# СХЕМЫ УПРАВЛЕНИЯ

# **УСТРОЙСТВАМИ ОТОБРАЖЕНИЯ ИНФОРМАЦИИ**

НПО "Интеграл" (г. Минск) разрабатывает и производит более 2000 типов интегральных микросхем и полупроводниковых приборов для телевидения и аудио, телекоммуникаций, силовой, автомобильной и промышленной электроники. Значительное место занимают микроконтроллеры и драйверы. Ниже приводятся характеристики микросхем для управления матричным ЖК-экраном и цифровым ЖКИ.

## КА1835ИД1 — МИКРОСХЕМА ДРАЙВЕРА МАТРИЧНЫХ ЖК-ЭКРАНОВ

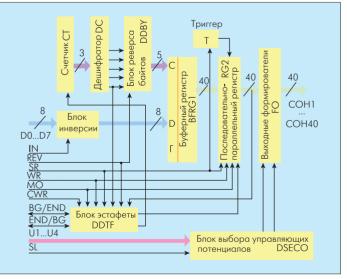

Предназначена для управления мультиплексным ЖКИ в устройствах отображения информации. Структурная схема приведена на рис.1, назначение выводов — в таблице 1.

#### Характеристики микросхемы

| Частота следования          |                             |

|-----------------------------|-----------------------------|

| импульсов тактовых сигналов | 400 кГц                     |

| Разрядность данных          | 8                           |

| Число режимов работы        | 2                           |

| Потребляемая мощность,      |                             |

| P <sub>CC</sub>             | не более 0,008 мВт          |

| Число выводов управления    | 40                          |

| Диапазон коммутируемых      |                             |

| напряжений                  | от U <sub>CC</sub> до -20 Е |

|                             |                             |

Микросхема состоит из следующих блоков: блока инверсии IN, буферного регистра BFRG1, счетчика СТ, дешифратора DC, блока реверса байтов DDBY, блока эстафеты DDTF, триггера Т, блока выбора управляющих потенциалов DSECO, последовательно-паралельного регистра RG2, выходных формирователей FO. Назначение блоков приведено в таблице 2.

Для управления столбцами и строками индикатора предусмотрено два режима работы микросхемы.

**Режим управления столбцами.** Функции: прием информации по байтовой шине; запись информации в буферный регистр; управление выходными формирователями; формирование сигнала управления.

А.Пархомчук

**Режим управления строками.** Функции: последовательный сдвиг в буферном регистре состояния возбужденной строки; управление выходными формирователями; формирование сигнала передачи управления.

Для управления индикаторами различной емкости количество микросхем, управляющих столбцами и строками индикатора, увеличивается. Допускается изменение порядка управления столбцами индикатора, что облегчает разработку плат и компоновку микросхем.

Выбор режима осуществляется по выходу МО. Низкий уровень напряжения на выходе МО соответствует режиму управления столбцами, высокий уровень — режиму управления строками.

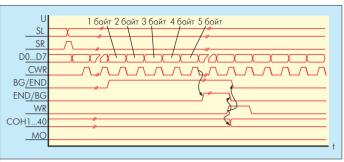

Работа микросхемы в режиме управления столбцами. Временная диаграмма работы микросхемы в этом режиме приведена на рис. 2. После общего сброса (по входу SR) по информационной магистрали (D0-D7) подается информация первых восьми столбцов индикатора. Информация может инвертироваться в блоке инверсии или проходить непосредственно во внутреннюю магистраль. Управление блоком инверсии осуществляется по входу IN.

После общего сброса счетчик устанавливается в состояние, обеспечивающее запись в буферный регистр первого

Рис. 1. Структурная схема ИС КА1835ИД1

Таблица 1. Назначение выводов микросхемы КА1835ИД1

| Выводы | Назначение                                             |  |  |  |  |  |

|--------|--------------------------------------------------------|--|--|--|--|--|

| 01-14  | Выводы управления ЖКИ СОН14-СОН1                       |  |  |  |  |  |

| 15     | Вход/выход передачи управленияBG/END                   |  |  |  |  |  |

| 16     | Вывод питания U (+5 B)                                 |  |  |  |  |  |

| 17     | Вход минимального потенциала управления ЖКИ U5 (-20 B) |  |  |  |  |  |

| 18     | Общий вывод 0V                                         |  |  |  |  |  |

| 19     | Вход выбора режима МО                                  |  |  |  |  |  |

| 20     | Вход строба записи CWR                                 |  |  |  |  |  |

| 21-28  | Вход информационный D0-D7                              |  |  |  |  |  |

| 29     | Вход перезаписи WR                                     |  |  |  |  |  |

| 30     | Вход реверса выходной информации REV                   |  |  |  |  |  |

| 31     | Вход "Общий сброс" SR                                  |  |  |  |  |  |

| 32     | Вход селектора напряжений SL                           |  |  |  |  |  |

| 33-36  | Входы потенциалов управления ЖКИ U1, U2, U3/ U4        |  |  |  |  |  |

| 37     | Вход инверсии IN                                       |  |  |  |  |  |

| 38     | Выход/вход передачи управления END/BG                  |  |  |  |  |  |

| 39-64  | Выходы управления ЖКИ СОН40-СОН15                      |  |  |  |  |  |

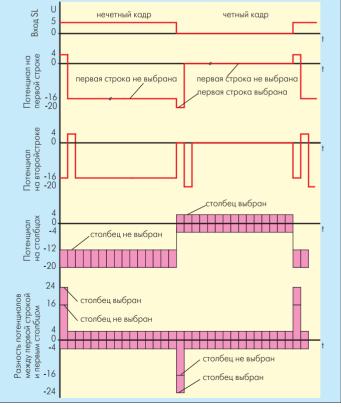

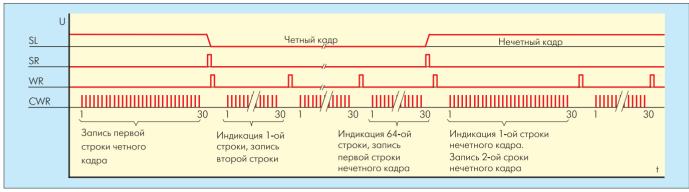

байта. Тактирование счетчика происходит по входу CWR. К приходу второго тактового сигнала на информационной магистрали (D0-D7) устанавливается информация по столбцам с 9 по 16 и так далее до полного заполнения всех пяти байтов буферного регистра, после чего по входу WR подается сигнал перезаписи информации в последовательно-параллельный регистр. На выходах COH1-COH40 устанавливаются потенциалы, соответствующие выбранному и невыбранному столбцу первой строки нечетного кадра (рис. 3). Управление четностью кадра происходит по входу SL.

Аналогично обеспечивается выбор элементов всех остальных строк индикатора. Затем весь процесс записи информации повторяется, однако на входе SL устанавливается низкий уровень напряжения, соответствующий четному кадру, что обеспечивает установление на выходах СОН1-СОН40 потенциалов, соответствующих четному кадру (см. рис. 3).

Таким образом, для работы схемы необходимо подавать две пары потенциалов (вход U1-U4), которые коммутируются на выходы формирователей в соответствии с таблицей 3.

Таблица 2. Назначение блоков драйвера КА1835ИД1

| Название блока                                    | Назначение                                                                                                                           |  |  |  |  |  |

|---------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

| Блок инверсии IN                                  | Прием информации из информационной магистрали в прямом или инверсном виде                                                            |  |  |  |  |  |

| Счетчик СТ совместно<br>с дешифратором DC         | Изменение порядка записи байтов в буферный регистр                                                                                   |  |  |  |  |  |

| Блок реверса<br>байтов DDBY                       | Изменение порядка записи байтов в буферный регистр                                                                                   |  |  |  |  |  |

| Блок эстафеты DDTF                                | Обеспечение последовательного подключения нескольких микросхем при управлении индикатором с количеством строк (столбцов) не более 40 |  |  |  |  |  |

| Триггер Т                                         | Запуск микросхемы в режиме управления строками индикатора                                                                            |  |  |  |  |  |

| Блок выбора управ-<br>ляющих потенциалов<br>DSECO | Подключение к выходным формирователям поочередно двух пар управляющих потенциалов                                                    |  |  |  |  |  |

| Последовательно-<br>параллельный<br>регистр RG2   | Хранение информации по столбцам и строкам индикатора и управление выходными формирователями                                          |  |  |  |  |  |

| Выходные<br>формирователи FO                      | Непосредственная подача управляющих потенциалов на элементы ЖКИ                                                                      |  |  |  |  |  |

Рис.2. Временная диаграмма работы микросхемы в режиме управления столбцами

Для обеспечения возможности использования микросхемы с индикатором, количество столбцов которого более сорока, предусмотрены два входа/выхода передачи управления BG/END и END/BG.

Управление режимом работы входов/выходов передачи управления происходит по входу REV. Один из входов/выходов передачи управления устанавливается в состояние "вход", а второй — в состояние "выход". При этом меняется порядок заполнения байтов буферного регистра (таблица 4). Запуск работы микросхемы происходит при подаче на вход передачи управления высокого уровня напряжения.

При работе в режиме управления столбцами после полного заполнения буферного регистра на выходе передачи управления появляется высокий уровень напряжения. При этом прохождение тактовых импульсов на счетчик блокируется и буферный регистр хранит записанную в нем информацию. Такая организация передачи управления позволяет подключать к магистрали данных одновременно несколько микро-

Рис. 3. Временная диаграмма работы матричного ЖК-экрана

Таблица 3. Таблица истинности outCOHi = F(outRG2)

| Значение уровня<br>напряжения<br>на входе SL | Информация,<br>записанная в последо-<br>вательно-параллельный<br>регистр RG2 | Потенциал, коммутируемый на соответствующий выход СОН1-СОН40 |  |

|----------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------------------------|--|

| 0                                            | 0                                                                            | $U_2$                                                        |  |

| U                                            | 1                                                                            | U <sub>1</sub>                                               |  |

| 4                                            | 0                                                                            | U <sub>3</sub>                                               |  |

| l l                                          | 1                                                                            | U <sub>4</sub>                                               |  |

схем, а поочередная передача в них информации обеспечивается подключением входов передачи управления к выходам передачи управления предыдущей микросхемы. Вход передачи управления первой микросхемы подключается непосредственно к источнику питания.

Таблица 4. Порядок заполнение буферного регистра

| Значение уровня            | Состояние в | хода/выхода | Порядок заполнения<br>байтов буферного<br>регистра BFRG1 |  |

|----------------------------|-------------|-------------|----------------------------------------------------------|--|

| напряжения на<br>входе REV | BG/END      | END/BG      |                                                          |  |

| 0                          | Вход        | Выход       | С 1 по 5                                                 |  |

| 1                          | Выход       | Вход        | С 5 по 1                                                 |  |

#### Работа микросхемы в режиме управления строками.

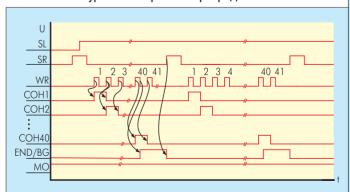

Временная диаграмма работы микросхемы в режиме управления строками приведена на рис. 4.

При работе микросхемы в режиме управления строками информация по информационной магистрали (D0-D7) игнорируется. Тактирование осуществляется по входу WR, а последовательно-параллельный регистр работает в последовательном режиме.

По первому тактовому импульсу в первый разряд последовательно-параллельного регистра из триггера переписывается "логическая единица", после чего триггер обнуляется. При поступлении следующих тактовых импульсов состояние "логической единицы" будет сдвигаться в последующие разряды последовательно-параллельного регистра, обеспечивая тем самым сканирование состояния выбранной строки на выводах СОН1-СОН40 (см. рис. 3). Управление четностью кадра и передачей управления происходит аналогично режиму работы по столбцам. При этом формирование высокого уровня на выходе передачи управления происходит при появлении сигнала высокого уровня в сороковом разряде.

<u>Рис.4. Временная диаграмма работы микросхемы</u> в режиме управления строками

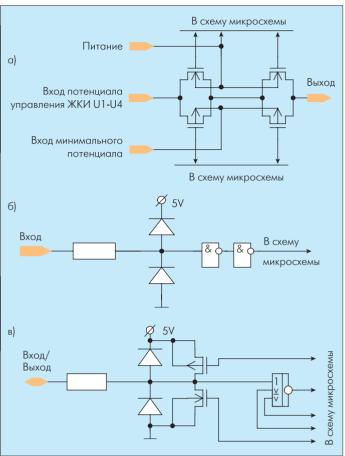

Рис.5. Принципиальная электрическая схема: а — выходного каскада для выводов 15, 19-32, 38; б — входного каскада для выводов 15, 19-32, 38; в — входного каскада для выводов 15, 19-32, 38

Начальная установка микросхемы производится подачей импульса положительной полярности на вход SR. При этом микросхема устанавливается в состояние, соответствующее готовности приема информации первой строки очередного кадра.

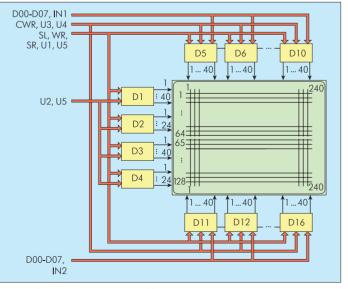

Схемы электрические принципиальные входных, выходных и входных-выходных каскадов микросхем приведены на рис. 5а,б,в. Схема применения микросхемы (240 столбцов и 128

Рис.6. Схема применения КА1835ИД1

Рис. 7. Временная диаграмма работы микросхемы при управлении ЖКИ (240 столбцов, 64 строки)

строк) приведена на рис. 6. Пример временной диаграммы работы микросхемы при управлении ЖКИ (240 столбцов и 64 строки) приведен на рис. 7.

Микросхема выполнена в корпусе 4233Ю.64-1.

# КР1820ВГ1 — КМОП-МИКРОСХЕМА ДРАЙВЕРА ЦИФРОВЫХ ЖКИ

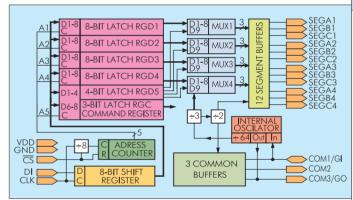

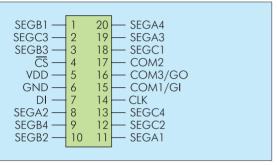

КР1820ВГ1 — драйвер ЖКИ с мультиплексом 1:3. Параметры микросхемы: напряжение питания 2,85—5,5 В, диапазон рабочих температур от —40 до 85°С. Имеет встроенный RC-генератор. Управление контрастом ЖКИ обеспечивается изменением напряжения питания VDD, которое определяет размах управляющих напряжений на ЖКИ. Назначение выводов КР1820ВГ1 приведено в таблице 5.

Рис.8. Структурная схема драйвера ЖКИ КР1820ВГ1

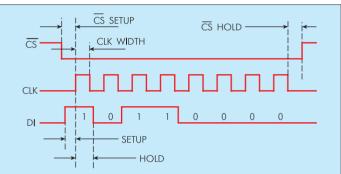

Данные по сигналу СLК (рис.8, 9, 10) загружаются в сдвиговый регистр. Частота передачи — до 500 кГц. После каждых 8 импульсов СLК счетчик адреса вырабатывает импульс перезаписи данных в один из 5 параллельных регистров. Ре-

Таблица 5. Назначение выводов КР1820ВГ1

| Вывод       | Назначение                                  |  |  |

|-------------|---------------------------------------------|--|--|

| CS          | Выбор кристалла                             |  |  |

| VDD         | Напряжение питания                          |  |  |

| GND         | Общий вывод                                 |  |  |

| DI          | Последовательный вход данных                |  |  |

| CLK         | Вход синхронизации данных                   |  |  |

| COM1/G1     | Выход управления строкой 1/вход генератора  |  |  |

| COM2        | Выход управления строкой 2                  |  |  |

| COM3/G0     | Выход управления строкой 3/выход генератора |  |  |

| SEGA1-SEGA4 | Выходы управления столбцами                 |  |  |

гистр RG5 организован как регистр данных RGD5 (Q1-Q4) и регистр команд RGC (Q6-Q8). Бит Q5 не используется. Бит Q8 используется для синхронизации двух и более микросхем при их совместной работе. Назначение битов регистра команд приведено в таблице 6.

Рис. 9. Временная диаграмма записи данных

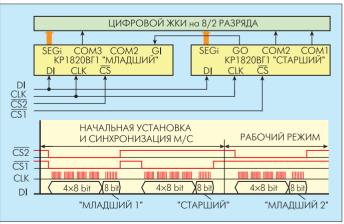

Две и более микросхемы могут использоваться совместно для управления 36×N сегментами ЖКИ. В этом случае выход генератора GO "старшей" ИС подключается к входам GI "младших" ИС. Для синхронизации работы нескольких микросхем в начале работы на все схемы подается команда "МЛАДШИЙ 1", затем на "старшую" микросхему — команда "СТАРШИЙ". В дальнейшем, при необходимости изменения информации в RGD5, на них подаются команды "МЛАД-ШИЙ 2" и "СТАРШИЙ". Если изменяются только младшие разряды ЖКИ, можно подавать число байт, соответствующее числу изменяющихся младших разрядов ЖКИ. После

Рис. 10. Совместная работа двух микросхем при каскадировании

Таблица 6. Система команд КР1820ВГ1

|    | Ком | анда |            |             | Выво    | ды ИС   |

|----|-----|------|------------|-------------|---------|---------|

| Q8 | Q7  | Q6   | <b>Q</b> 5 | Назначение  | COM3/G0 | COM1/G1 |

| 1  | 1   | 1    | 0          | "Младший 1" | COMO    | 01      |

| 0  | 1   | 1    | 0          | "Младший 2" |         | G1      |

| 0  | 0   | 1    | 1          | "Одиночный" | COM3    | COM1    |

| Х  | 1   | 0    | Х          | "Тестовый"  | G0      | G1      |

| 0  | 0   | 0    | 1          | "Старший"   | G0      | COM1    |

Таблица 7. Логика работы мультиплексоров MUXi

| Dyeni | SEG1-4 |   | СОМі |   | li | 0 |              |

|-------|--------|---|------|---|----|---|--------------|

| Входы | Α      | В | С    | 1 | 2  | 3 | Сегменты ЖКИ |

| D1    | Х      |   |      |   |    | Х | Hi           |

| D2    |        | Х |      |   | Х  |   | Gi           |

| D3    |        |   | Х    | Х |    |   | Fi           |

| D4    |        |   | Х    |   | Х  |   | Ei           |

| D5    |        | Х |      |   |    | Х | Di           |

| D6    | Х      |   |      |   | Х  |   | Ci           |

| D7    | х      |   |      | х |    |   | Bi           |

| D8    |        | Х |      | Х |    |   | Ai           |

| D9    |        |   | Х    |   |    | Х | Ki           |

завершения цикла записи уровень сигнала по входу CS должен быть установлен в "1".

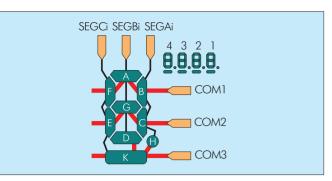

Благодаря аппаратной дешифрации бинарного кода в 7сегментный, КР1820ВГ1 оптимально подходит для управления цифровыми ЖКИ с разводкой сегментов, приведенной на рис. 11. Расположение выводов приведено на рис. 12. Отображение информации на сегментах ЖКИ происходит при помощи мультиплексоров-дешифраторов MUX1-MUX4, логика

Рис. 11. Типичная схема разводки одного разряда цифрового ЖКИ

Рис. 12. Расположение выводов

работы которых представлена в таблице 7. Сегмент К 4-го цифрового разряда ЖКИ на рис. 11 может использоваться в качестве единицы следующего разряда ЖКИ и разрядность ЖКИ увеличивается на 1/2 . Если же дешифрацию 7-сегментного кода осуществлять программно, то одна микросхема может управлять ЖК-индикаторами, содержащими 5 цифр, например: 88.888, 8888.8, 88888.

Микросхема выполнена в корпусах DIP-20 и SO-20.

### 17-я Международная ярмарка "Продуктроника 2007"

С 13 по 16 ноября 2007 года в Мюнхене состоится 17-я Международная ярмарка "Продуктроника 2007". Это — ведущая международная ярмарка в области изготовления электронной продукции. Она проводится с 1975 года один раз в два года в Мюнхене. По оценке устроителей ярмарки "Продуктроника 2007", в ней примут участие более 1500 экспонентов и примерно 44000 специалистов из всех стран мира.

Основные разделы выставки:

- Изготовление полупроводниковых приборов, дисплеев.

- Мир микро- и нанотехнологий.

- Технологии микроэлектроники.

- Микрообработка.

- Наноиндустрия.

- Обработка материалов (макрообработка).

- Технологии изготовления печатных плат и носителей для схемотехники.

- Контрольно-измерительная и испытательная техника, обеспечение качества.

- Логистика производства, технология расходования материалов.

Наибольшее внимание уделяется тем областям электроники, которые обладают высоким экономическим потенциалом и ориентированы на будущее — это органическая электроника, производство фотогальванической продукции, микро- и нанотехнологии, логистика производства и технология расходования

материалов, электронные службы производства, "зеленая" электроника, т.е. экологически чистые технологии производства и переработки отходов производства.

Подробные сведения о ярмарке можно получить в сетевом портале www.global-electronics.net, который является виртуальной платформой международной электронной промышленности и предлагает информацию об этой сфере производства, основные данные, сведения из области производственных инноваций и отчеты по претворенным в этой области достижениям, а также сведения, касающиеся ярмарок, которые проводятся в рамках глобальных электронных ярмарок.