## ДЕКОДЕР ЦИФРОВОГО ТЕЛЕВИЗИОННОГО СИГНАЛА ВЫСОКОЙ ЧЕТКОСТИ:

#### СИСТЕМА НА КРИСТАЛЛЕ

Бурное развитие цифровых телевизионных технологий требует высокопроизводительной элементной базы. Такие устройства должны быть достаточно мощными, чтобы поддерживать современные стандарты, и достаточно простыми в проектировании и производстве, чтобы составлять основу потребительских устройств средней ценовой категории. В системе на кристалле декодера цифрового телевизионного сигнала высокой четкости, разрабатываемой в ЗАО НТЦ "Модуль", используется как опыт крупнейших зарубежных компаний, лидеров отрасли, так и разработки отечественных специалистов. Таким образом, создается устройство, отвечающее запросам российского рынка цифровой телевизионной техники.

ЦИФРОВОЕ ТЕЛЕВИДЕНИЕ В РОССИИ

Важным этапом развития современного телевидения является переход к новым, цифровым форматам вещания.

Согласно государственной программе развития цифрового телевидения, к концу 2009 года принимать программы в новом цифровом формате вещания сможет не менее 80% населения России. Для этого, по приблизительным расчетам, потребуется порядка 30 млн. цифровых телевизионных приставок (из расчета – по одной приставке на семью). В конце 2011 года планируется окончательный переход на цифровое вещание. Ожидается, что значительно увеличится доля программ в формате телевидения высокой четкости (HDTV). Для окончательного же перехода к цифровому телевизионному вещанию потребуется не менее 45 млн. приставок. В данном случае речь идет, прежде всего, о недорогих приставках с минимальным набором интерфейсов и пользовательских функций, в которых отсутствует поддержка видео высокой четкости. С другой стороны, по мере развития цифрового телевидения все большим спросом будут пользоваться приставки с П.Шевченко, А.Шкуренко pshevch@module.ru

расширенным набором пользовательских функций, способные обрабатывать телевизионный сигнал высокой четкости.

Основой элементной базы любой современной цифровой телевизионной приставки является микросхема декодера цифрового телевизионного сигнала класса "система на кристалле". Система на кристалле (СнК) декодера цифрового телевизионного сигнала, разрабатываемая ЗАО НТЦ "Модуль", делает возможным создание различных конфигураций телевизионной приставки — от экономичной до класса hi-end.

#### НЕОБХОДИМЫЕ АЛГОРИТМЫ ОБРАБОТКИ ТВ-СИГНАЛА

Функции современных устройств приема цифрового ТВ (ЦТВ) весьма разнообразны. Не менее широк и набор задач, которые выполняет такое устройство, а соответственно, и система на кристалле, лежащая в его основе.

Задачи, которые должна решать система, можно разделить на несколько групп: прием и декодирование транспортного и программного потоков данных, поступающих от различных источников; декодирование и обработка аудио- и видеопотоков, дешифрация данных для обеспечения условного доступа.

Корректная работа цифровой телевизионной приставки невозможна без операционной системы реального времени. Такая система должна отвечать требованиям, которые накладывают особенности работы устройства, в том числе управление многочисленными интерфейсами ввода/вывода и создание удобного пользовательского интерфейса.

Планируется, что устройства на основе СнК будут принимать сигнал не только по телевизионным сетям наземного вещания, но и по спутниковым, кабельным и IP-сетям. Также возможно накопление информации на HDD, воспроизведение ее с HDD и DVD, в том числе с HD-DVD или Blu гау дисков, работа с системами условного доступа, выполнение различных дополнительных пользовательских функций, поддержка мультимедийных сервисов.

На данном этапе разработки СнК поддерживаются следующие алгоритмы кодирования видео: MPEG2 MP/HL, MPEG4-10/H.264 HP/L4.1 (Amd 2, апрель 2007), SMPTE 421M (VC-1) MP/HL, MPEG4-2 ASP/L5 (DivX, XviD), WMV9 MP/HL. Вместе

Таблица 1. Требования к производительности вычислительной системы декодирования видео

| Функции декодирования видео<br>(1080p/25fps) по стандарту Н.264 | Вычислительная<br>загрузка, % | МАС<br>на точку | ММАС*<br>на кадр | Чтение/запись,<br>Мбайт/с |

|-----------------------------------------------------------------|-------------------------------|-----------------|------------------|---------------------------|

| Дискретное косинусное преобразование (DCT)                      | 9                             | 20              | 43               | 270/150                   |

| Компенсация движения                                            | 16                            | 27              | 60               | 58/14                     |

| Деблочный фильтр                                                | 25                            | 12              | 27               | 50/11                     |

| САВАС декодирование                                             | 23                            | другое**        | другое**         | 1,5/1                     |

| Управление декодированием                                       | 27                            | другое**        | другое**         | менее 1                   |

| Всего                                                           | 100                           | 59              | 130              | 9500/4400                 |

<sup>\*</sup>MMAC – миллион умножений с накоплением (MAC). \*\*Данные функции, как правило, используют другие операции.

с этим существует возможность масштабирования и фильтрации видеоизображения, а также преобразования форматов в реальном времени. Это крайне актуально для телевизоров с большой диагональю или высокой разрешающей способностью (HD Ready и Full HD). В то же время, основными требованиями к цифровой телевизионной приставке бюджетного уровня являются поддержка стандартов декодирования видео MPEG-2 MP/ML и MPEG-4 MP/L3.0 — упрощенного подмножества перечисленных выше спецификаций.

Программный подход используется и для алгоритмов обработки аудиосигнала. СнК поддерживает как стандартные алгоритмы, которые применяются в домашних и переносных устройствах, такие как MPEG1/2 Layer I, II, MPEG1 Layer III (MP3) и MPEG4 AAC LC, так и новейшие алгоритмы обработки многоканального аудио, используемые в домашних кинотеатрах и технике класса hi-end: Dolby Digital / Dolby Digital + и DTS / DTS HD. В системе реализована программная поддержка постобработки и изменения формата аудио в реальном времени.

В табл.1 приведены требования к производительности вычислительной системы, поддерживающей декодирование потока видео высокой четкости с прогрессивной разверткой и частотой кадров 25fps (так называемый режим 1080р) по стандарту Н.264. Этот алгоритм наиболее требователен к вычислительным ресурсам системы. За одну секунду декодер должен производить до трех миллиардов операций умножения с накоплением (МАС), не говоря уже о других операциях и управлении системой. Пропускная способность памяти на чтение и запись должна составлять не менее 10 Гбайт/с и 5 Гбайт/с, соответственно. Необходимая производительность вычислительной системы достигается за счет применения высокопроизводительных вычислительных устройств и развитой иерархической подсистемы памяти.

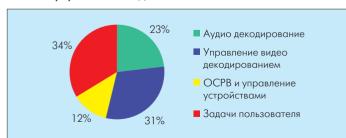

<u>Рис. 1. Распределение загрузки центрального процессора</u> <u>ARM 1 176JZF-S</u>

#### РЕАЛИЗАЦИЯ АЛГОРИТМОВ В СИСТЕМЕ ПРИЕМА ТВ-СИГНАЛА

Разработка микросхем уровня системы на кристалле — процесс далеко не быстрый. Часто достаточно сложно точно спрогнозировать, какие функции будут пользоваться спросом к моменту появления микросхемы и устройств на ее основе на рынке. Телекоммуникационные стандарты постоянно развиваются, и крайне важно своевременно реагировать на изменения.

Быстро решить задачи модификации функционального состава устройства можно только на программном уровне. Главным преимуществом программного подхода к декодированию аудио- и видеосигналов является гибкость системы, в рамках которой на одной и той же аппаратуре реализуются несколько близких по функциональности алгоритмов, а также возможность изменений в уже законченной системе и поддержка самых новых модификаций стандартов, в том числе и после выхода системы.

Говоря о методах реализации алгоритмов, нужно подчеркнуть, что большинство из них реализуется с использованием как непосредственно ядра центрального процессора, так и сопроцессорных вычислительных устройств. Задачи обработки и декодирования аудиосигналов, работа операционной системы реального времени, включая управление различными периферийными устройствами и поддержку пользовательского интерфейса, выполняются непосредственно на ядре ЦП (рис.1). Основные вычисления, связанные с декодированием и обработкой видеосигналов, производятся сопроцессорными устройствами. Такой подход к вычислениям требует высокопроизводительного центрального процессора.

#### СИСТЕМА ДЛЯ ПРИЕМА ЦИФРОВОГО ТВ

Основой устройства является микросхема класса "система на кристалле", которая обеспечивает исполнение большинства функций приемника. Стоимость разработки таких микросхем весьма высока, поэтому имеет смысл выпускать микросхемы одного типа с максимумом поддерживаемых функций, а не разрабатывать различные типов кристаллов для разных приложений. Таким образом, разнообразные модификации конечных устройств закладываются уже на этапе разработки, тем самым достигается оптимальное соотношение цены и качества для различных категорий пользователей.

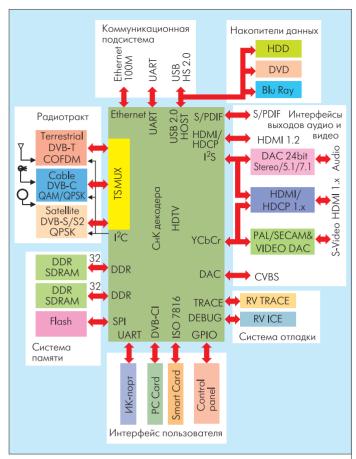

Рис.2. Схема устройства приема ЦТВ

Подобное устройство приема ЦТВ может быть изготовлено с использованием описываемой системы на кристалле (рис.2). Такая конфигурация отвечает всем требованиям к современным медиацентрам, созданным на базе цифровых телевизионных приставок.

Приемная часть радиотракта устройства состоит из тюнеров для приема наземного (DVB-T), кабельного (DVB-C) или спутникового (DVB-S/S2) телевизионного сигнала, а также из блоков демодуляции данных сигналов: COFDM, QAM/QPSK и QPSK, соответственно. Обработку радиосигнала производят специализированные СБИС, их выбирают в зависимости от типа принимаемого телевизионного сигнала. В микросхему декодера из данного блока сигнал поступает в формате транспортного потока. Управляются демодуляторы по универсальной шине I<sup>2</sup>C центральным процессором системы.

Коммуникационная подсистема состоит из интерфейсов Ethernet, UART и USB 2.0. Интегрированный контроллер Ethernet позволяет использовать микросхему декодера HDTV для приема цифрового телевизионного сигнала по IP-сетям. Кроме того, с помощью интерфейсов Ethernet и UART можно организовать обратный канал для поддержки многочисленных мультимедийных сервисов. Система содержит высокоскоростной интерфейс USB Host High Speed версии 2.0. Через него можно подключать системы для хранения и структурирования данных и дисковые приводы для воспроизведения или записи выбранного медиаконтента.

Звук на выходе аудиоподсистемы передается с помощью цифровых интерфейсов I<sup>2</sup>S и S/PDIF с поддержкой до восьми каналов звука. Для получения аналогового сигнала необходимого качества применяют внешние ЦАП с разрядностью до 24 разрядов на канал. Обеспечивается поддержка от одного канала звука (моно) до восьми каналов (7.1).

Блок видеоинтерфейсов допускает выдачу как аналогового композитного видеосигнала стандартного разрешения, упрощая подачу сигнала на старые аналоговые телевизионные приемники, так и цифрового видеосигнала стандартной и высокой четкости. Кроме того, видео- и аудиосигналы из микросхемы декодера можно выдавать с помощью новейшего цифрового интерфейса HDMI с поддержкой системы защиты информации HDCP. Также предусмотрена организация второго канала HDMI с применением внешних интерфейсных микросхем.

Для дистанционного управления устройством предназначен инфракрасный порт (IrDA) с интерфейсом UART. Для управления устройством через аппаратный интерфейс пользователя служат порты общего назначения GPIO.

Система на кристалле поддерживает функции условного доступа. Можно задействовать как встроенный универсальный блок условного доступа, используя внешнюю пользовательскую карту Smart Card для хранения ключевой информации, так и внешние модули условного доступа (CAM) по интерфейсу DVB-CI.

Для отладки и трассировки работы системы имеется стандартный инструментарий, предоставляемый фирмой ARM, — RV ICE и RV Trace. соответственно.

Наличие двух внешних 32-разрядных интерфейсов с динамической памятью типа DDR обусловлено требованиями алгоритма H.264 к высокой пропускной способности памяти. Необходимое для работы системы программное обеспечение хранится во внешней flash-памяти. ПО аппаратно защищено от несанкционированной модификации.

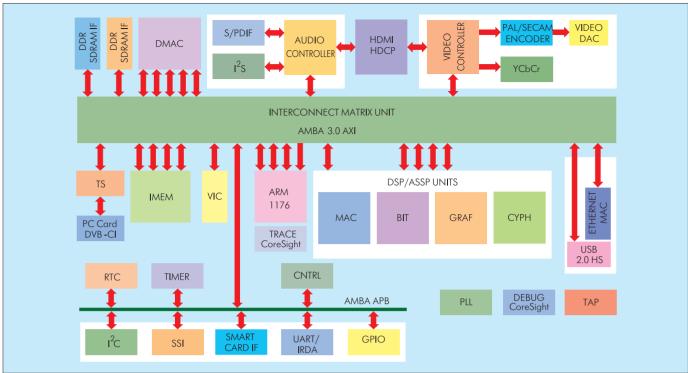

#### СИСТЕМА НА КРИСТАЛЛЕ

В основе системы на кристалле декодирования и обработки аудио- и видеоинформации для устройств цифрового телевидения лежит центральный процессор ARM1176JZF-S (рис.3). Обмен данными в системе производится по шинам данных в соответствии со спецификацией AMBA 3.0.

Основными преимуществами ядра ARM1176JZF-S являются: новая, более производительная архитектура версии v6; наличие интегрированных в ядро кэшей команд и данных, а также сверхоперативной памяти команд и данных TCM (Tight Coupled Memory); поддержка новейшего формата шины — AMBA 3.0 AXI; наличие сопроцессора для работы с данными в формате с плавающей точкой. Ядро поддерживает работу с четырьмя шинами: тремя 64-разрядными шинами для чтения команд, передачи данных и работы с памятью TCM в режиме

**Рис.3. Структура системы на кристалле для HDTV**

прямого доступа к памяти и 32-разрядной шиной для обмена данными с периферийными устройствами.

Такое обилие шин позволяет достичь необходимой пропускной способности системы. Кроме того, спецификация AMBA AXI обеспечивает два независимых канала для чтения и записи данных. Таким образом, пропускная способность еще больше увеличивается и при помощи одной шины формата AXI создается полноценный канал прямого доступа в память.

За взаимодействие между отдельными устройствами системы отвечает настраиваемая матрица коммутации (interconnect matrix unit). Она предусматривает возможность одновременной передачи данных от нескольких источников к нескольким приемникам. В частности, используется пакетный режим передачи данных и одновременная передача нескольких пакетов данных с чередованием данных из разных пакетов от разных источников.

Многоканальный контроллер прямого доступа в память (DMAC) обеспечивает загрузку данных в требуемые области памяти. Система имеет иерархическую многоуровневую систему памяти для максимальной загрузки данными всех ее вычислительных устройств.

Система памяти содержит четыре банка внутренней памяти микросхемы IMEM, два интерфейса с внешней динамической памятью типа DDR, интерфейсы с внешней flash-памятью. Такая конфигурация в сочетании с кэшем команд и данных, памятью ТСМ процессора ARM и векторными регистрами блока декодирования видео обеспечивает иерархическую систему памяти с пропускной способностью, необходимой для решения всех возложенных на систему задач.

Система содержит демультиплексор транспортного потока TS, который производит разбор транспортного потока от нескольких источников, и интегрированный в него блок системы условного доступа, который поддерживает основные алгоритмы условного доступа, в том числе CSA, DES, 3DES и отечественный ГОСТ. Устройство также предусматривает подключение внешних модулей условного доступа по интерфейсу PC Card/DVB-CI и работу со смарт-картами.

Многочисленные коммуникационные интерфейсы и интерфейсы вывода аудио- и видеоданных позволяют строить на базе микросхемы линейки устройств с различными потребительскими свойствами и минимальным количеством дополнительных микросхем.

Микросхема имеет развитую систему прерываний, которой управляет векторный контроллер прерываний VIC. Доступ к регистрам периферийных устройств (CNTRL), размещенных в общем адресном пространстве системы, производится по периферийной шине процессора.

Система на кристалле основана на готовых функциональных блоках. Это дает возможность максимально унифицировать систему и значительно упрощает адаптацию необходимого программного обеспечения. Собственно говоря, большая часть ПО для процессоров ARM из имеющегося на рынке способна функционировать в системе без внесения какихлибо изменений либо с минимальной адаптацией.

Большинство лицензируемых IP-блоков, входящих в состав системы на кристалле, предоставляется компанией Fujitsu. Это основной процессор ARM1176JZF-S, блоки, составляющие инфраструктуру шин данных формата AMBA 3.0, аналоговые блоки ЦАП (12 разрядов, 54 млн. выборок в се-

Таблица 2. Технические параметры микросхемы

| Технология изготовления, нм      | КМОП 90     |  |  |

|----------------------------------|-------------|--|--|

| Размер кристалла, мм             | 6,4×6,4     |  |  |

| Напряжение питания, В            | 1,2/2,5/3,3 |  |  |

| Типовая мощность потребления, Вт | <2          |  |  |

| Частота ядра, МГц                | 324         |  |  |

| Частота внутренней шины, МГц     | 162         |  |  |

| Объем внутренней памяти, Мбит    | 10          |  |  |

| Тип корпуса                      | BGA484      |  |  |

| Число функциональных выводов     | 332         |  |  |

кунду) и PLL, интерфейсные периферийные блоки (контроллер USB 2.0 HS Host, видеоинтерфейс HDMI 1.2 Тх с поддержкой защищенного режима передачи HDCP, контроллер Ethernet MAC 100 M/1G, интерфейсы последовательных портов I<sup>2</sup>C, SSI, UART).

Специализированный блок, предназначенный для декодирования видеосигнала (DSP/ASSP), — собственная разработка ЗАО НТЦ "Модуль".

Трассировка и отладка микросхемы существенно упрощена благодаря технологии CoreSight фирмы ARM. Отладочная программа имеет доступ к внутренним ресурсам процессора через ТАР-контроллер.

#### БЛОК ДЕКОДИРОВАНИЯ ВИДЕОСИГНАЛОВ

Основным вычислительным блоком микросхемы декодера цифрового телевизионного сигнала высокой четкости, помимо процессора ARM, является блок декодирования видеосигналов. Устройство предназначено для обработки потоков видеоданных и представляет собой набор устройств цифровой обработки сигналов, созданных на основе технологии NeuroMatrix. Эта технология разработана в ЗАО НТЦ "Модуль" и уже опробована в нескольких поколениях цифровых сигнальных процессоров NeuroMatrix. Устройства могут выполнять матричные операции над матрицами и векторами данных с переменной разрядностью операндов. Загрузка и выгрузка данных реализуется специализированными блоками прямого доступа в память на фоне работы основного процессора. Устройство имеет собственную подсистему памяти для хранения промежуточных результатов декодирования и набор векторных регистров. Блок декодирования видео содержит интерфейсы согласно спецификации AMBA 3.0 AXI и, соответственно, может быть использован в любой системе на основе процессоров ARM. Блок декодирования управляется программно через центральный процессор системы.

Блок декодирования видео структурно разделен на несколько функциональных устройств, которые выполняют задачи отдельных составляющих алгоритма (см. рис.3): дискретное косинусное преобразование (блок MAC), компенсацию движения и деблочную фильтрацию (блок GRAF), декодирование битовых последовательностей (блок BIT), битовые перестановки (блок СҮРН). Обмен данными производится как между отдельными функциональными устройствами, так и с остальной системой.

#### ХАРАКТЕРИСТИКИ МИКРОСХЕМЫ

В табл.2 приведены технические параметры кристалла. Микросхема изготавливается по технологии КМОП фирмы Fujitsu с технологическими нормами 90 нм. Столь прогрессивная технология позволяет получить высокопроизводительную систему на кристалле при достаточно скромных технологических параметрах. Так, размер кристалла составляет всего около 40 мм², а типовое энергопотребление СБИС — менее 2 Вт при частоте работы ядра 324 МГц. Микросхема заключена в пластиковый ВGA корпус с 484 выводами, из них 332 вывода — функциональные. Относительно малое число внешних выводов достигается за счет частичного мультиплексирования интерфейсов микросхемы по функциональному признаку. Напряжение питания составляет 3,3 В для внешних интерфейсов, 2,5 В для интерфейса с памятью DDR и 1,2 В для питания ядра микросхемы.

Главным отличием описываемой СБИС от существующих на рынке аналогов является программная поддержка всех современных алгоритмов для декодирования видео высокой четкости. Это позволяет учитывать современные тенденции в телекоммуникационной сфере, обеспечивает соответствие всем современным стандартам и простоту модификации в будущем. К преимуществам относится также масштабируемая архитектура. В целом микросхема — законченное программно-аппаратное решение, сохранившее при высокой производительности компактность и низкую стоимость.

Характеристики микросхемы позволяют ей занять достойное место на отечественном рынке, в различных областях применения — от цифровых телевизионных приставок бюджетного уровня до многофункциональных мультимедийных центров.

# НОВЫЕ КНИГИ

### ИЗДАТЕЛЬСТВА "ТЕХНОСФЕРА"

Динамика радиоэлектроники/ Под общ. ред. Ю.И. Борисова. – М.: Техносфера, 2007. – 400с.+ цв. Вклейка, ISBN 978-5-94836-142-0, цена 275 руб.

Издание осуществлено при поддержке Управления радиоэлектронной промышленности и систем управления Роспрома

Книга содержит материал о динамике развития радиоэлектроники – одной из наиболее важных составляющих научно-технического прогресса общества, во многом определяющей его социальные и оборонные возможности. Материалы книги подготовлены группой ученых и инженеров, непосредственно принимавших участие в исследованиях, разработках, испытаниях и применении изделий электронной техники и радиотехнической аппаратуры.

Для читателей, интересующихся созданием и развитием отечественной радиоэлектроники и условиями, в которых проходило ее становление в СССР.

#### Как заказать наши книги?

По почте: **125319 Москва, а/я 594** По тел./факсу: **(495) 956-3346, 234-0110**

E-mail: knigi@technosphera.ru; sales@technosphera.ru