Семь лет назад мы писали о первом отечественном DSP-процессоре, изготовленном российской фирмой НТЦ "Модуль", — NeuroMatrix NM6403 (Л1879ВМ1) [1]. Полгода назад компания объявила о выпуске следующего процессора семейства NeuroMatrix — 1879ВМ2 (NM6404). Сегодня в ближайших планах компании — процессор третьего поколения 1879ВМ4.

Научно-техническим центром "Модуль" разработано семейство процессоров цифровой обработки сигналов (DSP) NeuroMatrix, включающее СБИС Л1879ВМ1 (NM6403) и 1879ВМ2 (NM6404), а в перспективе — процессор третьего поколения 1879ВМ4 (NM6405). Особенность данного семейства — оригинальная запатентованная векторно-матричная архитектура, обеспечивающая высокое соотношение производительности к цене устройств.

Процессоры семейства NeuroMatrix — это высокопроизводительные вычислительные устройства RISC-архитектуры с элементами VLIW (Very Long Instruction Word — очень длинное командное слово), SIMD (Single Instruction Multiple Data) и суперскаляра. Они аппаратно поддерживают матричные и векторные операции над 64-разрядными векторами, в которых упакованы данные (в дополнительном коде с фиксированной точкой). Каждый вектор может состоять из нескольких элементов произвольной разрядности, но суммарная разрядность всех элементов вектора должна составлять 64 разряда.

### ПРОЦЕССОР Л1879ВМ1

Процессор Л1879ВМ1 выпускается уже более семи лет. Он изготавливается по КМОП-технологии с технологическими нормами 0,5 мкм фирмой Samsung. Процессор работает на частотах до 40 МГц в диапазоне температур от -40...+85°С и напряжений от 3,0—3,6 В. В 1999 году лицензия на использование микропроцессорного ядра этого процессора была приобретена фирмой Fujitsu. Л1879ВМ1 поддерживает работу с 32-разрядными скалярными данными и векторными данными программируемой разрядности от 1 до 64, упакованными в 64-разрядные блоки данных.

П.Виксне

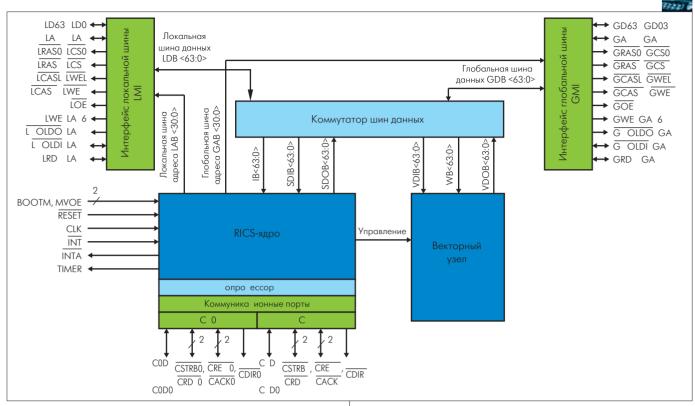

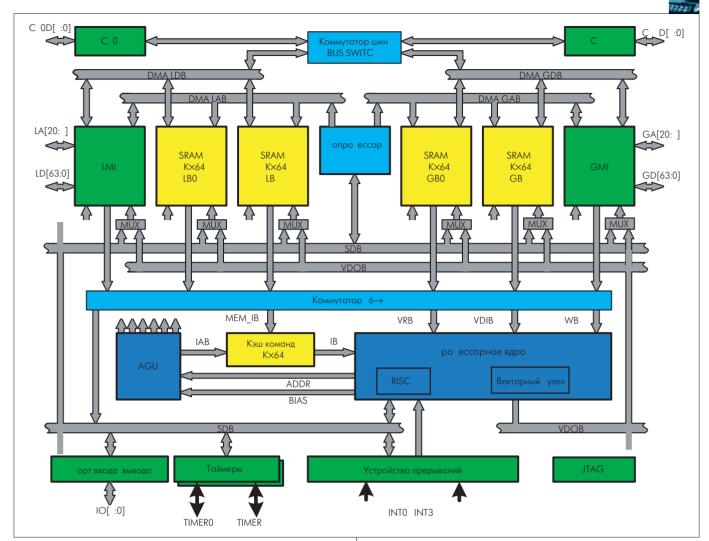

В состав процессора входят (рис.1):

Вхол Ц

- 32-разрядный RISC-процессор с 5-ступенчатым конвейером, выполняющий скалярные арифметические, логические и сдвиговые операции над 32-разрядными данными, а также управляющий выполнением программ. RISC-процессор использует оригинальную систему команд. Команды — 32- и 64-разрядные, одна команда обычно задает две операции: арифметическую и ввода-вывода;

- *векторный узел*, выполняющий арифметические и логические операции над 64-разрядными векторами данных;

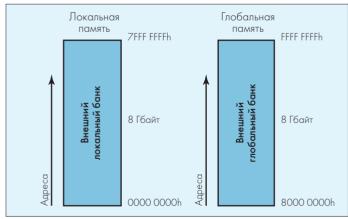

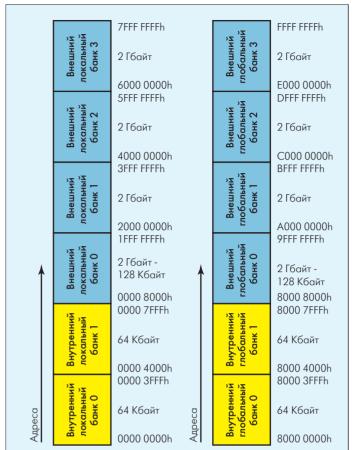

- два идентичных 64-разрядных интерфейса с внешней памятью локальной (LMI) и глобальной (GMI). Каждый интерфейс позволяет работать с двумя банками внешней памяти типа SRAM/DRAM общим объемом 8 Гбайт (2<sup>31</sup> 32-разрядных ячеек). Таким образом, доступное адресное пространство составляет 16 Гбайт (рис.2). Обмен происходит 32- и 64-разрядными данными. Младший разряд адреса используется только при обмене 32-разрядными данными. Интерфейсы LMI и GMI поддерживают режим совместного использования общей памяти с другим процессором;

- два байтовых коммуникационных порта ввода/вывода для межпроцессорного обмена, аппаратно совместимые с портами DSP TMS320C4x фирмы Texas Instruments (CP0 и CP1);

# Представляем автора статьи

ВИКСНЕ Павел Евгеньевич. Окончил факультет информатики и управления МВТУ им. Баумана. Начальник сектора ЗАО НТЦ "Модуль", автор 30 публикаций.

E-mail: pvixne@module.ru

Рис. 1. Структурная схема процессора Л1879ВМ1

- сопроцессор прямого доступа к памяти (ПДП), осуществляющий обмен 64-разрядными данными между памятью и портами;

- коммутатор шин данных, позволяющий динамически связать одну из внешних шин с одной из шести внутренних: с шиной команд IB, входных/выходных скалярных данных SDIB/SDOB, входных/выходных векторных данных VDIB/VDOB, а также с входной шиной весов WB. Все шины « 64-разрядные.

Рис. 2. Карта памяти процессора Л1879ВМ1

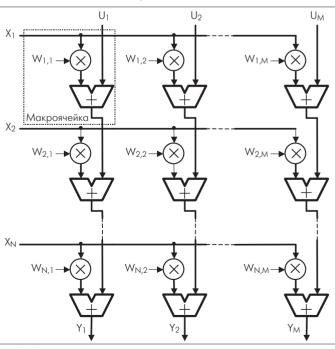

Архитектура векторного узла NeuroMatrix дает уникальную возможность варьировать между производительностью и точностью вычислений для базовой процедуры — операции умножения с накоплением (MAC):

$$Y_n = U_n + \sum_{n=1}^{M} X_n \times W_{i,n} .$$

Векторный узел содержит операционное устройство регулярной структуры, похожее на матричный умножитель (рис.3). Оно состоит из ячеек, содержащих триггер и некоторую комбинационную логику. Пользователь может поделить матрицу ячеек на макроячейки, используя два программно доступных 64-разрядных конфигурационных регистра. Эти регистры задают границы между строками и столбцами макроячеек таким образом, что каждая макроячейка выполняет операцию умножения элемента входного вектора  $X_i$  на заранее загруженный весовой коэффициент  $W_{ij}$ , а затем выходные значения мак-

Рис.3. Операционное устройство векторного узла

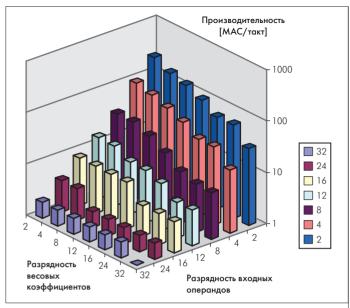

<u>Рис.4. Зависимость производительности от разрядности входных операндов и весов</u>

роячеек в одном столбце суммируются. Таким образом, за один такт в каждом столбце независимо вычисляется свой результат.

Число МАС, выполняемых за один такт, зависит от разрядности операндов (размеров макроячеек) и изменяется от 2 (32-разрядные данные) до 224 (2-разрядные данные) МАС. Соответственно, пиковая производительность при 2-разрядных данных составляет 8,96 млрд МАС (GMAC) на частоте 40 МГц. Если повысить точность, используя 32-разрядные операнды с получением 64-разрядного результата, производительность снизится до 80 ММАС.

Рис.5. Пример работы векторного узла с 8-разрядными входными данными и весами

Конфигурация векторного узла может меняться динамически в процессе вычислений. Например, начав вычисления с небольшой разрядностью, но с большой производительностью, по мере накопления промежуточных результатов (и увеличения их разрядности) можно перейти к обработке данных большей разрядности за счет снижения быстродействия (рис.4). Например, при работе с 8-разрядными входными данными ( $X_i$ ) и весами ( $W_{ij}$ ) (рис.5) достигается пиковая производительность в 960 ММАС (за один такт в 25 нс выполняются 24 операции МАС с получением 21-разрядных результатов).

Операционное устройство достигает еще большей производительности — 40,96 GMOPS при выполнении булевого умножения, когда разрядность входных операндов и весов равна 1. Интересно отметить, что при использовании 1-разрядных коэффициентов векторный узел превращается в мощный коммутатор, когда перестановка битов в 64-разрядном входном операнде происходит за один такт.

Новые весовые коэффициенты загружаются в операционное устройство за 32 такта. Причем их предварительно можно записать в теневую матрицу, а затем за один такт переписать в рабочую.

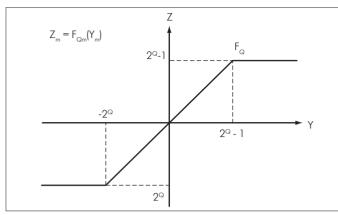

Для предотвращения переполнения регистров результата аппаратно реализована функция насыщения (рис.6), выполняемая одновременно над всеми элементами 64-разрядных векторов упакованных данных. Границы насыщения задаются с помощью программно доступных регистров управления этой функцией.

Система команд процессора делится на две основные группы: скалярные и векторные команды. Скалярные команды — это обычные RISC-команды, в том числе условные переходы, переходы к подпрограмме и возвраты из подпрограмм и из прерывания. Процессор использует 32-разрядные константы, загружаемые в регистры или используемые для задания адреса или смещения при обращении к памяти. Векторные команды содержат специальное поле, задающее число повторов выполнения данной команды (от 1 до 32). Это позволяет аппаратно поддержать организацию коротких циклов и значительно увеличить плотность кода.

Конвейер Л1879ВМ1 состоит из нескольких подконвейеров. Любая скалярная или векторная команда в заданный момент времени занимает один или несколько подконвейеров. Очередная команда (но не более одной за такт) может быть запущена, только если свободны необходимые подконвейеры. Одновременно выполнются до четырех векторных команд (включая два доступа в память) и одна скалярная команды.

Синхронизируются подконвейеры с помощью механизма блокировок. Если команда требует некоторый ресурс, который в данный момент занят, формируется блокировка, и выполнение команды приостанавливается. Принадлежащие команде подконвейеры блокируются, остальные же могут продолжать

Рис.б. Функция насыщения

свою работу. Таким образом, несмотря на последовательный запуск команды в конвейер, использование векторных команд позволяет достичь производительности суперскалярных процессоров. Также поддерживается завершение команд не в том порядке, в котором они выбирались из памяти. Вместе с тем достигается высокий уровень загрузки аппаратуры на кристалле, поскольку скалярные и векторные команды используют единый конвейер и одни и те же исполнительные устройства. При этом объем управляющей логики невелик – менее 5% от 115 тыс. используемых вентилей на кристалле.

Эффективность заложенных в NeuroMatrix архитектурных решений демонстрирует сравнение производительности DSP Л1879ВМ1 и TMS320C80 (Texas Instruments) на задачах вычисления фильтра-свертки (табл.1) [18]. Важно отметить, что число циклов для Л1879ВМ1 с увеличением размера маски свертки растет линейно. Более подробно с оценкой производительности Л1879ВМ1 на различных задачах можно познакомиться в работах [19-25].

## ПРОЦЕССОР 1879ВМ2

Процессор 1879ВМ2 уже разработан и запущен в серийное производство. Он изготавливается по более современной 0,25-мкм КМОП-технологии фирмы Fujitsu. От своего предшественника 1879ВМ2 отличается вдвое большей производительностью и тактовой частотой (до 80 МГц), а также встроенной памяти объемом 2 Мбит. Рабочий диапазон температур – от -40 до +85°C, напряжение питания ядра процессора -2,3-2,7 В, периферии - 3,0-3,6 В.

По структурной организации и программным моделям отдельных узлов 1879ВМ2 практически идентичен процессору Л1879ВМ1 (рис.7). Это позволяет без изменений использовать в новом процессоре системное и прикладное программ-

Таблица 1. Вычисление сверток

| Свертка | Л1879ВМ1<br>Циклы/Пиксель | TMS320C80<br>Циклы/Пиксель |  |

|---------|---------------------------|----------------------------|--|

| 3x3     | 1,8                       | 2,1                        |  |

| 5x5     | 2,6                       | 7,3                        |  |

| 7x7     | 4,3                       | Нет данных                 |  |

| 9x9     | 5,7                       | Нет данных                 |  |

### ПРОГРАММА ВЫЧИСЛЕНИЯ ФИЛЬТРА-СВЕРТКИ 3х3:

nb1 = 80008000h: / Первые две команды делят операционное устройство / sb = 02020202h: / на 4 колонки по 16 разрядов и 8 строк по 8 разрядов/

<1>

rep 24 wfifo = [ar6++], ftw; / Загрузка весов в теневую матрицу// Переписывание теневой матрицы WTW REG(gr2); в рабочую/

rep 32 data = [ar0++],ftw with vsum, data, 0;

/ Вычисление промежуточного результата свертки с использованием трех элементов первой строки

маски 3х3/

WTW REG(gr2); / переписывает новые веса из теневой

матрицы в рабочую/

rep 32 data = [ar1++], ftw with vsum, data, afifo;

/Вычисляется промежуточный результат свертки с использованием трех

элементов второй строки маски 3х3 с прибавлением результата

пятой команды/

WTW REG(gr2); /Снова переписываются веса из тене-

вой матрицы в рабочую/

rep 32 data = [ar2++]with vsum, data, afifo;

/вычисляется промежуточный результат свертки с использованием трех элементов третьей строки маски

3х3 с прибавлением результата седьмой команды/

if > delayed goto L with gr7--;

/Отложенный переход на начало цикла. "Отложенный переход" означает, что следующие две команды будут

выполнены прежде, чем произойдет

сам переход/

ar6 = ar6: rep 32 [ar4++gr4] = afifo; /Восстановление памяти весов/ /Запись результатов вычислений

в память/

ное обеспечение (ПО), созданное для Л1879ВМ1. Рассмотрим основные архитектурные и структурные особенности 1879ВМ2, отличающие его от своего предшественника.

СБИС 1879ВМ2 содержит встроенную быстродействующую статическую оперативную память (SRAM) общим объемом 2 Мбит. Это позволяет существенно сократить объем внешней памяти или вообще исключить ее. а также использовать более дешевые медленные СБИС памяти. Тем самым резко снижается стоимость изделий на базе процессора 1879BM2.

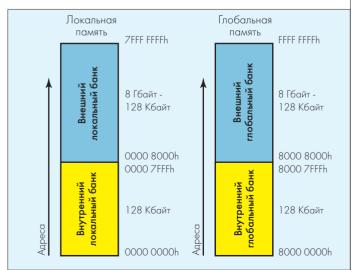

Внутренняя память состоит из двух одинаковых блоков (банков) однопортовой синхронной SRAM с организацией 16K×64 бит и может использоваться для оперативного хранения 32- и 64-разрядных данных, коэффициентов и команд. Любой цикл обращения к внутренней памяти выполняется за один процессорный такт. В каждом такте происходит до двух обращений к внутренней или внешней памяти. Один банк вну-

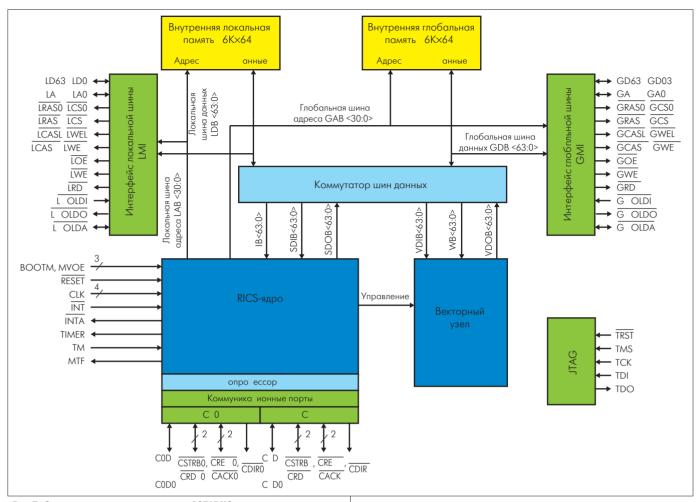

Рис.7. Структурная схема процессора 1879ВМ2

тренней памяти расположен в адресном пространстве локальной шины, второй — в адресном пространстве глобальной шины (рис.8). Банки внутренней памяти не доступны извне. Предусмотрено аппаратное тестирование внутренней памяти.

В 1879ВМ2 добавлен JTAG-порт, позволяющий существенно упростить процедуры тестирования аппаратных средств и отладки прикладного ПО.

В отличие от предшественника, такие функции, как арбитраж шины, сигнал готовности, признак цикла (запись/чтение)

Рис. 8. Карта памяти процессора 1879ВМ2

для динамического ОЗУ реализованы в интерфейсе с внешней памятью посредством отдельных соответствующих выводов (т.е. для этого уже не используются 16—19 разряды адресной шины, как в Л1879ВМ1). Кроме того, выводы сигналов готовности внешнего устройства (GRDY и LRDY) использовались в Л1879ВМ1 как таковые только в однопроцессорной конфигурации шины, для многопроцессорной конфигурации с их помощью разрешался захват шины другим процессором. Теперь же они выполняют свою основную функцию независимо от конфигурации шины, а захват шины реализуется посредством двух новых выводов GHOLDA и RHOLDA.

Коммуникационные порты в 1879ВМ2 остались прежними. Снимаются все ограничения на использование коммуникационного порта СР1, введеные для Л1879ВМ1 из-за аппаратной ошибки. Наличие у 1879ВМ2 внутренней памяти позволяет гарантировано принимать/передавать пакеты размером до 16К 64-разрядных слов. Но уровень сигналов в 1879ВМ2 — 3 В, и он не способен принимать 5-В сигналы. В результате процессор может обмениваться данными непосредственно через коммуникационный порт с Л1879ВМ1, но не с ТМS320С4х, питание которого 5 В.

В 1879ВМ2 добавлены четыре входа внешних прерываний вместо одного, при этом таблица адрес-векторов прерываний осталась неизменной. Это означает, что любому из четырех

Рис. 9. Структурная схема процессора 1879ВМ4

внешних прерываний соответствует один адрес-вектор. Какое именно внешнее прерывание (или несколько внешних прерываний) обрабатывается в данный момент времени, программист может определить с помощью битов 29—26 регистра INTR, где теперь фиксируется состояние всех входов внешних прерываний при детектировании обобщенного запроса на внешние прерывания (т.е. при появлении низкого уровня на любом из входов внешних прерываний при условии, что выход подтверждения внешнего прерывания INTA находится в пассивном состоянии). При инициализации процессора по внешнему прерыванию можно использовать любой из четырех входов внешних прерываний.

## ПРОЦЕССОР 1879ВМ4

Процессор 1879ВМ4 — это DSP третьего поколения, дальнейшее развитие семейства NeuroMatrix. Его запуск планируется в 2006 году. Он будет изготовлен по той же технологии, что и 1879ВМ2 (и с теми же электрическими и климатическими параметрами), но за счет более глубокого конвейера тактовая частота достигнет 150 МГц. Сохраняя программную совместимость с предшественниками и их основные архитектурные особенности, процессор 1879ВМ4 имеет процессорное ядро

усовершенствованной архитектуры, ряд отличий которой позволяет увеличить производительность при той же тактовой частоте.

По структурной организации и программным моделям отдельных узлов 1879ВМ4 практически идентичен процессорам Л1879ВМ1 и 1879ВМ2 (рис.9). Система команд 1879ВМ4 отличается от Л1879ВМ1 и 1879ВМ2 весьма незначительно, что позволяет после перекомпиляции использовать в новом процессоре созданное для его предшественников системное и прикладное ПО.

В 1879ВМ4 добавлены два программируемых канала ПДП типа "память-память". Введены два коммуникационных порта синхронного типа (CP0/CP1), что позволит увеличить скорость обмена до 75—150 Мбайт/с по каждому порту вместо 20 Мбайт/с у предшественников. Добавлено 8 программируемых входов/выходов, немаскируемое прерывание, а также прерывания от каналов ПДП.

Внутренняя память состоит из четырех одинаковых банков однопортовой синхронной SRAM 8К×64 бит (по два в адресном пространстве локальной и глобальной шин). Все банки памяти работают как псевдодвухпортовые, что позволяет одновременно обращаться к памяти как со стороны

Рис. 10. Карта памяти процессора 1879ВМ4

процессорного ядра, так и со стороны каналов ПДП. В каждом такте реализуется до четырех доступов к внутренней памяти и до двух — к внешней. Кроме того, возможно обращение к внутренней памяти по двум каналам ПДП, которые работают в фоновом режиме. Одновременно обмены могут происходить только между различными блоками (локальными или глобальными) внутренней и внешней памяти. Таким образом, всего в процессоре в каждом такте поддерживается до шести обращений во внутреннюю память и до двух — во внешнюю память. Любое активное внешнее устройство, захватившее управление внешней шиной, может обратиться к подключенной к ней внутренней памяти для записи/чтения.

Распределение адресного пространства 1879ВМ4 (рис.10) также отличается от предшественников. Внешняя память на локальной и глобальной шинах разделена на четыре банка. В качестве одного из банков на соответствующие адреса внешних шин может быть подключен другой процессор. Адреса векторов прерываний 1879ВМ4 расположены в начальных адресах банка внутренней памяти 0 на локальной шине.

Программируемый интерфейс 1879ВМ4 позволяет непосредственно, без дополнительных контроллеров подключать к выводам 1879ВМ4 СБИС внешней памяти типа SRAM, ROM, Flash ROM и СБИС синхронной памяти (SSRAM, SDRAM). Разные банки внешней памяти одного процессора могут быть реализованы на СБИС различного типа.

1879ВМ4 на кристалле имеет 8-канальную (8-way) наборно-ассоциативную кэш-память команд объемом 8 Кбит (1К×64) без блокировок при промахах. При обращении во внешнюю память выбранные команды попадают одновременно в процессорное ядро и в кэш. При повторном обращении по тому же адресу команды будут выбираться из кэш, а не из внешней памяти. Команды из внутренней памяти не кэшируются. Кэш команд освобождает программиста от работы по трансляции кода из внешней памяти во внутреннюю.

Аппаратные средства 1879ВМ4 позволяют без дополнительного внешнего контроллера подключать к любой внешней шине (локальной или глобальной) такой же процессор. Несколько процессоров на одной шине работают в режиме разделения памяти, подключенной к этой шине. Данная способность 1879ВМ4 позволяет строить на его основе мультипроцессорные системы с линейной структурой. К единой внешней шине могут быть подключены как локальные, так и глобальные шины процессоров 1879ВМ4. Дополнительные конфигурационные выводы определяют, какой из процессоров управляет шиной после системного сброса.

В адресное пространство каждого 1879ВМ4 мультипроцессорной системы входит вся его внутренняя и внешняя память, а также по одному банку внутренней памяти соседних процессоров, подключенных к локальной и глобальной шинам данного процессора. Каждый 1879ВМ4 может обращаться к ячейкам внутренней памяти соседнего процессора как в программном режиме, так и в режиме ПДП. Включение в адресное пространство 1879ВМ4 банков внутренней памяти соседних процессоров позволяет даже без СБИС внешней памяти увеличить объем ОЗУ каждого процессора до 4 Мбит.

При работе нескольких 1879ВМ4 в режиме разделения памяти в каждый момент времени внешней шиной управляет только один процессор — "ведущий", другой процессор на этой шине является "ведомым". "Ведущий" процессор может непосредственно обращаться как к своей внутренней, так и к внешней памяти или к внутренней памяти "ведомого" процессора. "Ведомому" процессору разрешено непосредственно адресовать только свою внутреннюю память. Для смены ролей "ведомый" процессор выставляет запрос на захват шины. "ведущий" по окончании текущих операций на внешней шине в ответ выставляет сигнал разрешения на захват шины и становится "ведомым", соответственно, "ведомый" преврашается в "ведущего". Передачу управления внешней шиной может контролировать и программист с помощью битов "разрешение передачи управления локальной (глобальной) шиной" регистра PSWR.

1879ВМ4 имеет развитую систему внутренних шин, что позволяет увеличить число одновременно выполняемых циклов обращения к памяти и тем самым повысить производительность процессора. В набор внутренних шин входят:

- шина MEM\_IB для пересылки команд из внешней памяти в кэш и далее в процессорное ядро по шине команд IB;

- шина скалярных данных (SDB) для чтения скалярных данных из памяти в процессорное ядро, а также для их записи в память или в регистры периферийных узлов;

- шина входных векторных данных (VDIB);

- шина весов (WB):

- шина векторного регистра (VRB) для пересылки данных из памяти в векторный регистр векторного узла;

- шина выходных векторных данных (VDOB) для записи результатов работы векторного узла в память без остановки других операций чтения/записи процессорного ядра.

Коммутатор 6→5 динамически объединяет одну из шести шин данных внешней или внутренней памяти с одной из пяти внутренних шин ядра и кэш-памяти. Встроенный сопроцессор ПДП обслуживает два коммуникационных порта (СРО и СР1), а также два программно настраиваемых канала ПДП "памятьпамять". Он управляет коммутатором шин BUS SWITCH для организации обмена между коммуникационными портами и банками памяти или между самими банками памяти по специальным шинам данных/адреса ПДП в локальную и глобальную память (DMA LDB/LAB и DMA GDB/GAB).

В 1879ВМ4 используется семь генераторов адреса (блок AGU) — один для команд и шесть для данных. Это позволяет в одном такте формировать до семи запросов на работу с памятью: на выборку команды, на чтение и запись скалярных данных, на чтение до трех данных для векторного сопроцессора и на запись результата работы векторного сопроцессора. Все семь запросов могут быть обслужены одновременно, если адресуются различные банки внутренней памяти, адреса внешней памяти принадлежат различным шинам, а команда выбирается из кэш-памяти.

Для 1879ВМ4 изменяются правила выполнения команд на первом, втором и третьем уровнях конвейера. Все команды при запуске, как и у предыдущих моделей, попадают в общую часть первого уровня конвейера. Скалярная команда выставляет запрос на доступ в память. Если нет блокировок от блока приоритетов и от нижних ступеней конвейера, команда попадает на вторую ступень и освобождает общую часть. Векторная команда при запуске занимает общую часть первого уровня конвейера на один процессорный такт. За это время она вычисляет адрес первого обращения в память. Одновременно на специальном арифметическом устройстве, содержащем умножитель (5×32 разряда) и 32-разрядный сумматор, формируется новое значение адресного регистра, использующегося в качестве базы. Это значение совпадает с тем, что должно получиться после завершения выполнения векторной команды. В следующем такте векторная команда освобождает общую часть и занимает один из шести адресных генераторов, находящихся вне процессорного ядра. При этом выдается адрес первого обращения в память по шине ADDR и значение смещения по шине BIAS. Далее адресный генератор работает самостоятельно, не занимая ресурсов процессорного ядра.

На втором уровне конвейера вводится единая очередь для скалярных и векторных команд, ожидающих своих данных. Глубина этой очереди — восемь команд, что позволяет эффективно работать с внешней синхронной памятью в конвейерном режиме: можно выставить до восьми запросов на чтение. прежде чем придут первые данные. На третьем уровне конвейера команды из очереди последовательно попадают на исполнительные конвейеры (один для скалярных операций и пять для векторных операций) и ожидают своих данных. Причем векторная команда может занять один или несколько исполнительных конвейеров в зависимости от кода операции. Конвейеры для векторной операции имеют переменную глубину, зависящую от ее типа. Скалярные команды после получения данных выполняют операцию в арифметико-логическом устройстве (АЛУ) (при необходимости) и заканчивают свою работу. Если в скалярной команде задан один и тот же регистр в качестве приемника для операции в АЛУ и операции ввода-вывода, более приоритетна последняя.

Перечисленные особенности конвейера позволяют одновременно выполнять одну скалярную и до пяти векторных команд, в том числе четыре команды обмена с памятью, а также эффективно работать с конвейером доступа в память переменной глубины от одного до восьми тактов.

Таблица 2. Пиковая производительность (MMAC/c) процессоров семейства NeuroMatrix и DSP TigerSHARC ADSP-TS001 компании Analog Devices

| Процессор                |    | TigerSHARC<br>ADSP-TS001 | Л1879ВМ1 | 1879BM2 | 1879BM4 |

|--------------------------|----|--------------------------|----------|---------|---------|

| Тактовая<br>частота, МГц |    | 150                      | 40       | 80      | 150     |

| Разрядность<br>данных    | 2  | 1200                     | 8960     | 17920   | 33600   |

|                          | 4  | 1200                     | 3200     | 6400    | 12000   |

|                          | 8  | 1200                     | 960      | 1920    | 3600    |

|                          | 16 | 1200                     | 160      | 320     | 600     |

|                          | 32 | 300                      | 80       | 160     | 300     |

В 1879ВМ4 предусмотрена загрузка матрицы весов по принципу один вектор весов за один такт. Это существенно снижает минимальный эффективный размер пакета обрабатываемых векторов (раньше он был равен 32) и значительно увеличивает производительность процессора.

Также введено аппаратное копирование вершины системного стека — ячейки памяти, хранящей последний адрес возврата из подпрограммы или прерывания и значение регистра PSWR при входе в подпрограмму/прерывание. Это позволяет резко ускорить выполнение команд возврата из подпрограммы или прерывания, особенно если системный стек расположен во внешней памяти.

Благодаря всем перечисленным архитектурным и структурным усовершенствованиям реальная производительность 1879ВМ4 по сравнению с Л1879ВМ1 и 1879ВМ2 должна повыситься соответственно в 3–12 и 1,5–6 раз в зависимости от класса решаемых задач (табл.2).

В заключение отметим, что отечественные процессоры семейства NeuroMatrix – это представители нового класса векторно-конвейерных DSP. Их отличает высокая производительность на задачах обработки больших потоков данных при относительно небольших аппаратных затратах и малом энергопотреблении. Просматриваются пути дальнейшего повышения вычислительной мощности процессоров семейства как за счет углубления конвейера, так и путем их реализации на технологиях с меньшими топологическими нормами. Благодаря аппаратной поддержке матрично-векторных операций и возможности увеличения производительности при обработке данных меньшей разрядности процессоры NeuroMatrix эффективны для решения широкого класса задач в таких областях, как видеообработка, распознавание образов, сигнальная обработка, радиолокация, телекоммуникация, навигация и многие другие. А встроенные средства для построения многопроцессорных систем позволяют использовать их как базовые блоки для создания параллельных вычислительных систем.

#### **ЛИТЕРАТУРА**

- 1. **Шахнович И.** Отечественный процессор цифровой обработки сигналов NM6403 чудо свершилось. ЭЛЕКТРОНИКА: НТБ, 1999, №2, с. 30–34.

- 2. Texas Instruments Europe. Implementation of an Image Processing Library for the TMS320C8X (MVP). BPRA059, July, 1997.

- 3. **Борисов Ю.** Комплекс "Трафик-Монитор" на базе процессора Л1879ВМ1. Особенности разработки. ЭЛЕКТРОНИКА: НТБ, 2003, №6.

- 4. **Мушкаев С.** Оценка производительности корреляционных мер сходства в задачах полного поиска движения на процессоре NM6403. Сборник докладов научно-технической конференции "Молодежь в науке", 2005.

- 5. **Мушкаев С.** К вычислению квадратов и абсолютных значений на процессоре NM6403(Л1879ВМ1). Цифровая обработка сигналов, 2005, №1.

- 6. **Мушкаев С.** Реализация ранжирующих и медианных фильтров на процессоре NM6403 (Л1879ВМ1). Цифровая обработка сигналов, 2005, №1.

- 7. **Миронов С., Дударев В., Богатов А.** Цифровая обработка радиолокационных сигналов. ЭЛЕКТРОНИКА: НТБ, 2003, №3.

- 8. **Мушкаев С., Ландышев С**. Применение процессора Л1879ВМ1 для сжатия изображений. Цифровая обработка сигналов, 2002, №1.

- 9. **Кашкаров В., Мушкаев С.** Организация параллельных вычислений в алгоритмах БПФ на процессоре NM6403. Цифровая обработка сигналов, 2001, №1.