# ПРОГРАММИРУЕМЫЙ ШИРОКОДИАПАЗОННЫЙ ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ

## ПО ТЕХНОЛОГИИ "СИСТЕМА НА КРИСТАЛЛЕ"

Технологии "система на кристалле" все чаще используются при разработке различных устройств. В статье описано применение данных технологий для создания формирователей импульсов. Формирователи предназначены для использования в приборах, выполняющих синхронизацию шкал времени в навигационных системах, в частности ГЛОНАСС и GPS. Еще одна область применения формирователей — предпусковые и предполетные диагностические системы и комплексы.

ОСНОВНЫЕ ХАРАКТЕРИСТИКИ ФОРМИРОВАТЕЛЯ

Формирователь импульсов (далее — формирователь) генерирует последовательности импульсов с заданными периодами следования и длительностями. Длительности импульсов и интервалы между ними задаются методом последовательного счета. Внутренний опорный генератор создает последовательность импульсов определенного периода — так называемых квантующих импульсов. Длительность выходных импуль-

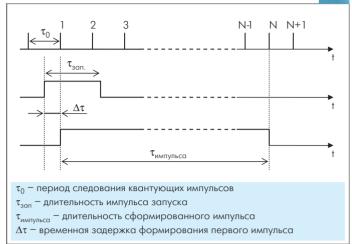

Рис. 1. Временная диаграмма выходных сигналов формирователя

В.Малых, П.Моисеев, Е.Аржадеева

сов формирователя определяется через число квантующих импульсов.

В устройстве формируются три независимых временных интервала. Два из них соответствуют длительности генерируемых импульсов и один — задержке между этими импульсами (рис.1).

Формирователь имеет три независимых выхода и может работать как в режиме непрерывной генерации, так и в режиме внешнего запуска. При работе в режиме непрерывной генерации временная диаграмма формирования импульсов соответствует изображенной на рис 1.

В режиме внешнего запуска оба выходных импульса возникают только при наличии внешнего импульса запуска. В приборе появляется дополнительная задержка формирования первого импульса  $\Delta \tau$  (рис.2). Данная задержка обусловливает некоторую дополнительную нестабильность генерирования выходных импульсов. Временные диаграммы формирования второго импульса и задержки между импульсами такие же, как в режиме непрерывной генерации (см. рис.1).

Длительность импульса можно записать как:

$$\tau_{\text{импульса}} = N \tau_0.$$

Здесь N — число квантующих импульсов. Относительная погрешность установки длительности импульсов определяется формулой:

$$\delta_{0\mu\mu\eta\eta\eta\rho\alpha} = \pm \delta_0 \pm 1/N$$

,

где  $\delta_0$  — относительная погрешность периода квантующих импульсов.

Абсолютная погрешность вычисляется по формуле:

$$\Delta \delta_{0MMIVJIBCA} = \pm \delta_0 N \tau_0 \pm \tau_0.$$

При достаточно малом значении  $\delta_0$  предельное значение абсолютной погрешности равно  $\pm \tau_0$ .

Приведенные формулы показывают, что для повышения точности формирования одного импульса необходимо уменьшать значение  $\delta_0$  и  $\tau_0$ . На современном уровне технологий достижимы значения  $\delta_0$  =10<sup>-8</sup>-10<sup>-9</sup> за месяц и  $\tau_0$  = 0,5-1 нс.

Формирователь реализован в двух вариантах — в виде программируемой логической интегральной схемы (ПЛИС) и в виде заказной интегральной схемы (ASIC). В первом случае формирователь разрабатывался на основе традиционных схемных методов проектирования с использованием графических интерфейсов. Во втором случае применялась технология проектирования "система на кристалле".

#### РЕАЛИЗАЦИЯ НА ПЛИС

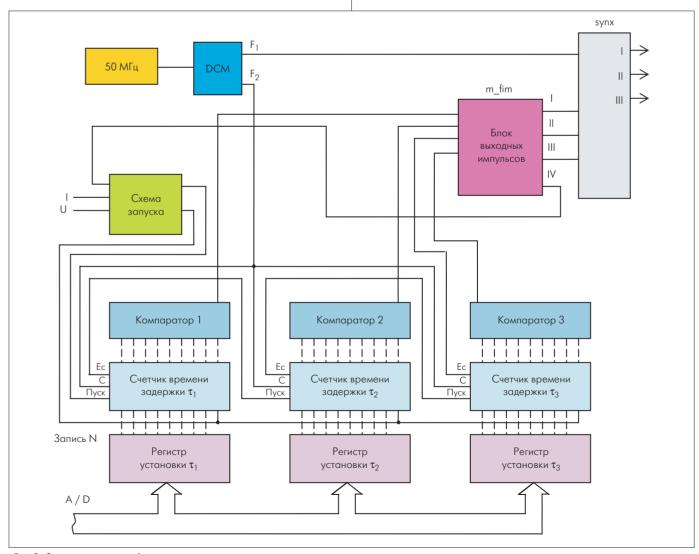

Первый вариант формирователя был выполнен на FPGA семейства Spartan-3 фирмы XILINX [1]. В его схеме (рис.3)

Рис.2. Временная диаграмма формирования первого импульса при внешнем запуске

использованы специализированные устройства, входящие в библиотеку семейства, в частности Digital Clock Manager (DCM) [2]. DCM позволяет синтезировать частоты 100 МГц и 200 МГц из входной частоты 50 МГц.

Схема работает следующим образом. С выхода кварцевого генератора сигнал с частотой 50 МГц (стабильность

Рис. 3. Структурная схема формирователя импульсов

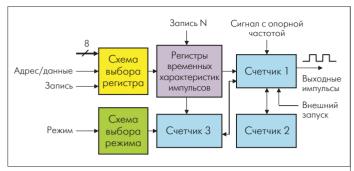

Рис 4. Структурная схема формирователя импульсов, реализованного в виде ASIC. Под счетчиками 1, 2, 3 подразумеваются блоки, объединяющие непосредственно счетчик, компаратор и формирователь импульса.

не менее  $10^{-8}$ ) поступает на вход DCM, на выходе которого синтезируются частоты  $F_1=200~\text{MFц}$  и  $F_2=100~\text{MFц}$ . Сигнал с частотой  $F_1$  синхронизирует выходные импульсы в блоке synx. Сигнал с опорной частотой  $F_2$  поступает на синхровходы C счетчиков формирования временных интервалов. Это обеспечивает дискретность установки длительности выходных импульсов 10~Hc. Счетчики запускаются поочередно, управление последовательностью запуска проиводится по входам "пуск" и  $E_c$ .

Схема запуска обеспечивает начальную загрузку счетчиков формирования задержки, а также их запуск по фронту внешнего запускающего импульса или внутреннего сигнала, в зависимости от состояния входа управления "U". Внутренний сигнал "пуск" запускает счетчики, выходы которых поступают на один из входов компараторов. Другие входы компараторов подключены к регистрам, содержащим двоичный код, который определяет временные параметры требуемых импульсов. Сигналы с выходов компараторов поступают на блок выходных импульсов (m\_fim).

Блок m\_fim фиксирует сформированные импульсы, соответствующие заданным временным интервалам  $\tau_1$  (канал I — первый импульс),  $\tau_2$  (канал II — задержка между первым и вторым импульсом),  $\tau_3$  (канал III — второй импульс), и передает соответствующие сигналы на блок синхронизации (synx). В канале IV формируется сигнал внутреннего запуска, необходимый для работы формирователя импульсов в режиме непрерывной генерации.

Заданные временные параметры импульсов загружаются в регистры установки по шине A/D. Микросхема формирователя размещается в 100-выводном пластмассовом корпусе типа VQ.

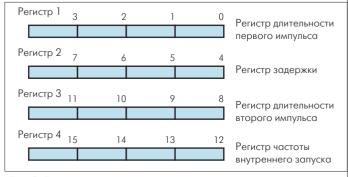

Рис. 5. Регистры установки временных параметров

Разработка микросхемы проводилась с использованием САПР ISE 7.1i фирмы Xilinx и ModelSim XE III 6.0a фирмы Mentor Graphics. Отладка модели на функциональном уровне была проведена с применением стандартных библиотечных макросов из библиотеки САПР.

Недостатком реализации формирователя на ПЛИС является неполная реализация ресурсов кристалла и интеллектуальных возможностей ПЛИС и САПР. Поэтому был опробован маршрут разработки в виде заказной интегральной схемы (ASIC). В данном маршруте ПЛИС использовалась только для опробования поведенческой модели устройства.

#### РЕАЛИЗАЦИЯ В ВИДЕ ЗАКАЗНОЙ ИНТЕГРАЛЬНОЙ СХЕМЫ (ASIC)

Поскольку область возможного применения формирователя очень широка, он был реализован по технологии "система на кристалле" и проектировался как СФ-блок (IP-core). На первом этапе была разработана поведенческая модель формирователя с использованием языка Verilog. Для синтеза схемы из представления на языке Verilog был задействован синтезатор Build Gates. Рассмотрим работу устройства на схеме, восстановленной из RTL-описания (рис.4).

На мультиплексированной восьмиразрядной шине "адрес/данные" выставляется адрес регистра, в который записывается двоичный код, определяющий длительность импульса. Выборка адреса или данных производится по значению сигнала "адрес/данные" (0 — передача адреса, 1 — передача данных). Информация с шины адреса/данных переписывается в выбранный регистр. Всего используется шестнадцать 8-разрядных регистров, каждые четыре из которых образуют один 32-разрядный исполнительный регистр, который определяет длительность импульса или длительность задержки между импульсами (рис.5).

По сигналу "запись N" происходит одновременная загрузка длительностей импульсов и задержки между ними в исполнительные регистры формирователя.

Переключение между режимами внешнего запуска и непрерывной генерации имеет место при изменении уровня на входе "режим".

Для формирования сигналов на выходе микросхемы в режиме внешнего запуска на вход "внешний запуск" подается запускающий импульс. По его фронту сигнал с опорной тактовой частотой начинает поступать на вход синхронизации счетчика 1. Каждый импульс опорной частоты увеличивает содержание этого счетчика на 1. Формирование первого импульса заканчивается, когда содержимое счетчика 1 станет равным содержимому регистра 1. После этого счетчик 1 сбрасывается в 0, а содержимое счетчика 2 увеличивается на 1. Таким образом, счетчик 2 подключает к компаратору и счетчику 1 регистр 2. В счетчике 1 повторно формируется временной интервал (в данном случае — длительность задержки). Данный процесс завершается, когда содержимое

счетчика 1 становится равным содержимому регистра 2. Точно так же формируется и второй импульс. После этого счетчики 1 и 2 возвращаются в исходное нулевое состояние.

Работа в режиме непрерывной генерации проходит аналогичным образом. Отличие здесь в том, что последовательности импульсов на выходе формирователя возникают периодически, а внешний запускающий импульс не используется. Непрерывный внутренний запуск формирователя обеспечивается счетчиком 3. Частота внутреннего запуска обусловлена содержимым регистра 4.

Степень интеграции и структурный состав схемы определялись с помощью синтезатора Leonardo Spectrum.

Чтобы проверить функциональность формирователя, был разработан тест и смоделирована схема с использованием Model Sim. Отладка СФ-блока в виде твердой копии проводилась с применением отладочного стенда фирмы Xilinx для семейства Spartan 3.

Топология СБИС для реализации в виде ASIC разрабатывалась в среде САПР фирмы Cadence. Для моделирования применялась программа NCLaunch. При проектировании топологии микросхемы были выбраны библиотеки завода XFAB. Моделирование после разработки топологии с проектными нормами 0,6 мкм показало максимальную частоту работы формирователя 100 МГц, с нормами 0,35 мкм — 200 МГц. Микросхема размещена в металлокерамическом корпусе 4226.108-2.

Преимуществом реализации формирователя в виде ASIC является полное использование ресурсов кремния и САПР. Степень интеграции уменьшается в три раза по сравнению с вариантом реализации в виде ПЛИС. Однако нужно иметь в виду, что качество синтеза у синтезаторов физического уровня различных САПР неодинаково, что отражается на скоростных характеристиках микросхемы.

#### ИСПОЛЬЗОВАНИЕ В ПРИБОРАХ

Формирователи импульсов в виде ПЛИС и ASIC применяются в радиоизмерительной технике для синхронизации шкал времени в навигационных системах, в частности ГЛОНАСС и GPS, а также в предпусковых и предполетных диагностических системах и комплексах.

Одно из приложений формирователя — его использование в качестве ядра перестраиваемого генератора оптических импульсов ОТ5-101. Генератор предназначен для поверки и аттестации оптических рефлектометров в составе автоматизированных рабочих мест (APM).

Ядро представляет собой первичный трехканальный импульсный генератор с регулируемыми длительностями импульсов и задержками между ними. Длительность выходных импульсов прибора меняется в пределах 0,1—50 мкс. Максимальная задержка между импульсами составляет 5 мс. Дискретность установки длительности выходных импульсов равна 10 нс. При работе генератора в режиме внешнего за-

пуска частота следования внешних запускающих импульсов не должна превышать значение, определяемое формулой:

$$F \le 1/(\tau_1 + \tau_2 + \tau_3) + 10$$

HC,

где:

т<sub>1</sub> – длительность первого сформированного импульса,

$au_2$  — длительность задержки между первым и вторым импульсом,

τ<sub>3</sub> – длительность второго сформированного импульса.

Амплитуда запускающих импульсов от внешнего генератора— не более 3,3 В. Длительность не нормируется. Запуск осуществляется положительным фронтом входного импульса.

Формирователь управляется с помощью микроконтроллера XS164, встроенного в генератор оптических импульсов. Контроллер обеспечивает установку необходимых временных параметров генератора и режимов его работы, а также непрерывную диагностику.

#### **ЛИТЕРАТУРА**

- 1. Xilinx Inc. (2003). Spartan 3 Platform FPGA Handbook. Advance Product Specification. July 11.

- 2. **Кузелин М.О.**, **Кнышев Д.А.**, **Зотов В.Ю.** Современные семейства ПЛИС фирмы Xilinx. М.: Горячая линия Телеком, 2004. 440 с.

### Конференция МЭС-2006 — уже традиция

Вторая всероссийская научно-техническая конференция "Проблемы разработки перспективных микроэлектронных систем — 2006" (МЭС-2006) прошла с 9 по 13 октября 2006 года на базе подмосковного санатория "Истра". Как и год назад, конференция была посвящена актуальным вопросам автоматизации проектирования МЭС, систем на кристалле, IP-блоков и новой элементной базы микроэлектроники.

Организатор конференции — Институт проблем проектирования в микроэлектронике (ИППМ), соорганизаторы — Московский государственный институт электронной техники (МИЭТ), НИИМА "Прогресс", а также Московское научно-техническое общество радиотехники, электроники и связи им. А.С.Попова (МНТОРЭС). Организационный комитет МЭС-2006 возглавил директор ИППМ РАН, академик РАН А.Л.Стемпковский.

Учредители конференции — отделение информационных технологий и вычислительных систем РАН, Российский фонд фундаментальных исследований, МГУ им. М.В.Ломоносова, Роснаука, Федеральный фонд развития электронной техники, департамент науки и промышленной политики Москвы, ОАО "Московский комитет по науке и технологиям", Ассоциация "Фонд УНИЭТ".

Спонсорами МЭС-2006 выступили такие компании, как НИЦ "Микростайл"; Freescale Semiconductor; Intel; Megratec-Inline Group и дистрибьютор Synopsys в России компания Alternative Solutions Alt-S.

Всего на конференции прозвучали четыре пленарных доклада, десять аналитических и 83 сессионных (180 авторов из 11 городов России, а также из Армении, Белоруссии, Польши и Украины) и четыре доклада-презентации ведущих мировых разработчиков САПР СБИС. Среди авторов докладов 31 доктор наук, 42 кандидата наук, 15 аспирантов, 1 студент. Доклады представлены от институтов Российской и национальных Академий наук, высших учебных заведений, государственных и коммерческих организаций, в том числе от зарубежных коммерческих компаний и их представительств в России.

Из пленарных докладов отметим выступление заместителя начальника Управления радиоэлектронной промышленности и систем управления Н.А.Иванчука. Он, в частности, отметил, что трехлетняя борьба Управления за сохранение отрасли начала приносить свои плоды. Уже с 2007 года ожидается государственное финансирование отрасли в размере порядка 1 млрд. долл. Это превышает объем бюджетного финансирования российской электроники за предшествующие 15 лет.

О новых принципах формирования ГОЗ в области МЭС рассказал заместитель начальника пятого направления Управления развития базовых военных технологий и специальных проектов Ю.Г.Малофеев. Он подчеркнул, что госзаказчик будет как воспроизводить существующие технологии, так и поддерживать создание новых архитектур СБИС. В частности, будут испФУАЗЙ ЬТПИЛБОГ Пользоваться как контроллеры с MIPS- и SPARC- архитектурой, так и собственные архитектурные реше-

ния, такие как "Мультикор" и Е2к ("Эльбрус-2000"). Докладчик отметил, что системы на кристалле (СнК) и IP-блоков — это важное и перспекитвное направление, но обязательное для них условие — массовое универсальное применение.

Большой интерес вызвал рассказ Н.В.Суэтина (ЗАО "Интел А/О") о перспективных технологиях СБИС компании Intel. Несмотря ни на что, закон Мура продолжает выполняться — такова была красная нить его выступления.

В организации конференции 2006 года появился ряд новых, принципиальных отличий. Улучшилась система отбора выступлений. Теперь для включения в программу конференции доклады рецензировались ведущими учеными РАН, вузов и профильных компаний, что значительно повысило их качество. В результате из заявленных 112 сессионных докладов было оставлено лишь 83.

В программу МЭС-2006 вошли десять так называемых аналитических докладов, прочитанных известными учеными России и зарубежья. Впервые была организована презентация современных научно-технических решений компаний — ведущих мировых разработчиков САПР СБИС: Cadence, Mentor Graphics, Synopsys и Agilent Technologies.

Работа конференции проходила по трем научным направлениям: методы и средства автоматизации проектирования МЭС; проектирование функциональных блоков СБИС; проектирование систем на кристалле. В рамках этих направлений на сессионных заседаниях рассмотрены различные аспекты разработки САПР МЭС и СБИС. Среди них — методы логического моделирования; логического синтеза в САПР СБИС; моделирования радиотехнических СБИС; экстракции параметров для САПР СБИС; автоматизации топологического проектирования в САПР СБИС; приборно-технологического моделирования и высокоуровневого моделирования.

Обсужден опыт разработки цифровых и цифроаналоговых МЭС. Большое внимание было уделено общим проблемам проектирования СБИС типа "система на кристалле", в том числе — разработке архитектуры систем, реализуемых в виде СнК. Живой интерес участников вызвала проблема IP-блоков и их включения в СнК. Был представлен ряд докладов по разработке и использованию отечественных платформ СнК. Все эти вопросы рассматривались в ходе сессий: специализированные аналого-цифровые микросхемы и СФ-блоки; проектирование цифровых СБИС; проектирование технологических процессов; методы цифровой обработки информации и цифровые фильтры; разработка специализированных СБИС типа "система на кристалле"; разработка СБИС сигнальных процессоров; проектирование элементов СБИС; проектирование фотоприемных СБИС.

Представленные доклады вызвали значительный интерес специалистов и сопровождались оживленной дискуссией. Следующая, уже третья, конференция МЭС состоится в 2008 году.

И. Шахнович, по материалам ИППИ РАН.