# СОВРЕМЕННЫЕ ТЕХНОЛОГИИ RTL-C В ПРОДУКТАХ КОМПАНИИ SYNOPSYS

Процесс проектирования цифровых СБИС уже невозможно представить без средств синтеза принципиальной электрической схемы устройства из его описания на уровне регистровых передач (RTL-синтеза). Сегодня основная задача разработчика — создать корректное RTL-описание на языке Verilog или VHDL. На этом "ручная работа" практически заканчивается, последующие этапы проектирования в основном выполняются с помощью различных процедур синтеза. RTL-синтез - первый в последовательности таких процедур, и от эффективности используемых здесь технологий во многом зависит результат всего проектирования.

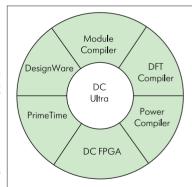

ервый коммерческий компилятор логических схем для заказных БИС был выпущен компанией Synopsys в 1987 году. Сегодня 86% мирового рынка средств логического синтеза для заказных цифровых СБИС и систем-на-кристалле принадлежит продуктам компании, а система Design Compiler (DC) – общепризнанный лидер среди систем RTL-синтеза. Структура средств RTL-синтеза компании Synopsys представлена на рис.1. Ядро семейства DC - систе-

ма DC Ultra. Здесь сосредоточены базовые технологии синтеза, на которые опираются остальные средства, ориентированные на решение специфических задач, таких как синтез с учетом тестопригодности (DFT Compiler); синтез энергосберегающих схем (Power Compiler); yuer ocoбенностей реализации на FPGA (DC FPGA); оценка временных характеристик с помощью системы статического cemeйctba Design Compiler временного анализа (Prime

Рис. 1. Структура средств RTL-синтеза

Time); синтез с учетом существующих IP-блоков (Module Compiler и библиотека IP-блоков DesignWare). Совмещение мощного современного базового аппарата логического синтеза и специализированных, часто уникальных, алгоритмов позволяет добиваться наилучших результатов как по общим критериям площади и быстродействия, так и с учетом специфических требований, предъявляемых к конкретному проекту. Ядро DC Ultra также является базисом для системы Physical Compiler, в которой процесс логического синтеза объединен с размещением и макротрассировкой (global routing).

B.Кравченко; vitally.kravchenko@alt-s.com Д.Радченко; dmitry.radchenko@alt-s.com

#### БАЗОВЫЕ ТЕХНОЛОГИИ RTL-CUHTE3A (DC ULTRA)

Базовые методы RTL-синтеза системы DC Ultra включают учет характера арифметических операций, оптимизацию размещения регистров в комбинационной логике (retiming), минимизацию критических путей, синтез с учетом оценок задержек. Большое внимание уделено решению задачи управляемого синтеза, при котором пользователь может добиваться необходимого результата путем выбора приоритетов целевой функции, а также задания прямых указаний компилятору в RTL-описании.

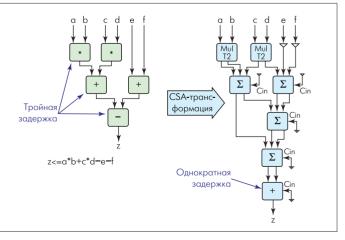

Учет характера используемых арифметических операций особенно важен для схем с трактами обработки данных. Для таких схем система может сама идентифицировать в тексте RTL-описания деревья арифметических операций и произвести их оптимизацию с помощью технологии сохранения битов переноса (Carry Save Adder, CSA). В процессе оптимизации удается повысить быстродействие за счет уменьшения числа тактов выполнения арифметической операции. Пример использования CSA-технологии приведен на рис.2. При прямом развороте представленного на рисунке выражения дерево арифметических операций будет трехуровневым. После CSAтрансформации все вычисления могут быть реализованы в рамках одного уровня.

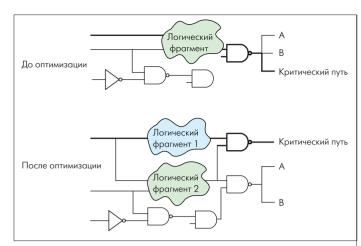

Большое внимание в системе DC Ultra уделяется синтезу критических цепей, поскольку критические цепи определяют быстродействие синтезируемого устройства в целом. Чтобы добиться максимального быстродействия критических цепей, используется целый пакет различных алгоритмов оптимизации. На начальной стадии синтеза, еще до привязки к конкретному библиотечному базису, проводится оптимизация на вентильном уровне (уровне базовой внутренней библиотеки GTECH компании Synopsys). Происходит

Рис. 2. Использование CSA-технологии для оптимизации арифметических операций

Рис.З. Разгрузка критического пути за счет частичного дублирования логических фрагментов

реструктуризация логической схемы с учетом оценки временных характеристик. Одна из основных применяемых здесь технологий — частичное дублирование и оптимизация фрагментов логических схем, направленные на разгрузку критического пути (рис.3). На этапе привязки логической схемы к библиотечному базису оптимизация осуществляется за счет использования на критическом пути библиотечных элементов с большим быстродействием.

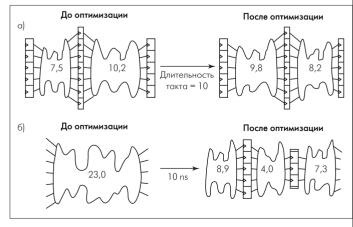

Подавляющее большинство проектируемых цифровых схем — синхронные. В процессе создания RTL-описания и последующего синтеза на основе этого описания подсхемы, описываемые комбинационной логикой, разбиваются регистрами на фрагменты. Задержка каждого такого фрагмента не должна превышать тактового периода. Технология оптимизации расстановки регистров (retiming) позволяет, за счет оптимизации расположения существующих регистров и вставки дополнительных, добиваться как улучшения временных параметров схемы, так и уменьшения используемой площади (рис.4а,6).

Логический синтез и оптимизация с учетом временных характеристик межсоединений — обязательный компонент современных систем RTL-синтеза, поскольку задержки на связях при современных технологиях реализации систем-на-кристалле могут превышать задержки логических элементов. Предварительная оценка задержек в DC Ultra осуществляется на основе использования статистических моделей распределения связей, причем пользователь может задавать свои модели (в системе есть встроенный инструмент для создания статистических моделей распределения связей). Для

Рис.4. Оптимизация расположения регистров во фрагментах комбинационных логических схем: а) за счет оптимизации расположения существующих регистров; б) за счет вставки новых регистров

детальной оптимизации можно использовать информацию о задержках, полученную по результатам реальной физической реализации. Поддерживаются форматы данных SDF (Standard Delay Format) и PDEF (Physical Design Exchange Format), с помошью которых можно передавать информацию о реальной физической иерархии, емкости связей, расположении ячеек и выводов цепей.

Основная проблема организации логической оптимизации с учетом задержек, полученных по результатам физической реализации, — обеспечить сходимость итерационного процесса "логическая оптимизация — физический синтез — логическая оптимизация". После логической оптимизации и синтеза нового физического прототипа изменения могут быть настолько значительны, что значения задержек, которые использовались при логической оптимизации, окажутся неактуальными. Технология локальной оптимизации (Location Based Optimization, LBO) позволяет добиваться сходимости за счет использоваия точной информации о расположении ячеек и выводов. Все изменения осуществляются таким образом, чтобы минимизировать их влияние на результирующую топологию. Статистические модели в технологии LBO не используются, оценка задержек проводится на основе реальных данных о расположении ячеек.

Многие программы, реализующие логический синтез, для разработчика часто выглядят как "черный ящик". На входе RTL-описание, на выходе — синтезированная схема, способ повлиять на результат практически отсутствует. Чтобы избежать этого недостатка, в DC Ultra предусмотрены не только механизмы формирования целевых функций, определяющих приоритеты оптимизиции (быстродействие, площадь, другие факторы), но и возможность задания непосредственно в RTL-коде прямых указаний для компилятора. Например, можно указать типы ячеек, которые надо использовать, задать характер оптимизации для выделенного фрагмента описания.

### TEXHOЛОГИИ СИНТЕЗА С УЧЕТОМ ТЕСТОПРИГОДНОСТИ (DFT COMPILER)

Применение встроенных цепей сканирования (1-Pass Test) - основной на сегодняшний день метод проектирования тестопригодных цифровых интегральных схем. Цепь сканирования представляет собой сдвиговый регистр с подключением к внутренним точкам логической схемы, обеспечивающий возможность передачи данных о состоянии в этих точках наружу для последующего анализа. Технологии системы DFT Compiler позволяют решать задачу создания цепей сканирования на RTL-уровне, что значительно уменьшает риск повторных итераций проектирования, вызванных необходимостью обеспечения тестопригодности. Происходит это за счет того, что все необходимые требования к формированию сканирующих цепей определяются заранее, до процесса синтеза. Алгоритмы синтеза учитывают эти требования при создании вариантов реализации, обеспечивающих максимально полный контроль внутренних состояний. При этом очень важно, что синтез тестопригодной схемы проходит сразу с учетом требований к быстодействию и занимаемой площади, а также всех других ограничений.

Новинка системы DFT Compiler — технология RTL TestDRC, которая позволяет выявлять ошибки в обеспечении тестируемости схемы на уровне RTL-кода. Основные типы выявляемых ошибок:

- ошибки, приводящие к невозможности вставки элементов сканирующей цепи (например, асинхронная или неконтролируемая установка/сброс триггеров);

- ошибки, не позволяющие получить данные (например, подключение тактовых сигналов к информационным входам триггеров);

- ошибки, которые не позволяют обеспечить полное тестовое по-

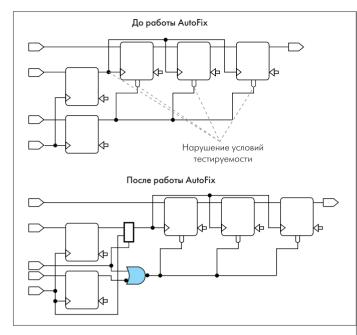

Рис. 5. Пример устранения ассинхронной установки/сброса триггеров

крытие схемы (например, циклы в комбинационных фрагментах логической схемы).

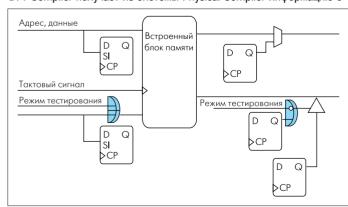

В дополнение к технологии RTL TestDRC, позволяющей выявлять ошибки на уровне RTL-кода, разработана новая технология исправления нарушения условий тестируемости на уровне логических элементов в процессе логического синтеза (AutoFix). Технология AutoFix в основном ориентирована на устранение проблем с асинхнонной и неконтролируемой тактовой установкой/сбросом триггеров, поскольку это наиболее часто встечающиеся ошибки. Вставка дополнительных логических элементов позволяет устранить проблему (рис.5). Благодаря тому, что технология AutoFix непосредственно внедрена в базовый процесс синтеза сканирующих цепей, введение дополнительных тестовых элементов влияет на окончательные характеристики синтезируемой схемы минимальным образом. Еще одна новинка, расширяющая возможности базовых средств технологии AutoFix, - технология Shadow-LogicDFT, которая позволяет автоматически синтезировать тестопригодное логическое окружение встроенных блоков памяти (рис.6).

Есть еще два важных аспекта синтеза цепей сканирования, которые поддерживаются в системе DFT Compiler. Это учет физической реализации и иерархии схемы. Учет физической реализации обеспечивается тесной интеграцией с системой Physical Compiler. DFT Compiler получает из системы Physical Compiler информацию о

<u>Рис.6. Синтез тестопригодного логического окружения встроенных блоков памяти</u>

размещении компонентов и строит сканирующую цепь таким образом, чтобы триггеры цепи располагались рядом с точками подключения. Детальное рассмотрение проблемы иерархической организации цепей сканирования требует отдельной публикации, но упомянуть здесь о ней все-таки необходимо. Иерархическая организация позволяет значительно поднять производительность как при проектировании системы тестирования, так и непосредственно при тестировании. Но пожалуй главное, что может дать применение иерархического подхода, — обеспечение прозрачности тестирования при использовании IP-блоков в системах-на-кристалле. Компания Synopsys была одним из инициаторов принятия стандарта IEEE 1450.6 Core Test Language (CTL) для создания тестовых моделей иерархических блоков и IP, а система DFT Compiler позволяет автоматически генерировать тестовые модели на базе стандарта CTL в процессе RTL-синтеза.

Для обеспечения процесса тестирования СБИС недостаточно просто синтезировать тестопригодную структурную схему, необходимо создать набор тестов, гарантирующий качественную проверку функционирования разрабатываемого устройства. Система автоматической генерации тестов TetraMAX ATPG (Automatic test pattern generation) значительно облегчает решение этой задачи. Сам по себе процесс генерации набора тестов включает много различных аспектов, но с точки зрения рассматриваемых нами технологий RTLсинтеза, реализованных в продуктах компании Synopsys, важен момент взаимосвязи системы TetraMAX ATPG и компилятора DFT Compiler. DFT Compiler помимо синтеза тестопригодной схемы также подготавливает данные о структуре сканирующих цепей и передает их в систему TetraMAX ATPG. Наличие такой информации (по сути, готовых сценариев тестов) позволяет значительно ускорить процесс автоматической генерации тестов. Данные передаются в STIL-формате (IEEE 1450, Standard Test Interface Language), который содержит информацию о компонентах сканирующей цепи, тестовых выводах, описание процедуры инициализации цепи сканирования, а также требования к временным характеристикам тестовых и синхросигналов и ряд других ограничений.

#### СИНТЕЗ ЭНЕРГОСБЕРЕГАЮЩИХ CXEM (POWER COMPILER)

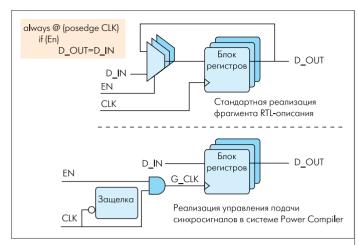

Введение средств управления синхросигналами (clock gating), которые дают возможность отключать их подачу в пассивные блоки устройства, - основной метод, позволяющий добиваться снижения энергопотребления схемы при проектировании ее структуры. Схемы управления на уровне крупных структурных блоков обычно создаются разработчиками вручную, а вот последовательно реализовать этот метод на уровне регистровых передач вручную удается не всегда, поскольку задача эта весьма трудоемкая. Методы автоматического синтеза схем управления синхросигналами, реализованные в системе Power Compiler, позволяют решить эту проблему непосредственно в процессе RTL-синтеза, без внесения изменений в исходный RTL-код. Один из характерных примеров, иллюстрирующий результат автоматического введения средств управления, позволяющих отключить подачу синхросигнала на блок регистров, приведен на рис. 7. Надо заметить, что автоматические средства именно дополняют решения, принятые на уровне крупных структурных блоков. Разработчик может не беспокоиться, что работа Power Compiler что-то нарушит в общей схеме управления синхросигналами. При этом только за счет оптимизации на RTL-уровне снижение энергопотребления может достигать 70%. Дополнительного снижения энергопотребления на 10-20% при синтезе можно достичь путем оптимизации на вентильном уровне. При наличии данных о рассеиваемой мощности в библиотеках, поставляемых полупровод-

Рис.7. Пример работы алгоритмов системы Power Compiler

никовыми фабриками, Power Compiler будет выбирать элементы, обеспечивающие минимизацию потребления, контролируя при этом требования к общему быстродействию устройства.

#### TEXHOЛОГИИ СИНТЕЗА, ОРИЕНТИРОВАННЫЕ НА FPGA (DC FPGA)

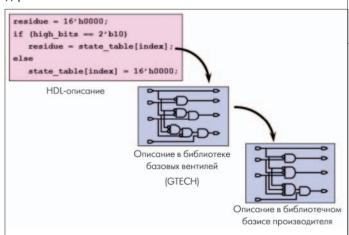

В рамках системы DC FPGA реализована новая технология адаптивной оптимизации (Adaptive Optimization Technology), которая позволяет добиваться лучших результатов синтеза за счет учета специфики архитектуры конкретных FPGA. При этом важно, что настройка на конкретный тип FPGA не требует изменений RTL-кода. Одно и то же описание может использоваться для реализации устройства как на различных типах программируемых кристаллов, так и в виде заказной микросхемы. Это достигается благодаря тому, что вся методология синтеза в продуктах Synopsys реализована таким образом, что сначала RTL-описание разворачивается до уровня базовых логических вентилей, а затем уже осуществляется оптимизация с учетом конкретной библиотеки и архитектуры (рис.8). Помимо технологии адаптивной оптимизации, в DC FPGA впервые реализована поддержка не только процесса компиляции сверху вниз, но и реальный синтез снизу вверх, за счет чего появляется возможность инкрементального синтеза, большей гибкости в выборе стиля проектирования. Специальные средства автоматического преобразования схем управления подачей синхросигналов позволяют учесть особенности реализации таких схем на базе FPGA. Упомянутые технологии могут быть легко адаптированы к новому направлению структурных ASIC. Сегодня, например, в системе DC FPGA уже поддерживается семейство StratixII компании Altera.

Рис. 8. Разворот RTL-описания до уровня базовых вентилей и переход к библиотечным элементам

## МОДУЛЬНЫЙ ПОДХОД И RTL-CUHTE3 (MODULE COMPILER, DESIGNWARE)

Применение модульного подхода и использование IP-блоков — краеугольный камень методологии проектирования современных систем-на-кристалле. С точки зрения задачи RTL-синтеза модульный подход, с одной стороны, позволяет значительно увеличить производительность за счет повторного использования результатов синтеза, но с другой — создает проблемы для оптимизации из-за ограничений, накладываемых структурой модуля. Обычная процедура синтеза с использованием модульного принципа состоит в выявлении однотипных фрагментов RTL-описания, однократного синтеза и подстановки результатов во все места, где были выявлены фрагменты данного типа. При оптимизации результатов синтеза структура модулей либо вообще не изменяется, либо допускается некоторая оптимизация "через границы модулей", которая требует полного или частичного разворота иерархии модулей и, соответсвенно,

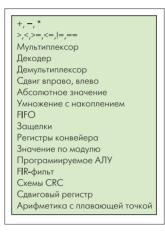

приводит к снижению производительности синтеза. В системе Module Compiler предлагается другой подход, который особенно эффективен при работе с системами обработки данных. Система сопровождается параметризованной библиотекой модулей для наиболее часто встречающихся операций (рис.9). При оптимизации проекта для каждого вхождения модуля, в зависимости от окружения, могут быть выбраны наиболее подходящие параметры. Такой параметрический подход оказывается более эффективным, чем оптимизация "через границы

Puc.9. Некоторые функции библиотеки DesignWare

модулей". Использование гибкого модульного подхода, основанного на технологии ModuleCompiler, эффективно также и при использовании крупных IP-блоков, поддержка которых осуществляется средствами библиотеки DesignWare.

Приведенный обзор технологий RTL-синтеза не претендует на всеобщность. В дальнейшем мы планируем возвращаться к обсуждению этой темы, поскольку RTL-синтез — инструмент, с которым разработчики цифровых микросхем работают постоянно и от которого в значительной степени зависит качество проекта. Понимание внутренних механизмов и технологий позволяет полнее использовать все возможности этого инструмента.