## АЦП С СИНХРОНИЗАЦИЕЙ ВЫХОДНЫХ **ЦИФРОВЫХ ПОТОКОВ**

## НОВОЕ РЕШЕНИЕ КОМПАНИИ NXP

Мори Вуд, Денис Кулон, Люк Джиоваччини, Юнес Фада, NXP Semiconductors

В сентябре 2011 года компания NXP Semiconductors представила ADC1443D – первый на рынке высокоскоростной аналоговоцифровой преобразователь (АЦП) с цифровым интерфейсом на базе SerDes, отвечающий требованиям стандарта JESD204B. Среди интегрированных возможностей этого устройства есть так называемая функция MDS (Multiple Device Synchronization – мультисинхронизация устройств). С функцией MDS компания NXP Semiconductors расширяет преимущества своей CGVxpressреализации интерфейса JEDEC JESD204B.

изайн ИС ADC1443D гарантирует согласование последовательных выводов JESD204B различных каналов нескольких АЦП в рамках одного устройства. Функция MDS, как следует из ее названия, обеспечивает новый системный уровень синхронизации за счет согласования множества устройств ADC1443D.

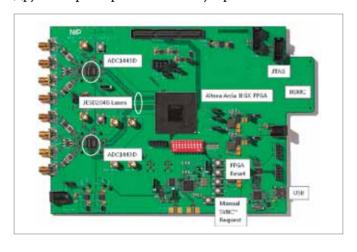

АЦП позволяет синхронизировать несколько (до 16 каналов) цифровых выходных потоков данных на уровне отсчета (сэмпла) и фазовой когерентности. Существует множество приложений с высокоскоростной цифровой обработкой сигнала, в которых синхронизация выборок данных желательна или даже необходима. Для линейки высокоскоростных преобразователей NXP Semiconductors предлагает оценочную плату с двумя ADC1443D (т.е. с четырьмя каналами АЦП) на базе ПЛИС Altera Arria II GX, специально предназначенную для демонстрации функции MDS (см. рисунок). Функция мультисинхронизации устройств на базе АЦП позволит разработчикам смешанных цифроаналоговых компонентов сэкономить время и сократить расходы на материалы.

**Характеристики АЦП.** ADC1443D - это двухканальный 14-разрядный АЦП со скоростью преобразования 200 Msps (млн. выборок в секунду), с типичным значением динамического диапазона, свободного от паразитных выбросов (SFDR - Spurious-Free Dynamic Range), 86 дБс и с двумя отвечающими требованиям стандарта JESD204B дорожками (lane), каждая из которых работает на скорости до 5 Гбит/с. Другие характеристики этого устройства:

Демонстрационная плата ADC1443DxxxW1/DB MDS

- набор функций NXP Semiconductors CGVxpress (развитие высокоскоростного последовательного интерфейса CGV), включая MDS и гарантированную совместимость с ПЛИС ведущих производителей отрасли;

- соответствие требованиям к подклассам 0, 1 и 2 (Device Subclass 0, 1 и 2) устройств JESD204B с поддержкой синхронизации гармоническим сигналом и детерминированными задержками;

- типичная ширина полосы входного аналогового сигнала 1 ГГц;

- типичное отношение сигнал-шум (SNR) 73 дБ;

- схема коррекции ошибок выходных данных, гарантирующая отсутствие потери данных (zero missing codes) во всем рабочем диапазоне:

- интерфейс SPI для управления конфигурациями (включая режимы сна и выключения питания) и мониторинга состояния (в том числе всесторонний контроль состояния интерфейса JESD204B);

- однополярное питание 1,8 В; типичное рассеяние мощности 1,0 Вт при частоте дискретизации (FS) 200 МГц;

- аттестовано для работы в промышленном диапазоне температур от -40°C до 85°C;

- поставляется в корпусе типа HLQFN56 размером 8×8 мм.

Проверка возможностей схемы помощью демонстрационной АЦП ADC1443DxxxW1/DB поставляется в трех вариантах, отличающихся частотой дискретизации ("ххх"): 125, 160 и 200 млн. выб./с. Для проверки возможностей MDS с помощью демонстрационной платы требуется два генератора аналоговых сигналов (например. Rohde & Schwarz SMA100A) для синтеза тестового входного сигнала FIN (4 МГц дифференциальная синусоида) и тактового сигнала дискретизации FS (100 МГц дифференциальная синусоида). Рекомендуется использовать полосовой фильтр (с центральной частотой 4 МГц) для частоты дискретизации FIN, чтобы обеспечить спектральную чистоту. Для доступа к плате по интерфейсу USB и для поддержки зонда JTAG требуется ПК (для программирования регистра управления SPI и регистра состояния в АЦП ADC1443Ds и ПЛИС Arria II GX). Зонд JTAG используется для программирования ПЛИС с помощью Altera Quartus II, а также для мониторинга внутренних сигналов ПЛИС с помощью встроенного

логического анализатора Altera SignalTap II. ПК также выполняет приложение National Instrument LabVIEW, созданное специалистами NXP Semiconductors (группа разработки приложений для высокоскоростных преобразователей компании предоставляет его квалифицированным пользователям). Благодаря приложению LabVIEW NXP HSDC ADC Acquisition Software можно управлять устройствами ADC1443D, вести их мониторинг, анализировать цифровой сигнал на выходе АЦП как по временным, так и по частотным параметрам. Для питания ADC1443DxxxW1/DB применяется стабилизированный 5-В источник.

Мультисинхронизацию устройств с помощью АЦП ADC1443D можно проводить в двух рабочих режимах. Как упоминалось выше, АЦП ADC1443D отвечает требованиям стандарта JESD204B для устройств подкласса 0, 1 и 2. Device Subclass 0, по существу, является режимом JESD204A с повышенной максимальной скоростью передачи данных (обычно 4,5 Гбит/с на двух дорожках для ADC1443D).

В режиме JESD204B Device Subclass 0 (и JESD204A) для синхронизации кодовых групп (Code Group Synchronization, CGS) сигнал SYNC~ подается с устройства RX (в данном примере – ПЛИС) на устройство ТХ (в данном примере ADC1443D). В режиме JESD204B Device Subclass 0 и JESD204A последовательность, определенная протоколом ILA (Initial Lane Alignment – начальное согласование дорожек), выполняется непосредственно после последовательности CGS с использованием заданных символов K28.0, K28.3 и K28.4 (для получения более подробной информации см. спецификацию JEDEC JESD204A).

В режиме Device Subclass 0 после включения демонстрационной платы производится конфигурирование АЦП, программирование и конфигурирование ПЛИС, а затем – сброс всех устройств. Устройство RX ПЛИС немедленно подает сигнал SYNC~, выполняется последовательность CGS, затем ILA. На демонстрационной плате имеется нажимная кнопка для подачи сигнала SYNC~ вручную (см. рисунок).

Приложение NXP Semiconductors LabVIEW позволяет проверить и сравнить фазы одного из двух каналов разных АЦП.

При использовании этого режима MDS необходимо минимизировать на уровне печатной платы относительный сдвиг по фазе между сигналом SYNC~ и синхронизирующими

сигналами фреймов на входе устройств АЦП. Слишком большой относительный сдвиг по фазе может привести к отмене (de-assertion) сигнала SYNC~ выборки/захвата на различных фронтах импульса фрейма, в результате два (или больше) АЦП в системе MDS будут иметь мультифреймы с разными (несогласованными) данными после выполнения последовательности ILA.

Мультисинхронизация устройств с АЦП ADC1443D доступна также в режиме JESD204B Device Subclass 2. В этом режиме нарастающий фронт (фронт отмены) сигнала SYNC~ (с логического устройства RX) используется для сброса локального счетчика мультифреймов LMFC (Local Multi-Frame Counter) во всех АЦП (устройства ТХ) в системе. В результате такого сброса внутренние генераторы тактовых импульсов во всей системе будут согласованы при условии, что относительный сдвиг по фазе между сигналами SYNC~, направленными нескольким АЦП, минимален.

Проверку работы функции MDS в режиме JESD204B Device Subclass 2 можно легко осуществить с помощью демонстрационной платы. После включения платы АЦП будут сконфигурированы для режима Device Subclass 2 с захватом сигнала SYNC~ при помощи автономного счетчика LMFC. На этом этапе можно проверить согласование фаз на двух выходах АЦП (снова сравнивая канал 0 АЦП 0 с каналом 0 АЦП 1) с помощью программного приложения NXP LabVIEW. Сдвиг фазы на выходе в этом состоянии случайный, так как АЦП получают сигналы POR (сброс по включению питания) в разные, хотя и незначительно отличающиеся, моменты времени. Активация, или "перевод в рабочее состояние" счетчика LMFC, приводит к сбросу обоих двухканальных АЦП. Затем пользователь подает запрос на синхронизацию (последовательность SYNC~) с ПЛИС при помощи нажимной кнопки на демонстрационной плате. Можно провести вторую проверку согласования фаз на выходе (последовательность SYNC~ естественным образом индуцирует ILA).

Имеется четыре способа проверки работы MDS в режиме Device Subclass 2:

- по фазовому сдвигу (в градусах) измеряется приложением LabVIEW (описано выше);

- посредством эхо-считывания значений соответствующих регистров SPI каждого устройства АЦП, позволяющего определить, на

- каком цикле LMFC сигнал SYNC~ был дискретизирован и подтвердить согласование счетчиков LMFC:

- с помощью анализатора логики Quartus II SignalTap II и эхо-считывания значений счетчиков задержки, встроенных в интерфейсную логику ПЛИС JESD204B для каждой дорожки (измеряется от момента отмены сигнала SYNC~ до первого символа, отличного от К28.5):

- путем вывода внутреннего сигнала LMFC через отладочный контакт на обоих АЦП, а также их относительной фазы и наблюдений на осциллографе.

Необходимо отметить, что, во-первых, функция MDS не изменяет детерминированные задержки в режиме JESD204B Subclass 2 для АЦП ADC1443D; во-вторых, задержки интерфейса ADC1443D не зависят от синхронизации захвата сигнала SYNC~.

Характеристики системы. Во множестве высокоскоростных системных приложений цифровой обработки сигналов синхронизация выборок АЦП обязательна. Например, OFDM (Orthogonal Frequency Division Multiplexing - мультиплексирование с ортогональным частотным разделением сигналов), цифровое радио, радары с синтезированной апертурой и системой формирования диаграммы направленности, автоматическое тестирование ИС, прецизионная квадратурная аппаратура, а также оборудование для широковещательной трансляции видео высокой четкости, например, ретрансляторы. Когерентность данных АЦП - типичное требование для систем с фазовой модуляцией, в которых невозможно восстановить данные о квадратуре (магнитуде и фазе, I и Q) для массива датчиков, если поступающие с них данные некогерентны по фазе. Современные радарные установки как небольшого размера (например, бортовые), так и крупные (например, аэродромные) развиваются в направлении AESA (Automatically Electronically Scanned Array - активный электронный сканирующий массив) с использованием систем формирования диаграммы направленности на базе цифрового сигнального процессора, состоящие из десятков, сотен или тысяч датчиков/АЦП. Очевидно, что эффективное формирование диаграммы направленности невозможно реализовать без фазовой когерентности подсистемы сбора данных.

С этой проблемой разработчики сталкиваются уже многие годы. Для ее решения обычно предлагались схемы синхронного сброса системы в сочетании с высокоточным управлением данными, синхронизацией и фазовым сдвигом управляющего сигнала, а также с исчерпывающим описанием и квалификационными испытаниями системы.

Функция MDS АЦП, реализованная в ADC1443D, впервые предоставляет средства системного уровня в рамках стандартной ИС. Обеспечив поддержку функции MDS в АЦП, компания NXP Semiconductors упростила создание систем обработки фазово-когерентных данных очень большого масштаба, причем, что важно, без дополнительных затрат на материалы.

Более того, возможность синхронизации выходов АЦП в совокупности с поддержкой стандарта JESD204B имеет большое преимущество – JESD204B существенно облегчает

применение устройства и снижает затраты на материалы за счет упрощения конструкции печатной платы и уменьшения ее размеров. Последовательный интерфейс JESD204B гарантирует дальность передачи между преобразователем данных (ТХ АЦП или RX ЦАП) и логическим устройством (RX или ТХ, ПЛИС или заказной ИС) до 20 см, что делает возможным создание крупногабаритных систем, например, больших радаров AESA. Цифровые ретрансляторы JESD204B (устройство RX, за которым следует ТХ, реализованные в виде ПЛИС или заказной ИС) позволяют увеличить это расстояние, а функция детерминированных задержек JESD204B дает возможность инженерам управлять задержками в системе.

Таким образом, функция MDS АЦП предоставляет мощный экономически эффективный стандартизированный системный подход к решению сложных проблем проектирования.