# РАСЧЕТ ВЕРОЯТНОСТИ

# ПРОРЫВНАЯ ТЕХНОЛОГИЯ БУДУЩЕГО

## ТЕХНОЛОГИЯ РАСЧЕТА ВЕРОЯТНОСТЕЙ

В 2006 году доктор наук из Массачусетского технологического института, одного из самых престижных учебных заведений США, Бен Вигода совместно с председателем правления компании Analog Devices Давидом Рейнольдсом) и основателем компании венчурного инвестирования Stata

В.Майская

Venture Partners, Рейем Статой организовали компанию Lyric Semiconductor. Сейчас Б.Вигода — генеральный директор компании, Д.Рейнольдс — вице-президент, ответственный за разработку новых изделий, и Р.Стата — председатель правления. Цель создания компании Lyric — реализация идей, изложенных в докторской диссертации Б.Вигоды «Аналоговые схемы непрерывного действия для статистической обработки сигнала» (Continuous-Time Analog Circuits for Statistical Signal Processing), которую он защитил в 2003 году, и разработка процессора, способного работать на основе принципов байесовской вероятности\*.

Разработки компании финансирует Управление перспективных разработок и исследований Министерства обороны США (DARPA) в объеме 18 млн. долл. Военное ведомство рассчитывает на то, что вероятностные процессоры окажутся полезными в системах машинного зрения и в комплексе противоракетной обороны, способном быстро выделять атакующие боеголовки среди ложных целей и помех. Поскольку новая технология явно выходит за рамки военных приложений, неудивительно, что компания Lyric получила еще 2 млн. долл. от венчурных компаний и частных инвесторов (основной инвестор — Stata Venture). Сегодня в компании работает 30 человек, а в ее портфеле — 50 заявок на патенты.

Традиционные процессоры работают на основе булевой логики. Однако многие задачи нельзя легко решать с помощью традиционной модели обработки данных. По мнению Рейнольдса, сегодня программные средства все в большей степени должны способствовать нахождению наиболее правдоподобного ответа (ответов) на возникшую задачу, т.е. определять вероятность события. К программным средствам этой категории относится большинство кодов извлечения информации, распознавания образов, моделирования/имитации, которые используются в самых разнообразных при-

$<sup>^*</sup>$  Принципы байесовской вероятности позволяют определять вероятность какоголибо события, имея лишь его косвенные подтверждения, которые могут быть неточны. Полученную вероятность можно уточнить на основе данных новых наблюдений.

ложениях, таких как поиск данных в Интернете, финансовое моделирование, анализ секвенирования геномов (определения первичной структуры макромолекул), распознавания речи, моделирования климата, обнаружения фальсификаций кредитных карт, блокировки спама. Традиционные компьютеры рассчитывают вероятность события уже несколько десятилетий. При этом основное внимание уделяется разработке языков программирования и алгоритмов, необходимых для выполнения этой задачи. Но при этом требуется существенное увеличение вычислительной мощности компьютеров. А это в свою очередь приводит к необходимости применения множества сложных микросхем, занимающих большую площадь, и к крупным затратам. В итоге эффективность таких расчетов невелика. Вот почему основатели компании Lyric пришли к выводу, что для получения оптимальных решений при расчете вероятностей необходимо изменить базовый элемент компьютера - логический вентиль.

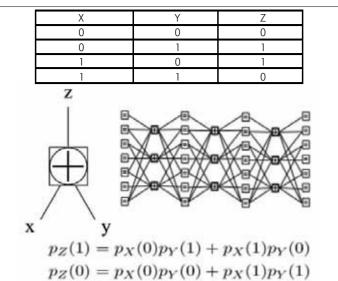

Согласно предложенной компанией технологии Probability Processing, для непосредственного представления (декодирования) вероятностей в виде напряжения или тока — в зависимости от используемой схемы (отрицательное решение — 0 В, положительное — напряжение питания  $V_{DD}$ ) — применяются так называемые аналоговые логические автоматы, которые выполняют расчеты в аналоговом домене с помощью аналоговых вероятностных разрядов (probability bits, pbits) и преобразующие выходные сигналы в цифровую форму.

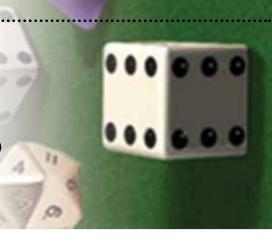

Для обработки таких вероятностных разрядов в качестве исходного логического элемента был выбран байесовский вероятностный вентиль NAND, который может иметь многочисленные соединения с другими подобными вентилями (рис.1). Построены вероятностные вентили на основе разработанных Б.Вигодой транзисторов-реостатов, действующих наподобие переключателей света фар. Число протекающих через такие транзисторы электронов соответствует вероятности того или иного события. Предложенные вероятностные вентили вместо последовательных вычислений выполняют сложные операции с многочисленными переменными параллельно. Как отмечает Вигода, вероятностный процессор представляет собой параллельно функционирующее устройство, в котором «множество фактов взаимодействует с множеством других фактов при решении задачи большой размерности».

И если в традиционном NAND-вентиле выходной уровень представляет логическую «1», когда два его входных уровня не совпадают, то выход вероятностного логического вентиля этого типа отображает возможность совпадения двух входных вероятностей. Таким образом, каждый вероятностный бит определяет не точное значение логического уровня, а лишь вероятность того, что он равен тому или иному значению между «0» и «1». В результате 100%-ной вероятности того, что pbit = 1, или prob(variable = 1) = 100%, соответствует

Рис. 1. Все переменные «разговаривают» друг с другом, по сути, в параллельном режиме

напряжение  $V_{DD}$ , а того, что prob(variable = 1) = 0% — нулевое напряжение. Но вместе с тем вероятностные NAND-вентили позволяют помимо значений напряжения или тока, соответствующих логическим «1» и «0», получать бесконечное множество других значений этих параметров. Цифровое разрешение pbit составляет 8 бит, т.е. они могут отображать  $2^8 = 256$  различных уровней напряжения (вероятностей) между 0 и  $V_{DD}$ . Подробности работы вентиля компания пока не раскрывает.

Чтобы продемонстрировать возможности вероятностных вентилей специалистами компании Lyric была разработана программа игры Судоки, итеративно определяющая вероятность нахождения того или иного числа в определенном квадрате. Вместо того, чтобы рассматривать множество возможных комбинаций цифр, вероятностный процессор принимает решения, исходя из основных правил игры (например, на одну линию нельзя дважды проставлять одно и то же число). В зависимости от сложности игры для решения поставленной задачи требуется 8—16 итераций. Решение аналогичной задачи с помощью обычного компьютера требует значительно больших затрат мощности и времени.

# ГДЕ ТЕХНОЛОГИЯ ОБРАБОТКИ ВЕРОЯТНОСТЕЙ НАЙДЕТ ПРИМЕНЕНИЕ?

Сегодня процесс обработки вероятности в первую очередь может найти применение для выявления шума радиочастотных сигналов и исправления ошибок памяти. Но это не единственные возможные области применения технологии компании Lyric. Вспомним об интернет-магазинах, где стоит задача предоставления товаров, способных заинтересовать покупателя. Фильтрация спама, выявление подделок кредитных карт и другие финансовые операции — также перспективные приложения устройств обработки вероятности. И, конечно, сложные алгоритмы расчета вероятности

востребованы крупными общественными организациями и финансовыми службами, не говоря уже о военных системах. И здесь вычислительные возможности вероятностного процессора, построенного на технологии компании Lyric, весьма перспективны. Так, по утверждению разработчиков, процессор на основе небольшого числа вероятностных вентилей с помощью нескольких специально разработанных команд сможет обрабатывать такой же объем информации, как и микросхема, содержащая 500 транзисторов. Система с тысячей подобных процессоров позволит значительно сэкономить электрическую энергию, что особенно актуально сегодня, когда потребляемая компьютерными средствами мощность и выделяемое ими тепло сдерживает дальнейшее развитие информационной технологии.

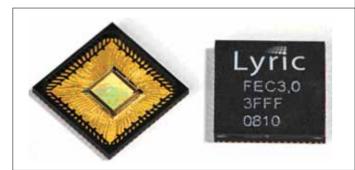

Вот почему компания Lyric уже в 2009 году начала разработку вероятностного процессора, опытные поставки которого намечены на 2013 год. Но для реализации намеченных планов компания с нуля должна создать специализированные, отличные от обычных схем процессора, микросхемы, которые позволят ей заработать средства, необходимые для создания программируемого вероятностного процессора. И первый коммерческий продукт — микросхема обнаружения и исправления ошибок схем памяти — уже готов к лицензированию.

#### СХЕМА ОБНАРУЖЕНИЯ И ИСПРАВЛЕНИЯ ОШИБОК ПАМЯТИ

Поскольку функция обнаружения и исправления ошибок памяти основана на оценке вероятности их возникновения, она легко может быть выполнена вероятностными вентилями, разработанными компанией Lyric. В современных микросхемах флеш-памяти, изготовленных по 30-нм технологии, при считывании на каждые 1000 хранимых в памяти бит приходится один неисправный, или «перевернутый», бит. По мере уменьшения топологических норм микросхем памяти до 20 нм один неисправный бит будет приходиться на 100 разрядов. Это значит, что размеры, сложность и стоимость контроллера, предназначенного для обнаружения и исправления ошибок, будут непрерывно возрастать, в результате чего перспективные средства исправления ошибок смогут применяться лишь в твердотельных накопителях высших моделей. И сегодня компания Lyric для решения проблем

Рис.2. LEC-микросхема обнаружения и исправления ошибок флешпамяти

обнаружения и исправления ошибок (Error Checking and Correction, ECC) флеш-памяти предлагает для лицензирования микросхему исправления ошибок Lyric (Lyric Error correction, LEC) второго поколения (рис.2). Микросхема изготовлена крупнейшим производителем микросхем — Taiwan Semiconductor Manufacturing Co. (TSMC) — по давно отработанной 180-нм технологии.

По данным Lyric, LEC-микросхема позволит создавать устройства обнаружения и исправления ошибок флеш-накопителей с производительностью до 6 Гбит/с. При этом такие устройства будут в 30—70 раз меньше эквивалентных цифровых ЕСС-схем, производительность которых составляет 1 Гбит/с. Они будут потреблять в 12 раз меньшую мощность, а их удельная, отнесенная к контакту ввода-вывода, производительность будет в четыре раза больше. Такая ЕСС-схема позволит увеличить производительность и срок службы флеш-памяти мобильных систем и серверов без нарушения хранимых данных. В итоге, по мнению разработчиков, LEСтехнология позволит снизить уровень ошибок флеш-памяти NAND-типа до 10-15.

LEC-технология компании Lyric Semiconductor получила награду конференции и саммита по флеш-памяти 2010 года (Flash Memory Summit 2010) в категории «Самые интересные инновационные технологии флеш-памяти».

Во втором квартале 2011 года компания планирует выпустить совместно с TSMC микросхему исправления ошибок третьего поколения LEC 3 также с 180-нм топологическими нормами, а в первом квартале 2012 — 65-нм микросхему четвертого поколения LEC 4. К концу 2011 года компания также планирует интегрировать LEC-ядро в микросхему флешпамяти NAND-типа, т.е. создать так называемую EZ NAND флеш-память. Правда, прежде чем LEC-технология получит массовое распространение, Lyric Semiconductor предстоит доказать ее надежность и масштабируемость.

Но наибольший выигрыш разработчики ожидают получить от реализации вероятностных процессоров.

# ПРОЦЕССОРЫ ОБРАБОТКИ ВЕРОЯТНОСТЕЙ

По утверждению специалистов компании Lyric, разрабатываемый процессор GP5, что значит General-Purpose Programmable Probability Processor (платформа универсального программируемого вероятностного процессора), в 1000х раз превзойдет по производительности современные процессоры компаний Intel и AMD. В случае успеха GP5 будет представлять собой пятый вид процессоров общего назначения в дополнение к центральным процессорам (CPU), сигнальным процессорам (DSP), графическим процессорам (GPU) и программируемым вентильным матрицам (FPGA). Каждый из этих процессоров обладает собственной архитектурой, логикой и языками программирования. Для обработки вероятностей пришлось оптимизировать архитектуру и логику процессора GP5, а

также разработать новый язык программирования PSBL (Probability Synthesis to Bayesian Logic, т.е. вероятностный синтез байесовской логики). Код, написанный на PSBL, будет запускаться на "родном" для него GP5. Представить первую версию PSBL планировалось в конце 2010 года, когда она будет лицензироваться для ограниченного круга партнеров. В четвертом квартале 2011 года компания намерена выпустить вторую версию языка — PSBL 2.0

По производительности процессор GP5 должен на три порядка превышать классические цифровые устройства с архитектурой х86. В тысячу раз уменьшатся мощность и стоимость комплексов, необходимых для выполнения статистических и вероятностных расчетов, т.е. одна микросхема компании Lyric заменит тысячу классических "камней". Полноценный вероятностный процессор GP5 должен быть представлен в 2013 году, хотя пока все технические характеристики будущей микросхемы не раскрываются. Предполагается, что процессор GP5, скорее всего, будет выпускаться в виде сопроцессора, подключаемого к компьютеру через интерфейс PCI Express, как многие графические и шифровальные процессоры. Это позволит быстро и эффективно решать широкий круг специализированных задач. На пути коммерциализации проекта Lyric придется решить множество проблем. Помимо разработки нового языка программирования, компания должна создать локальную память для хранения вероятностных битов, а также определить технический процесс изготовления как памяти, так и самого процессора.

Предназначен вероятностный процессор для систем обработки поисковых запросов, распознавания образов (например, в биометрии, для диагностики заболеваний), систем распознавания голоса, для определения кредитоспособности заемщиков и многих других задач. Вероятностный подход также поможет справиться с техническими задачами методами Монте-Карло с любой требуемой точностью решения.

Конечно, стоимость первых микросхем вероятностного процессора будет достаточно высокой, но в конечном итоге они найдут применение и в ПК. Первым потребителем GP5, естественно, станет DARPA.

Руководители Lyric хорошо знают, что земля усеяна "трупами" молодых микропроцессорных компаний, которые считали, что смогут успешно конкурировать с ведущими производителями — компаниями Intel и AMD. Самый яркий пример — компания Transmeta, основанная в 1995 году для создания процессоров, работающих с командными словами очень большой длины (VLIW) и потребляющих малую энергию. Компании пришлось прекратить разработку таких процессоров, но лишь после того, как ее основные конкуренты — Intel и AMD — обратились к решению проблемы уменьшения энергопотребления выпускаемых ими процессоров.

Сегодня на рынке появляются новые поставщики микросхем процессоров, которые рассчитывают воспользоваться возросшим интересом к системам виртуализации и облачных вычислений. Так, компания Tilera, которая уже поставляет на рынок процессоры с 36-ю и 64-мя ядрами, планирует выпустить в 2011 году микросхему с сотней ядер, а в 2013 году — микросхему с 200-ми ядрами. Компания также заключила контракт на производство комплектного оборудования (Original Design Manufacturing, ODM) с компанией Quanta Сотритет на разработку системы с 512-ю функционирующими ядрами в одной стойке. Но компания Lyric Semiconductor планирует поставлять комплексные решения для определенных сегментов рынка и рассчитывает на успех.

Lyric Semiconductor не единственная компания, разрабатывающая средства обработки вероятности. На Международной конференции по полупроводниковым схемам (ISSCC 2009) ученые Университета Райса продемонстрировали опытный образец микросхемы, выполненной на вероятностных КМОПтранзисторах (Probability-based Complementary Metal-Oxide Semiconductor, PCMOS).

## ВЕРОЯТНОСТНЫЕ РСМОЅ-УСТРОЙСТВА

Первоочередные требования в мире цифровой микроэлектроники — точность и отсутствие сбоев при обработке данных. На каждом этапе производства микросхем предусмотрено несколько этапов тестирования с целью гарантии того, что каждая микросхема всякий раз выдает точный результат. Но по мере уменьшения размеров кремниевых транзисторов возрастают их шум и потребляемая мощность. Разработчики решают проблему шума за счет увеличения рабочего напряжения, т.е. потребляемая микросхемой мощность растет. В результате специалисты приходят к выводу, что для создания робастных микросхем и архитектур с малым энергопотреблением на основе компонентов все меньших размеров следует отказаться от современных детерминистических структур в пользу вероятностных.

Этим можно объяснить интерес к работам группы исследователей Университета Райса и Института экологически дружественной нанотехнологии (Institute for sustainable nanoelectronics) при Технологическом университете Наньяна (Сингапур) под руководством профессора Кришны Палемы. В основе этих работ лежит мнение, что небольшие погрешности (или шум) не помешают работе микросхемы, особенно в приложениях, которые допускают такие погрешности вследствие ограниченности человеческого восприятия. К подобным приложениям относится обработка звука или изображения. PCMOS-vстройства также перспективны для выполнения операций шифрования данных, которые основаны на случайной генерации чисел. Согласно работам исследователей, использование возбуждаемого в схеме шума позволит создать устройства, которые смогут обеспечивать близкие к точным, а при определенных условиях - и точные результаты, что уже хорошо.

Рис. 3. Функции переключения одного бита: детерминистические (а) и их эквиваленты с вероятностью получения точного результата р (б)

В работе группы профессора Палемы, которую поддерживает DARPA и компания Intel, шум рассматривается не как фактор, препятствующий дальнейшему развитию полупроводниковой технологии в соответствии с законом Мура, а как источник сигнала, способствующий созданию микросхем и вычислительных платформ со сверхнизким энергопотреблением. В качестве основного элемента будущих микросхем вероятностной обработки данных предложен вероятностный ключ (или инвертор), реализующий переключение одного вероятностного разряда. Разработчики предположили, что четырем детерминистическим функциям переключения одного разряда (рис.За) соответствуют четыре вероятностных эквивалента (рис.3б) с явно выраженной вероятностью «истинности» переключения р, (в расчетах ученых Университета Райса -0.5 p < 1 и p = 1 при точном выполнении функции переключения современным цифровым устройством). Разработчики посчитали, что любую из этих четырех вероятностных функций переключения может выполнить вероятностный КМОП-переключатель (PCMOS-инвертор), на основе которого с помощью принятых вероятностных алгоритмов можно построить такие простейшие вентили булевой логики, как И, ИЛИ, НЕ.

Чтобы определить характеристики такого абстрактного переключателя и выяснить, можно ли построить на его основе стандартные блоки систем, работающих с вероятностными нагрузками, с помощью статистической термодинамики была определена энергия, потребляемая при выполнении функции переключения, и вероятность получения точного результата р. Анализ показал, что, во-первых, энергия, потребляемая вероятностным ключом при выполнении функции, экспоненциально возрастает с ростом р, т.е. чем выше вероятность получения точного результата, тем больше энергия, требуемая для его гарантированного получения, и наоборот. При относительно небольшой погрешности выполнения логической функции можно получить значительную экономию потребляемой энергии (выделяемого тепла). Эта зависимость получила название закона энергии—вероятности.

Во-вторых, при фиксированном значении вероятности получения точного результата наблюдается квадратичная зависимость потребляемой энергии от шума переключателя,

который определяется как среднеквадратическое значение напряжения  $\sigma$ . Чем выше шум прибора, тем больше потребляемая им при переключении энергия. Эта зависимость названа законом энергии—шума.

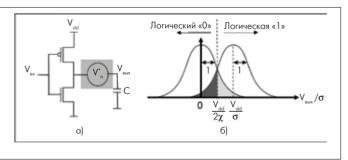

На основе полученных результатов анализа учеными Университета Райса была рассмотрена возможность создания вероятностных КМОП-переключателей, в выходное напряжение которых входило бы среднеквадратическое значение напряжения, вызванного тепловым шумом, шумом источника питания и шумом, обусловленным отклонениями топологических размеров элементов от норм в микросхемах, выполняемых по субмикронным технологиям (рис.4а). В таких переключателях выходное напряжение, нормализованное относительно значения напряжения шума  $V_{\text{вых}}/\sigma$ , может быть представлено в виде переменной с гауссовым распределением и дисперсией, равной 1. Среднее нормализованное значение выходного напряжения равно 0, если точный результат равен логической "1", и  $V_{\text{cd}}/\sigma$  ( $V_{\text{dd}}$  — значение напряжения питания) если точный результат логический "0" (рис.4б).

Чтобы выявить преимущество PCMOS-структур при реализации различных электронных устройств, сравнивались значения произведения энергии на производительность (Energy Performance Product, EPP) системы на основе PCMOS-инверторов и системы на основе процессора SA-1100 семейства StrongARM компании Digital Equipment. Обе системы выполняли вероятностные расчеты с помощью алгоритмов байесовской вероятности (Bayeson Inference, BN) и рандомизированной нейронной цепи (Randomized Neural Nentwork, RNN) (см. таблицу). Была показана возможность применения алгоритмов вероятностных расчетов в PCMOS-устройствах. И если для снижения энергопотребления функционального блока допустить погрешность некоторых его элементов, PCMOS-технология сможет способствовать дальнейшему масштабированию микроэлектронных устройств.

Для подтверждения своих выводов исследователями была предложена вероятностная система на кристалле, состоящая из двух основных блоков — хост-процессора, выполненного на основе обычного цифрового маломощного встроенного процессора, и сопроцессора, выполненного по PCMOS-тех-

Рис.4. PCMOS-ключ (а) и логические «0» и «1», представленные двумя кривыми с гауссовым распределением (заштрихованная область соответствует вероятности погрешности при переключении, т.е. 1-р) (б)

## Сравнение значений EPP для систем на основе PCMOS-инверторов и процессора SA-1100

| Алгоритм | Приложения                                                                                                                                    | Выигрыш в результате применения PCMOS-переключателя* |       |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------|-------|

|          |                                                                                                                                               | мин.                                                 | макс. |

| BN       | Спам-фильтр, средства планирования боевых действий, средство выявления дефектов принтера, аппаратура слежения за состоянием пациентов клиники | 3                                                    | 7,43  |

| RNN      | Классификация изображения и графики, оптимизация сложных проблем энергопотребления                                                            | 226,5                                                | 300   |

\*Выигрыш в результате применения PCMOS-переключателя  $\Gamma_{\rm I}$  =  $E_{\beta}$ - $T_{\beta}$ / $E_{\rm I}$ - $T_{\rm I}$ , где  $E_{\beta}$  — энергия системы на основе стандартной технологии,  $T_{\beta}$  — время переключения стандартной системы,  $E_{\rm I}$ -и  $T_{\rm I}$  — энергия и время переключения PCMOS-системы, соответственно.

нологии (рис.6). На Международной конференции по твердотельным схемам 2009 года (ISSCC 2009) была представлена опытная специализированная РСМОS-микросхема (ASIC), предназначенная для аппаратуры шифрования. Микросхема, разработка которой была начата в 2005 году, в сравнении с аналогами, выполненными на стандартных компонентах, потребляет в 30 раз меньше энергии при в семь раз большем быстродействии. К достоинствам РСМОS-микросхем относится и то, что они изготавливаются по хорошо отработанной КМОП-технологии. Поэтому их можно изготавливать с помощью существующего технологического оборудования (следует отметить, что моделирование возможностей РСМОS-инверторов проводилось на основе 0,25-мкм КМОП-микросхем компании TSMC).

По мнению ученых Университета Райса, PCMOS-схемы в первую очередь найдут применение в системах, где человеческое восприятие допускает неточности получаемой информации — в сотовых телефонах, лэптопах, устройствах обработки графического изображения и звука. При обработке изображения видеодатчика сотового телефона с помощью PCMOS-схемы малый размер экрана вкупе со способностью человека воспринимать несовершенное изображение приводит к тому, что он воспринимает изображение так же, как и

РЅОС Architecture

Вероятностный КМОП-сопроцессор

Блок управления памятью и сумматора/декодера

Память

<u>Puc.5. Архитектура вероятностной КМОП-системы на кристалле</u> (<u>PCMOS</u>)

при точной обработке. А возможность существенного уменьшения энергопотребления устройства обработки изображения позволит значительно продлить срок службы батарей и перезаряжать мобильный телефон не через несколько дней, а через несколько недель.

Сейчас разработчики изучают возможности применения PCMOS-технологии для схем обработки изображения сотовых телефонов и графических карт, а также в медицинских имплантатах. Коммерческая реализация разрабатываемых микросхем планируется на 2013 год.

Следует отметить, что вероятностная логика вошла в опубликованный специальным выпуском журнала Массачусетского технологического института Technology Review за 2008 год список десяти прорывных, еще "сырых" технологий, которые изменят Интернет, способы расчетов, медицину, энергетику и еще много чего. Как отметил руководитель Лаборатории микропроцессорных технологий компании Intel Шехар Боркар, переход от булевой логики к вероятностной можно считать выдающимся достижением. Если учесть энергетические и скоростные достоинства вероятностной логики, становится понятным ее значение для будущего науки, поскольку сегодня микроэлектроника уже достигает такой стадии развития, когда можно сказать: будущее за технологией обработки вероятности. Всегда есть люди, пытающиеся сделать невозможное, и время от времени им это удается, и на свет появляется новинка. Ждем 2013 год.