## ВСТРАИВАЕМЫЕ СИСТЕМЫ

## ИНТЕЛЛЕКТУАЛЬНЫЙ МИР МИКРОПРОЦЕССОРОВ И КОНТРОЛЛЕРОВ

Встраиваемые системы становятся катализатором процессов совершенствования вычислительных, коммуникационных, телекоммуникационных систем, промышленной и бытовой электроники, военных и аэрокосмических технологий. Они отвечают за работоспособность и выполняемые функции многих важнейших устройств - от средств автоматизации производства и сетевого оборудования до мобильных телефонов и бытовой аппаратуры. Сегодня наблюдается возрождение и быстрое развитие встраиваемых систем после огорчительных прошлых лет спада. Выбор между аппаратными и программными средствами, предлагаемыми различными компаниями, становится одной из труднейших задач, с которыми сталкиваются разработчики. Поэтому неудивителен интерес, вызванный прошедшими в начале года международными выставкой-конференцией Embedded World (13-15 февраля, Нюрнберг) и конференцией Embedded Systems Conference (3-7 апреля, Сан-Хосе, шт. Калифорния). Рассмотрим некоторые встраиваемые микропроцессоры и микроконтроллеры, представленные на этих встречах ведущих производителей и дистрибьюторов электронных компонентов и модулей, поставщиков техники и программного обеспечения для встраиваемых технологий.

Внимание участников и посетителей как выставки Embedded World, так и конференции Embedded Systems Conference (ESC), привлекло 32-бит процессорное ядро AVR32 компании Atmel с новой load/store RISC-архитектурой и возможностью исполнения 16- и 32-бит команд без режима переключения, а также DSP- и SIMD-команд. Новое процессорное ядро предназначено для встроенных приложений XXI века, основное требование которых — высокая производительность при малых энергозатратах. Действительно, по данным Консорциума EEMBC (EDN Embedded Microprocessor Вепсhmark Consortium), процессорное ядро AVR32 по производительности в три раза превосходит любой ближайший конкурент. Так, на тактовой частоте 100 МГц процессор AVR32 способен вы-

В.Шурыгина

полнить операцию декодирования фильма MPEG4-формата с 1/4 VGA-разрешением (формата, используемого различными малогабаритными видеоплеерами) со скоростью 30 кадров/с. Тактовая частота современных процессоров, необходимая для выполнения этой задачи, составляет 266 МГц. Для пользователя это в первую очередь означает больший срок жизни батареи. При повышении тактовой частоты до 400 МГц AVR32 сможет выполнять большее число задач и позволит исключить дополнительные процессоры или аппаратные акселераторы, что будет способствовать снижению стоимости аппаратуры при улучшении ее системотехники и надежности.

Высокой производительности процессорного ядра AVR32 разработчики компании Atmel добились за счет:

- уменьшения числа тактов, необходимых для загрузки регистра/хранения данных;

- максимального использования вычислительных ресурсов;

- выполнения переходов без потерь тактов;

- сокращения промахов кэша.

Кроме того, архитектура ядра предусматривает минимизацию как потребляемой в активном режиме мощности, так и токов утечки.

Процессор AVR32 работает с командами длиной в 1 байт (8 бит), в полуслово (16 бит), слово (32 бит) и в двойное слово (64 бит) в сочетании с адресной арифметикой с различными указателями, что обеспечивает эффективный доступ к таблицам, структурам данных и произвольным данным за минимально возможное число циклов. Пример такой новаторской команды — "загрузка с извлеченным индексом" (ld.w), которая позволяет сократить число тактов, требуемых для исполнения одного из самых широко используемых в криптографии алгоритмов — block chiper, с 14 (для современных процессоров) до семи. Всего у AVR32 28 команд, обеспечивающих увеличение эффективности операций загрузки/хранения.

Архитектура ядра AVR32 поддерживает SIMD-команды, позволяющие при обработке потока данных (например, для оценки движения при декодировании MPEG-данных) в четыре раза ускорить выполнение DSP-алгоритмов, требующих исполнения одной и той же команды.

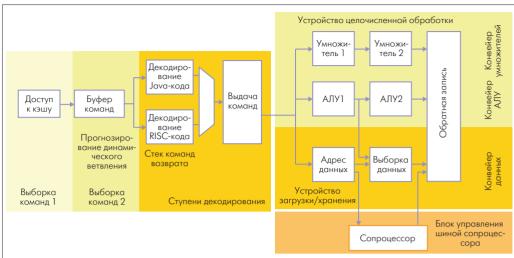

Конвейер ядра AVR32 содержит семь ступеней с тремя субконвейрами (операции умножения/управления доступом к среде передачи данных, загрузки/хранения и АЛУ), обеспечивающими переупорядоченное и параллельное исполнение имеющимися ресурсами арифметических действий с независимыми данными (рис.1). Логика обнаружения риска сбоя выявляет и удерживает зависимые команды в начале конвейера до завершения операции, от которой они зависят.

Перенос данных между ступенями конвейера позволяет исключить многие такты, затрачиваемые на запись и считывание регистровых файлов. Команды, заканчиваемые до достижения ступени повторной записи, сразу же пересылаются в начало конвейера, с тем чтобы началось исполнение команд, ждущих их результатов. Благодаря сокращению числа операций доступа к регистрам экономится не только число тактов на операцию, но и потребляемая ядром мошность.

Логика прогнозирования ветвлений в конвейере процессора AVR32 способна точно предска-

зать все команды изменения направления. К тому же, ветвления "складываются" с адресом команды. В результате для архитектуры AVR32 временные ограничения не столь критичны, как для других системных архитектур, функции динамического прогнозирования ветвления по существу могут реализовывать команды "с нулевой потерей такта на ветвление" и тем самым способствовать повышению производительности.

Набор команд процессорного ядра появился в ходе всестороннего сравнительного анализа его производительности методом прогона контрольных задач и доводки ядра совместно с поставщиком компилятора (IAR Systems). В итоге удалось увеличить плотность кода на 50% в сравнении с сопоставимыми 32-бит процессорами, работающими с программными пакетами ЕЕМВ. А это значит, что в кэше процессора может храниться большее число команд, что, в свою очередь, приводит к уменьшению промахов кэша и увеличению общей производительности устройства.

Архитектура ядра AVR32 поддерживает применение различных OC, в частности Linux.

За счет удержания данных вблизи процессора и минимизации операций их переноса обеспечивается дополнительная экономия энергопотребления на любой тактовой частоте. Так, благодаря включению в регистровый файл микроконтроллера регистра связи исключена операция копирования обратного адреса вызова стека памяти. Еще одна особенность процессора, позволяющая экономить энергозатраты, — размещение регистра статуса и обратного адреса прерываний и исключений в системных регистрах вместо передачи и извлечения данных из стека.

Появившиеся 10 лет назад 8-бит RISC-микроконтроллеры семейства AVR успешно конкурируют с уже существующими 8-бит микроконтроллерами и стали популярной маломощной их альтернативой. Та же участь уготовлена и семейству процессорных ядер AVR32.

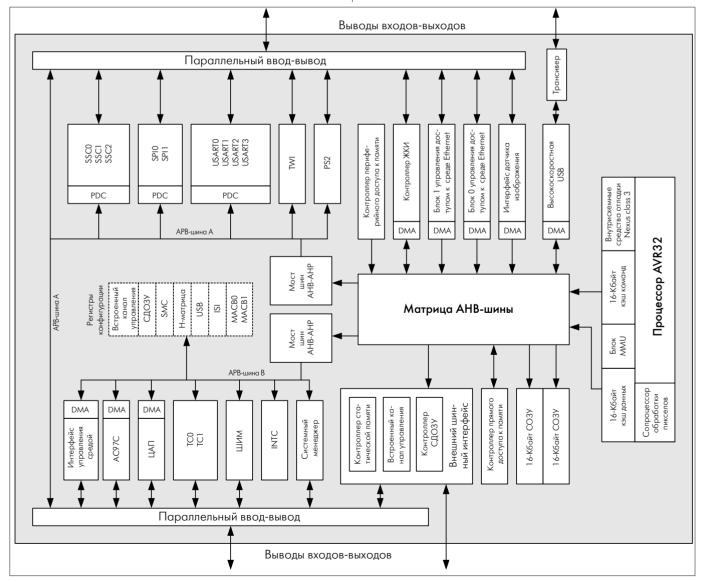

Об этом свидетельствует и представленный компанией Atmel на конференции ESC первый 32-бит сигнальный микроконтроллер на основе процессорного ядра AVR32 семейства AP7000. На кристалле объединены все функции, требуемые для реализации мультимедийных мобильных телефонов, цифровых видеокамер, карманных компьютеров, автомобильных электронных комплексов, телевизионных абонентских приставок и домашних развлекательных устройств, а также для сетевых коммутаторов/маршрутизаторов и принтеров. В микросхему контроллера входят:

сопроцессор обработки пикселов, подсоединенный к процессорному ядру AVR32 с помощью шины блока управления зада-

Рис. 1. Блок-схема процессорного ядра AVR32

- чей. Сопроцессор позволяет ускорить преобразование цветового пространства изображения, а также выполняет функции фильтрации/прореживания видеоданных;

- 32-Кбайт СОЗУ, выполненное в виде двух блоков емкостью 16 Кбайт каждый, с возможностью выборки за один такт при полной скорости передачи шины данных. При использовании в приложениях, требующих большего объема памяти, возможно подключение внешнего 16-бит СОЗУ. Дополнительный контроллер обеспечивает доступ к синхронному ДОЗУ и к любой стандартной энергонезависимой памяти;

- контроллер прямого доступа к памяти, позволяющий пересылать данные между периферийными устройствами и памятью без вмешательства процессора;

- периферийные устройства, в том числе 16-бит стерео-аудио ЦАП, контроллеры ЖКИ с разрешением 2048х2048 пикселов, порт USB 2.0 со скоростью передачи 480 Мбит/с и с выполненными на кристалле трансиверами (что позволяет исключить необходимость применения внешнего USB-контроллера), два контроллера доступа к сети 10/100 Ethernet, интерфейсы, поддерживающие практически все протоколы последовательной связи (рис.2).

Многослойная быстродействующая шинная архитектура АР7000 позволяет выполнять несколько операций параллельно. Кроме того, благодаря двум периферийным шинным мостам можно задавать различные тактовые частоты для периферийных устройств, отличающихся быстродействием. Алгоритмы динамичного изменения частоты устанавливают наименьшее значение частоты тактовых импульсов для конкретной исполняемой функции.

Благодаря используемым в ядре AVR32 и микросхеме контроллера AP7000 средствам снижения потребляемой мощности при выполнении рассмотренной выше операции декодирования фильма MPEG4-формата мощность, потребляемая контроллером, составляет всего 250 мВт. В начале апреля компания Atmel сообщила о готовности начать поставки первой микросхемы нового семейства — AP32A37000 в корпусе с матричным расположением 256 шариковых выводов.

На конференции ESC компания Atmel сообщила и о результатах десятилетних исследований проблемы снижения энергозатрат портативных устройств с батарейным питанием — о технологии рісоРоwer, используемой в микроконтроллерах семейств AVR. Возможности технологии приведены в докладе, посвященном разработке 8-бит AVR-микроконтроллеров с уровнем потребляемого тока

340 мкА в активном режиме, 150 мкА в режиме ожидания (на частоте 1 МГц), 650 нА в экономичном режиме и 100 нА в режиме пониженного потребления энергии. Микроконтроллеры предназначены для средств управления осветительными системами, средств безопасности, дистанционного открывания дверей и других устройств, которые большую часть срока эксплуатации находятся в режиме ожидания. Снижение энергозатрат достигнуто за счет запатентованного процесса изготовления и введения следующих инноваций:

- кристаллического генератора на частоту 32 кГц с потребляемым током 300 нА для реализации часов реального времени;

- блока регистрации падения напряжения ниже допустимого уровня, автоматически отключаемого в режиме ожидания и повторно включаемого в активном режиме микросхемы. Блок обеспечивает точную регистрацию падения напряжения при значениях напряжения питания 1,8; 2,7 и 4,5 В, его время отклика 2 мкс;

- регистра снижения потребляемой мощности, блокирующего передачу тактового сигнала блокам неиспользуемых периферийных устройств. Отключение одного периферийного модуля позволяет на 5–10% снизить потребляемую в активном режиме мощность и на 10–20% мощность, расходуемую в режиме ожидания;

- специализированного регистра блокировки ввода аналогового сигнала, обеспечивающего с помощью программных средств отключение буферов входов, используемых для считывания АЦП;

- техники управления пропусканием тактовых импульсов, позволяющей замораживать состояние периферийных временно неработающих устройств;

- техники опроса флэш-памяти, способной в течение нескольких наносекунд опросить содержимое флэш-матрицы и немедленно отключить память, благодаря чему существенно снижаются токи утечки.

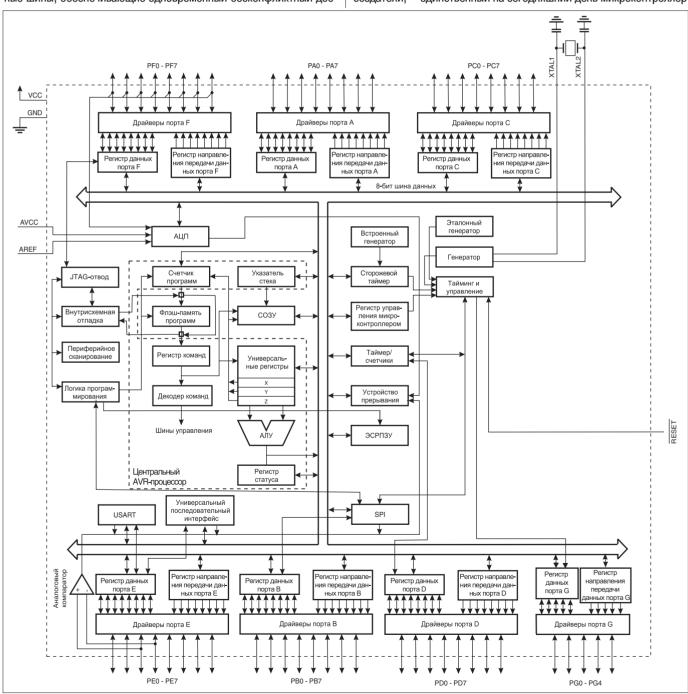

В марте Atmel сообщила о выпуске первых двух микросхем по этой технологии — Atmega169P (контроллер ЖКИ с разрешением 4x25 сегментов) в 64-выводном корпусе типа QFN и Atmega165P (универсальный микроконтроллер) в 64-выводном корпусе типа TQFP. Оба микроконтроллера имеют флэш-память емкостью 16 Кбайт, ЭСРПЗУ емкостью 512 байт и COЗУ емкостью 1 Кбайт; 10-бит АЦП; USART, SPI и двухпроводные интерфейсы (рис.3). Работают от источника питания на напряжение 1,8—5,5 В с производительностью до 16 mips. К марту 2007 года компания добавит к семейству рісоРоwer еще 14 микроконтроллеров, совместимых по разводке выводов и коду с уже представленными на рынке AVR-микроконтроллерами. Выполненные по этой технологии микросхемы получат в конце маркировки букву "Р".

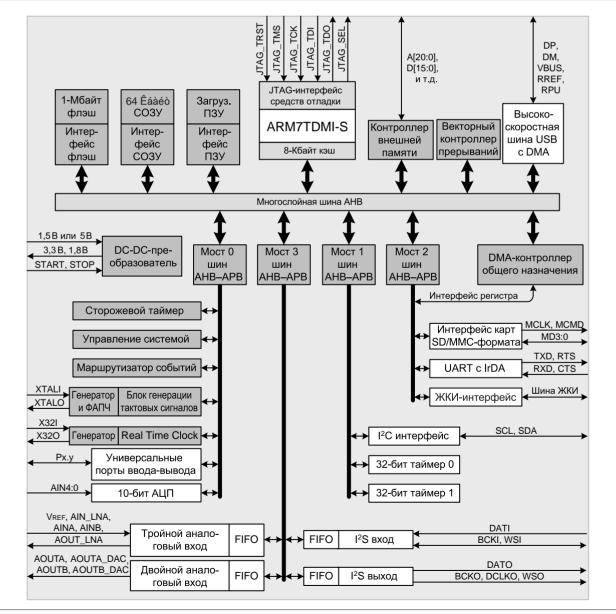

Но не едиными микроконтроллерами фирмы Atmel славна конференция-выставка ESC. Внимание ее участников привлекли и новые микроконтроллеры **Philips Semiconductor** — серии LPC2800

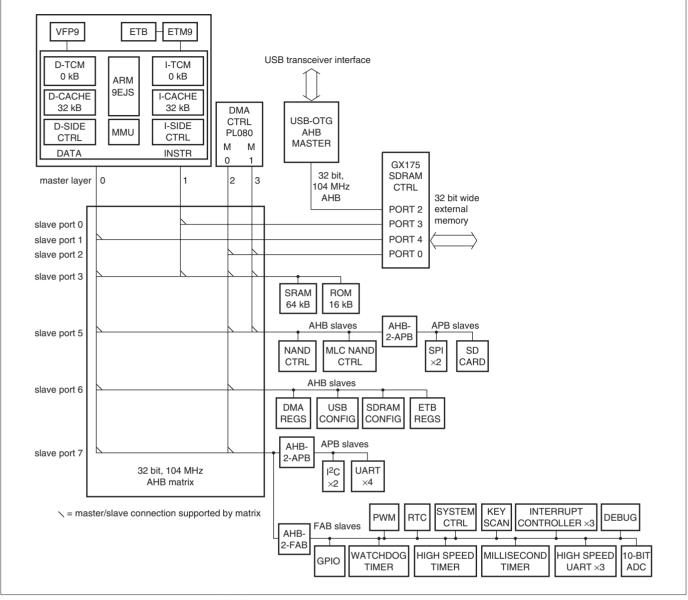

Рис. 2. Блок-схема сигнального микроконтроллера АР7000

на основе ядра ARM7, рассчитанные на питание от одной батареи на напряжение 1,5 В, через USB-порт или от внешнего источника (рис.4), и серии LPC3000 на основе ядра ARM926EJ (рис.5), предоставивший мультимедийным приложениям возможность векторной обработки данных. По утверждению разработчиков, LPC2800 — на сегодняшний день самый развитый микроконтроллер из всех представленных на рынке устройств на базе ядра ARM7. Это первый максимально соответствующий действующим стандартам ARM7-микроконтроллер с USB 2.0 портом и с внутрисхемным быстродействующим (480 Мбит/с) трансивером.

В состав микросхем серии LPC2800 помимо ядра ARM7TDMI на частоту 60 МГц входят многие высокопроизводительные устройства, упрощающие проектирование систем на базе этих микроконтроллеров. Это и 8-Кбайт кэш ядра и 1-Мбайт флэш-память программ, CO3У емкостью 64 Кбайт, многочисленные внутрисхемные шины, обеспечивающие одновременный бесконфликтный дос-

туп к памяти и выполнение программ, хранимых во флэше; внутрисхемный DC-DC-преобразователь, позволяющий подавать требуемое напряжение при питании от единичной батареи или через USB-порт; 16-бит  $\Sigma$ - $\Delta$  АЦП с мультиплексируемым пятиканальным входом.

Эти свойства микроконтроллеров серии LPC2800 позволят разработчикам встраиваемых систем при минимальных затратах вводить дополнительные возможности в периферию ПК, в смарт-карты SD-формата, считывающие устройства смарт-карт и другие USB-устройства с батарейным питанием. Микроконтроллеры серии поставляются в 180-выводных корпусах TFBGA-типа размером 10х10 мм. Технологию рісоРоwer намерены поддержать несколько изготовителей инструментальных средств проектирования.

32-бит микроконтроллер семейства LPC3000 компании — LPC3180, выполненный по 90-нм технологии, как утверждают его создатели, — единственный на сегодняшний день микроконтроллер

<u>Рис.3. Блок-схема микроконтроллера Atmega 165P</u>

на основе ядра ARM925EJ-S с векторным процессором обработки данных с плавающей запятой. Кроме того, он отличается большим набором стандартной периферии, включая шину USB On-The-Go (OTG), и возможностью работы в режиме сверхмалой потребляемой мощности при напряжении 0,9 В. Векторный процессор обработки чисел с плавающей запятой позволяет ускорить типичные расчеты в скалярном режиме в четыре-пять раз и в значительно большее число раз — в векторном режиме. LPC3180 — первый ARM9-микроконтроллер серии с USB OTG, позволяющим непосредственно подключаться к карманному компьютеру, считывателю смарт-карт и принтеру.

В число периферийных устройств на кристалле входят семь UART, последовательные интерфейсы SPI, I<sup>2</sup>C, часы реального времени с отдельным отсчетом времени питания, контроллеры флэш NAND-типа и DDR ОЗУ. Рабочая частота LPC3180 составляет 208 МГц, благодаря чему этот микроконтроллер перспективен для применения в таких высокоточных устройствах, как кассовые терминалы, медицинское и промышленное оборудование, GSP-системы, робототехнические системы. Блок ММU поддерживает основные операционные системы, в том числе и Linux — основную ОС

встроенных устройств. Благодаря наличию внутрисхемного сопроцессора обработки байт-кода микроконтроллер перспективен для применения в средствах безопасности и подтверждения подлинности. Смонтирован микроконтроллер в 320-выводной корпус LFBGA-типа.

На выставке Embedded World компания 2006 Philips демонстрировала макетную плату на основе LPC3180 с ОС Lunix.

Не остается в стороне от борьбы за первенство на рынке встраиваемых устройств и компания MIPS Technologies, представившая на конференции ESC семейство процессоров MIPS32 34К. Выполненное по 90-нм технологии 32-бит синтезируемое процессорное ядро с MIPS32 v.2 архитектурой и девятиступенным многопотоковым конвейером с возможностью DSP-обработки, присущей предыдущему поколению процессорных ядер семейства MPIS24K, содержит несколько виртуальных аппаратных средств обработки данных, а также такие опции, как средства гарантированного качества обслуживания (QoS), межпотоковой связи, обработки данных с плавающей запятой.

В ядре 34К удалось скрыть эффект ожидания доступа, характерный для однопотоковых процессоров, за счет более интенсивного

Рис.4. Блок-схема ARM- микроконтроллеров LPC2880/2888

Рис.5. Блок-схема ARM-микроконтроллера LPC3180

использования его мощностей. При останове одного потока в конвейер сразу же поступают дополнительные потоки. Пользователи могут выделять специализированный высокопроизводительный ресурс для обработки данных в реальном времени, обеспечивая QoS. Программа QoSLogic постоянно контролирует выполнение тредов и корректирует действия, с тем чтобы поддержать или предвосхитить требуемые действия в реальном времени.

Процессор 34К может быть конфигурирован в виде одного или двух виртуальных процессорных элементов (Virtual Processor Element — VPE), содержащих до пяти блоков контекста треда (Thread Context — TC). VPE можно описать как представление "видимых" только операционной системе состояний архитектуры, а ТС — как реализованные аппаратными средствами модели прикладного программирования задач конечного пользователя. VPE и ТС совместно пользуются всеми элементами, формирующими полный набор свойств процессора (логическими устройствами, конвейером, кэшами). Конкретное приложение и ОС воспринимают каждый VPE и ТС как полнофункциональный центральный процессор, способный одновременно выполнять программы нескольких ОС, а также до пяти тредов. Такая структура позволяет существенно сократить число неудачных обращений к кэшу, справляясь с восемью ожидающими

выполнения операциями загрузки. В случае неудачного обращения процессор может перейти к другому ТС-блоку и заполнить "пустой" такт конвейера.

Процессорное ядро может работать с двумя независимыми ОС или с ОС симметричной многопроцессорной системы.

Основные достоинства процессорных ядер семейства 34К: низкая стоимость, малые потребляемая мощность и общая площадь системы на кристалле на базе этого процессора, при сохранении совместимости с программными средствами существующих приложений без дополнительных издержек. Процессорное ядро на частоту 500 МГц занимает площадь 2,1 мм². Потребляемая мощность составляет 0,56 мВт/МГц при напряжении питания 1 В. Первоначальные эталонные испытания показали, что при обработке только двух потоков быстродействие процессора по сравнению с однопотоковым процессором возрастает на 60%, при этом размер ядра увеличивается лишь на 14%.

Гибкость ядер семейства 34К многопотоковой обработки делает их перспективными для применения в самых разнообразных устройствах: от систем IP-телефонии, цифровых телевизоров и DVD-рекордеров до цифровых камер, мобильных карманных приборов и портативных медиаплееров. Применение многопотокового ядра 34К по-

зволит объединить несколько однопотоковых функций в одном ядре, например функций хост-процессора, работающего с ОС Linux, и DSP с ОС RTOS. Компания MIPS Technologies уже объявила о предоставлении лицензий нескольким фирмам, в том числе с iVivity, Mobiley и PMC-Sierra.

Несмотря на интенсивные разработки 32-бит встраиваемых процессоров. 8- и 16-бит устройства по-прежнему широко представлены на рынке, и перспективы их развития оцениваются высоко. Поэтому усилия поставщиков таких изделий направлены на снижение их стоимости, расширение функциональных возможностей и повышение производительности. На секции 8- и 16-бит процессоров конференции ESC столкнулись микроконтроллеры гиганта полупроводниковой промышленности Texas Instruments. "крошечной" в сравнении с ним Rabbit Semiconductor и занимающей промежуточное положение компании Dallas Semiconductor/Maxim. Фирма Texas Instruments представила микроконтроллер смешанного сигнала со сверхнизким энергопотреблением серии MSP430F20xx\*. Потребляемый ток микроконтроллеров серии в активном режиме при напряжении питания 2,2 В и тактовой частоте 1 МГц составляет 220 мкА, в режиме ожидания – 0,5 мкА и в нерабочем режиме – 0,1 мкА. Микросхема содержит 16-бит RISC-процессор с временем исполнения команды менее 62,5 нс, 16-бит регистры, 16-бит таймер, генераторы постоянных величин. Генератор с цифровым управлением позволяет перейти из состояния ожидания в рабочий режим менее чем за 1 мкс. Монтируются в 14-выводные корпуса типа TSSOP или PDIP и в 16-выводной корпус QFN-типа. Предназначены микроконтроллеры серии для сенсорных систем сбора аналоговых сигналов, преобразования их в цифровую форму для воспроизведения или передачи хост-устройству, а также в интерфейсах автономных ВЧ-датчиков.

Компания Rabbit Semiconductor доложила о 8- и 16-бит микропроцессорах семейства Rabbit. Новейший представитель семейства, Rabbit 4000, - это высокопроизводительный 16-бит микропроцессор, в котором практически исключены проблемы, связанные с электромагнитными помехами. Это обеспечивают такие средства, как внутрисхемное устройство изменения режима работы задающего генератора частоты, блок управления пропусканием тактовых имрульсов для предотвращения синхронизации недействующих регистров, а также раздельные выводы подачи питания ядра и портов ввода-вывода. Микрокпроцесср, как и предыдущие процессоры Rabbit 3000 и 2000, предназначен для встраиваемых систем управления, связи и средств подключения к сети Ethernet. Rabbit 4000 работает на частоте 60 МГц с компактным кодом. В его состав входят 24-бит адресная шина, 8- или 16-бит шина данных, две шины выбора элемента памяти, две шины разрешенного выхода и три шины разрешенной записи, которые могут непосредственно взаимодействовать с несколькими (до шести) устройствами флэш-памяти или СОЗУ. Встроенный подчиненный порт позволяет применять микросхему Rabbit 4000 в ведущих и ведомых многопроцессорных системах. При этом специализированным процессорам могут назначаться отдельные независимые задачи. Микросхема содержит пять 8-бит параллельных портов (общее число входов-выходов – 40), шесть последовательных портов, совместимых с сигналами КМОП-устройств. Все шесть портов могут быть конфигурированы как порты IrDA-стандарта и, кроме того, четыре из них как SPI-порты, а два - как SDLC/HDLC-порты. Напряжение питания микропроцессора - 3,3 В, но возможна работа и при напряжении 1,8 В. Поставляется в 128-выводных корпусах TQFP и TFBGA,

отвечающих требованиям директивы защиты окружающей среды RoHS.

Микроконтроллер MAXQ3120 компании Dallas Semiconductor/ Maxim — высокопроизводительный 16-бит микроконтроллер смешанной обработки с 16-бит  $\Sigma$ - $\Delta$  АЦП, ЖКИ-интерфейсом, поддерживающим разрешение до 112 сегментов изображения, и модулем реального времени со специальным блоком резервного батарейного питания. Максимальная тактовая частота прибора составляет 8 МГц при напряжении питания 3,3 В. Основное назначение микроконтроллера — системы измерения однофазного электричества, хотя возможно и применение в портативных устройствах с батарейным питанием, в электрохимических и оптических датчиках и т.п.

О планах развития совместимых вариантов 8- и 32-бит процессоров старших моделей для промышленного и бытового секторов рынка доложила компания Freescale Semiconductor. Эти планы компании соответствуют современным тенденциям в области защиты ассигнований на разработку программных средств за счет выпуска совместимых по software микросхем микроконтроллеров и DSP низших и высших моделей. Планируемые к выпуску в конце 2006 года микросхемы должны "связать" 8- и 32-бит изделия. В рамках более близких планов компания создала дешевое 8-бит ядро RS08 с быстродействием 10 mips, предназначенное для 8-бит контроллеров, которые должны были появиться на рынке весной этого года. Цена ядра – не более 50 центов (сейчас 8-бит контроллеры компании стоят до 5 долл.). Контроллеры RS08 имеют ту же структуру шин, что и более дорогие 8-бит микроконтроллеры семейства 9S08, благодаря чему они совместимы с их внешними устройствами памяти и периферией. Однако они будут работать с сокращенным набором команд, присущим микросхемам меньших размеров. Ряд функций заменен более простыми, которые, тем не менее для большинства встроенных приложений, обеспечивают компактное кодирование.

Компания Freescale продолжит разработку 16-бит контроллеров ColdFire для автомобильной электроники. Быстродействие 32-бит микроконтроллеров семейства низших моделей, которые должны появиться на рынке в конце года, составляет 20—50 mips. Контроллер выполнен на базе той же периферии и памяти, что и RS08. Обе микросхемы изготовлены по 0,25-мкм технологии.

Объем статьи не позволяет полностью рассмотреть все представленные на ESC доклады, посвященные новым встраиваемым микропроцессорам и контроллерам, в том числе новейшим двухъядерным 64-бит процессорам компаний Intel и AMD, а также описанию предложенной фирмой Texas Instruments технологии Да Винчи (DaVinci). Эта технология, объединяющая ARM- и DSP-ядра, по утверждению ее разработчиков, служит фундаментом для грядущей революции в области цифровой видеотехники, сочетая опыт создания процессоров, средств проектирования, программных средств и систем при разработке цифровой видео- и аудиотехники.

Не меньший интерес вызвали экспонаты проходившей ранее в Нюрнберге выставки Embedded World, в работе которой приняли участие около 500 экспонентов из 27 стран мира. Несомненно, внимание привлекли три новые микрсхемы компании Intel, выполненные по 90-нм технологии, — Pentium M760 с 2-Мбайт кэшем и 400-МГц входной шиной, Cleleron M370 и Celeron M373 с ультранизким напряжением питания, а также чипсет базовой логики Intel 915GM Express для карманных ПК. Чипсет обеспечивает двукратное, в сравнении с предшествующим чипсетом Intel 855GME, увеличение производительности графических устройств. Он отвечает требованиям новой версии спецификации High Definition Audio на высококачественное аудиовоспроизведение. Поддерживает

<sup>\*</sup> Лапин.А. Новое поколение изделий компании Texas Instruments для управляемого электропривода. — ЭЛЕКТРОНИКА: HTБ, 2005, №6, с.28–32.

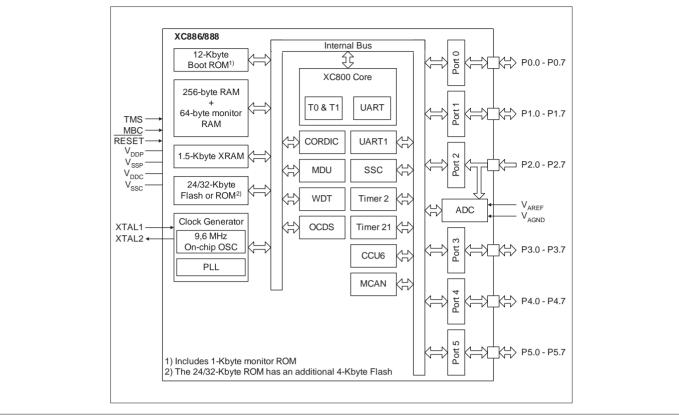

Рис. 6. Блок-схема микроконтроллера XC88xCLM

до 2 Гбайт DDR2 системной памяти, что в сравнении с DDR памятью позволяет на 60% повысить максимальную пропускную способность памяти при меньших энергозатратах.

Очевидно, демонстрация процессоров и чипсета — ответ компании Intel на продвижение на рынок процессоров семейства Geode ее вечного соперника — компании AMD. А из сообщения фирмы IBM, объявившей о готовности выпустить на рынок серверы, построенные на чипсете Hurricane, поддерживающем новое поколение двухъядерных 64-бит процессоров Intel Cranford, можно сделать вывод о том, Intel не собирается уступить AMD ни пяди рынка серверных процессоров.

На выставке Embedded World не было недостатка в новых разработах. Компания **Infineon Technologies**, занимающая четвертое место на рынке полупроводниковых изделий для промышленных приложений, экспонировала новые 8-бит микроконтроллеры семейства XC800, 16-бит устройства семейства XC166 и 32-бит флэш-микроконтроллеры семейства TriCore с оптимизированными для промышленных приложений характеристиками. Специалисты компании утверждают, что представленные микросхемы позволят снизить стоимость систем, в которых они используются, на 40%. К тому же, применение электронных средств управления электроприводом приведет не только к повышению их надежности, но и к экономии энергопотребления (до 20%).

Микроконтроллеры XC886/888 CLM с выполненным на кристалле CAN-контроллером и блоком поддержки локальной сети межсоединений (LIN) отличаются улучшенными характеристиками (рис.6). Внутрисхемный CAN-модуль выполняет большинство функций, задаваемых сетевым протоколом, тем самым уменьшая нагрузку процессора. В состав микросхем XC886/888 CLM, построенных на базе стандартной 8051 архитектуры, входят такие ключевые блоки, как встроенная флэш-память емкостью 32 Кбайт, "интеллигентный" ШИМ-модуль, быстродействующий высокоточный 10-бит АЦП, блок

реализации CORDIC-алгоритмов и блок умножения/деления (Multiplication Division Unit — MDU). Монтируются микросхемы в 48- и 64-выводные корпуса типа PG-TQFP, отвечающие требованиям директивы RoHS. Помимо систем управления электроприводом, микроконтроллеры XC886/888 CLM находят применение в различных сетевых автомобильных, промышленных, сельскохозяйственных CANсистемах, системах управления лифтами и эскалаторами и т.п.

Перспективна для применения в промышленных установках и электронных блоках автомобилей 32-бит система на кристалле семейства BlueStreak компании **Sharp**. Экспонировавшиеся микросхемы семейства — LH7A400 и LH7A404, выполненные на базе RISC-процессора ARM922T, рассчитаны на работу в промышленном диапазоне температур -40..85°C. Микросхемы содержат также 16-Кбайт кэш, CO3У, блок управления памятью, контроллер цветного ЖКИ с блоком поддержки сенсорного ввода. Работают микросхемы на частоте 245—266 МГц.

Нельзя не отметить и получившую награду выставки Embedded World серию "самых маленьких в мире" микроконтроллеров K\_Line компании **NEC Electronics**. В серию входят 68 различных приборов в корпусах пяти типов. Быстродействие микроконтроллеров серии лежит в диапазоне от 3 до 20 mips в зависимости от разрядности устройства: 8 или 32 бит. Микросхема наименьших размеров с флэш-памятью емкостью 1 Кбайт смонтирована в корпус WCSP-типа с шариковыми контактами размером 1,9x2,2 мм, самый большой контроллер с флэш-памятью 256 Кбайт — в 144-выводной корпус TQFP размером 20x20 мм.

Безусловно, в одной статье нельзя объять необъятное и рассмотреть все hardware и software, обсуждавшиеся и экспонировавшиеся на этих двух крупнейших мировых выставках-конференциях. Вопросы и проблемы развития столь перспективной технологии, как встроенные системы, будут освещены в последующих номерах журнала. Добро пожаловать в этот разумный, разумный, разумный мир!

## Совет главных конструкторов по техническим средствам волоконно-оптических систем передачи (СГК ВОСП) объявляет о проведении очередного заседания **14—15 июня 2006 г**. на тему **"Аппаратура оконечного доступа"**.

СГК ВОСП создан в соответствии с Решением секции №5 НТС Комиссии Правительства РФ по военно-промышленным вопросам и президиума НТС Российского агентства по системам управления от 29 августа 2000 года. Цель создания СГК ВОСП — решение перспективных задач разработки, производства и внедрения технических средств волоконно-оптических систем передачи двойного применения с учетом развития взаимоувязанной сети связи РФ.

С момента образования СГК ВОСП 1 декабря 2000 г. проведено девять заседаний, на которых обсуждались первоочередные вопросы состояния и перспективы развития волоконно-оптических систем передачи и их элементной базы. Отдельные предложения СГК ВОСП были использованы РАСУ и УРЭП и СУ при формировании разделов Федеральных целевых программ (ФЦП). Обсуждаемые на заседаниях СГК ВОСП вопросы в ряде случаев выходят за рамки интересов УРЭП и СУ, что привлекает внимание со стороны представителей других ведомств к его работе.

К компетенции СГК ВОСП относятся:

- Обсуждение первоочередных задач состояния и перспектив развития систем связи, а также вопросов разработки, производства и эксплуатации систем связи и ВОСП:

- Рассмотрение технических предложений при формировании разделов ФЦП и других документов, затрагивающих вопросы разработки и эксплуатации технических средств связи;

- Выработка предложений по совершенствованию и развитию телекоммуникационных сетей связи РФ с использованием волоконно-оптических линий связи ( ВОЛС );

- Выработка рекомендаций для решения проблем стандартизации сетевых стыков (интерфейсов), применяемых во взаимоувязанной сети связи РФ;

- Решение задач безопасности передачи информации по линиям связи;

- Рассмотрение вопросов стандартизации и новых технологий при разработке оборудования связи;

- Анализ состояния и перспективы развития элементной базы для ВОСП и других систем связи.

Контролирует и координирует деятельность СГК заместитель начальника Управления РЭП и СУ **Н.А.Иванчук**.

На предстоящем заседании предполагается рассмотреть следующие вопросы:

- Участие в ФЦП "Национальная технологическая база" на 2007-2011 годы;

- Аппаратура оконечного доступа ( вопросы разработки и применения ): модемы, маршрутизаторы, коммутаторы, коммуникационные системы, АТС, шифраторы и дешифраторы, анализаторы речи и данных, элементы питания и энергоснабжения;

- Измерительная аппаратура и ее применение;

- Вопросы унификации и стандартизации оборудования;

- Разработка и практическая реализация программных и аппаратных комплексов защиты каналов управления от несанкционированного доступа;

- Создание единой информационной базы по предприятиям поставщикам и производителям телекоммуникационной аппаратуры (с разделом "Новые разработки");

- Вопросы интеграции отечественных и зарубежных производителей телекоммуникационной аппаратуры.

Дополнительная информация — на сайте <u>www.sgk-urep.ru</u>. Исполнительный секретарь СГК **Михаил Викторович Волошенко**, *e-mail: info@sgk-urep.ru, vmv-68@rambler.ru*.