# БУДУЩЕЕ ТРАНЗИСТОРНЫХ СТРУКТУР

# Насколько справедлив закон Мура?

С утверждением, что мировой экономикой движут высокие технологии, спорить не приходится. Поэтому интерес ведущих производителей полупроводниковых приборов к перспективам дальнейшего развития выпускаемых изделий, несмотря на кризис, не удивителен. Особенно если учесть, что сегодня вследствие непрекращающегося масштабирования все труднее "выжать" требуемые характеристики современных микросхем: уменьшаются их размеры и напряжение, увеличивается быстродействие, а ток утечки и потребляемая мощность растут. Сможет ли микроэлектроника по-прежнему развиваться в соответствии с законом Мура, которому она следует не одно десятилетие?

рактически единственное изменение, которое претерпели активные полупроводниковые приборы, в том числе и полевые транзисторы на протяжении своего развития, - уменьшение минимальных размеров элементов (масштабирование) в соответствии с законом Мура. И на протяжении почти всей своей истории полупроводниковая промышленность определяла свои успехи, сопоставляя достигнутое с задачами масштабирования и увеличения плотности размещения элементов, поставленными перспективным планом развития (Roadmap). Но в конце 2001 года эксперты предупредили разработчиков, что масштабирование микросхем и другие способы повышения рабочих характеристик кремниевых транзисторов могут быстрее, чем предполагалось, привести к достижению физических пределов создаваемых структур. Так, уменьшение длины затвора и толщины затворного окисла транзисторов в схемах микропроцессоров, необходимое для увеличения их быстродействия, вызывает многие негативные эффекты, которые уже нельзя устранить с помощью существующих технологических методов. И действительно, по мере того как слой затворного диэлектрика становится все тоньше (а сегодня имеются транзисторные структуры с толщиной затворного окисла всего 0,8 нм, что равно трем атомным слоям), возрастают такие составляющие тока утечки, как паразитный ток затвора и туннельный ток через слой оксида. С уменьшением размеров транзисторов растет и ток утечки отключенного транзистора (так называемый ток утечки при субпороговом напряжении). Таким образом, транзистор практически никогда не бывает полностью отключен. Кроме того, с уменьшением толщины областей истока/стока растет их сопротивление и, соответственно, напряжение, требуемое для переключения прибора, а также его потребляемая мощность. Уменьшать же сопротивление этих областей путем увеличения уровня их легирования нельзя, поскольку практически предельные уровни концентрации носителей уже достигнуты (при концентрации носителей более 10<sup>18</sup> см<sup>-3</sup> наступает вырождение полупроводВ.Майская

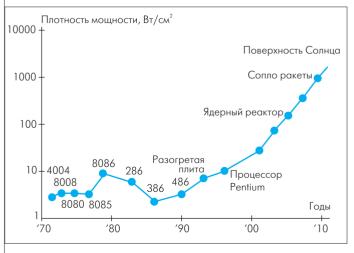

никового материала, приводящее к снижению подвижности носителей и ухудшению характеристик транзистора). В результате резко возрастает плотность потребляемой мощности (рис. 1). Как сообщил главный специалист по технологии фирмы-разработчика библиотек элементов Virtual Silicon на европейской конференции по проектированию, автоматизации и тестированию, при толщине затворного окисла 100 нм ток утечки МОП-транзистора может составлять 4 нА (в том числе и за счет туннельной составляющей). С увеличением тока повышается температура прибора, а с увеличением температуры растет ток. Круг замкнулся, и в режиме покоя возможен тепловой пробой транзистора. Таким образом, в ближайшие пять лет масштабирование КМОП-микросхем может достичь предельного уровня.

Один из путей решения проблемы — увеличение числа логических ячеек, работающих с несколькими пороговыми напряжениями, применение нескольких источников напряжения питания и активных средств управления потребляемой мощностью. Ток утечки может быть снижен и за счет увеличения порогового напряжения тех транзисторов, к быстродействию которых не предъявляются высокие требования. Но все это потребует существенного изменения всего процесса проектирования систем и, возможно, перехода к разработке полностью заказных устройств. А по утверждению разработчиков новейшего варианта Roadmap, необходимо идти по пути создания новых транзисторных структур, способных заменить традиционные КМОПустройства. И эти работы должны быть завершены в ближайшие шесть-девять лет. Иначе не удастся создать микросхемы, требуемые для будущих работающих в реальном времени систем распознавания и преобразования речи и образов или графических устройств, не уступающих по качеству изображения видеосистемам.

Рис. 1. Увеличение плотности потребляемой микропроцессором мощности

#### Разрабатываемые неклассические МОП-структуры

|                                          | Тип транзистора                                                                                                                              |                                                                                                                          |                                                                                                                                                                                          |                                                                                                                                                                  |                                                                                                                                                                                   |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Характеристики                           | КНИ со сверхтонкой<br>пленкой-основанием <sup>1</sup>                                                                                        | С управляемой проводимостью канала <sup>2</sup>                                                                          | Вертикальный <sup>3</sup>                                                                                                                                                                | С двойным<br>затвором <sup>4</sup>                                                                                                                               | FinFET <sup>5</sup>                                                                                                                                                               |

| Принцип<br>построения                    | КНИ-структура с полностью обед-<br>ненным носителями основанием                                                                              | SiGe-канал или канал из напряженного кремния                                                                             | С двойным затвором или полностью окруженной затвором структурой                                                                                                                          |                                                                                                                                                                  |                                                                                                                                                                                   |

| Достоинства                              | Улучшенная характеристика порогового напряжения, управляемость напряжения                                                                    | Высокое значение тока<br>возбуждения, возможность<br>изготовления на объемном и<br>КНИ-материале                         | Высокое значение тока<br>возбуждения, независи-<br>мость от разрешения<br>процесса литографии                                                                                            | Высокое значение тока возбуждения, улучшенная<br>характеристика порогового напряжения, слабо выра-<br>женный эффект короткого канала, формирование<br>NAND-схемы |                                                                                                                                                                                   |

| Особенности<br>масштабирования           | Возможность масштабирования толщины затворного оксида и всей структуры затвора; худший, чем у объемных КПОПструктур, эффект короткого канала | Возможность масштабирования толщины пленки с высокой подвижностью носителей и структуры затвора; хорошая интегрируемость | вой пленки и структуры затвора, хорошая интегрируемость, простота процесса, высокая точность,                                                                                            |                                                                                                                                                                  | Возможность центрирования<br>затвора, масштабирования<br>толщины кремниевой пленки<br>и структуры затвора, сложность<br>процесса; возможность автома-<br>тического проектирования |

| Проблемы<br>проектирования               | Определение характеристик прибора, компактное моделирование и выделение параметров                                                           | Определение характеристик<br>прибора                                                                                     | Определение характеристик прибора, выбор условий частичного или полного обеднения, компактное моделирование и выделение параметров, применение в устройствах смешанной обработки сигнала |                                                                                                                                                                  |                                                                                                                                                                                   |

| Основания для<br>продвижения на<br>рынок | Высокие рабочи                                                                                                                               | е характеристики, увеличение пло                                                                                         | отности размещения элемент                                                                                                                                                               | ов, уменьшение рассеив                                                                                                                                           | ваемой мощности                                                                                                                                                                   |

Примечание: <sup>1</sup> КНИ-транзисторы со сверхтонким основанием выполняются на чрезвычайно тонкой пленке кремния (толщиной менее 30 нм), нанесенной поверх оксидного слоя. Возможно формирование структур с полностью или частично обедненным каналом. <sup>2</sup> Транзистор с управляемой проводимостью канала характеризуется высокой подвижностью носителей в области канала, что достигается за счет применения слоя напряженного кремния, осаждаемого поверх ненапряженного слоя SiGe. Транзисторная структура не отличается от традиционной и может быть выполнена на объемном или КНИ-материале. <sup>3</sup> В вертикальном транзисторе на двух или более вертикальных поверхностях формируются поверхностные проводящие каналы. Ток протекает вертикально, в результате длина канала зависит не от толщины эпитаксиального слоя, а от вертикального зазора между истоком и стоком, т.е. этот параметр прибора не зависит от разрешения процессса и тографии.; <sup>4</sup> Транзистор с двойным затвором имеет два проводящих канала, сформированных с двух сторон горизонтальной поверхности, т.е. ток протекает горизонтально. Длина канала задается расстоянием между истоком и стоком в горизонтальной плоскости, т.е. зависит от разрешения процессов литографии и травления. <sup>5</sup> FinFET — разновидность транзистора с двойным затвором, длина канала которого задается разрешением процессов литографии и травления бокового спейсера.

Сегодня многие изготовители полупроводниковых приборов решают проблемы дальнейшего масштабирования размеров элементов микросхем с помощью альтернативных транзисторных структур. Изучается возможность использования металлического электрода и диэлектрика с высокой диэлектрической постоянной k, методов управления проводимостью исходного материала за счет применения напряженного кремния, SiGe и пр. (о чем, кстати, свидетельствуют доклады представителей Intel, IBM, Hitachi на Международной конференции по электронным приборам 2001 года). Предложены такие структуры, как КНИ-транзисторы с ультратонким основанием (Ultrathin Body — UTB), приборы с управляемой проводимостью канала, транзисторы с двойным затвором, или так называемые FinFET, вертикальные транзисторы (см. таблицу).

**UTB КНИ-ТРАНЗИСТОРЫ**

Транзисторы этого класса можно разделить на два типа — с полностью и частично обедненным носителями основанием (телом). Устранение эффекта короткого канала и регулировка порогового напряжения в таких транзисторах не требуют формирования сильнолегированного канала. Обе структуры пригодны для изготовления быстродействующих КМОП-микропроцессоров и систем-на-кристалле. В транзисторах первого типа тонкая пленка (менее 40 нм) полностью обеднена подвижными носителями при всех значениях напряжения смещения. Поскольку в области канала вследствие обеднения подложки заряда нет, электрическое поле в инверсионном слое прибора меньше, чем в обычных приборах с сильнолегированной областью канала, выполненных на объемном материале. Кроме того, крутизна характеристики субпорогового напряжения у этих транзисторов лучше, чем у обычных.

Именно такая структура легла в основу созданного специалистами фирмы Intel так называемого TeraHertz-транзистора, частота переключения которого, по оценкам разработчиков, сможет достичь 1000 ГГц, или 1 ТГц. UTB КНИ-структуры с минимальными размерами 50 нм и полностью обедненным основанием изготавливались на слое кремния толщиной менее 30 нм (толщина оксидной пленки

КНИ-структуры — 200 нм). Чтобы снизить (на 30%) паразитное сопротивление, присущее приборам с тонкой подложкой, и способствовать лучшему формированию контактов из силицида кремния, области истока/стока приподнимались (рис.2). Наличие слоя оксида под всей структурой транзистора привело к снижению тока утечки

#### Рис.2. Структура TeraHertz-транзистора

канала на два порядка. Кроме того, замена диоксида кремния в структуре затвора диэлектриком с высоким k позволила снизить ток утечки через затворный диэлектрик более чем на четыре (!) порядка. Материал наносился на подложку с помощью процесса атомного осаждения, позволяющего последовательно выращивать слои толщиной всего в одну молекулу. Для TeraHertz-транзисторов характерны также низкая емкость перехода, стойкость к воздействию альфа-излучения и отсутствие эффекта плавающей подложки.

Исследование показало, что TeraHertz-транзисторы намного превосходят стандартные КМОП-приборы (с длиной канала 70 нм и толщиной затворного оксида 1,5 нм) по быстродействию (на 25%) и потребляемой мощности (на 30%). При напряжении 1,3 В рабочий ток *р*-канального транзистора (толщина подзатворной пленки — три атомных слоя) равен 650 мкА/мкм, а ток утечки — 9 нА/мкм. На основе этих транзисторов Intel намерена к 2005—2007 году создать чипы микропроцессоров с минимальными топологическими нормами 20 нм, быстродействием до 20 ГГц и рабочим напряжением 1 В. Такой чип будет содержать миллиарды TeraHertz-транзисторов.

Основной недостаток КНИ-структур с частичным обеднением подложки — эффект плавающей квазинейтральной подложки. Но недавние работы фирмы IBM показали возможность контролировать этот эффект в структурах с размерами элементов до 30 нм, работающих при значениях напряжения 1,0—1,2 В. Это удалось благодаря формированию на сверхтонкой подложке имплантированного канала с "крутыми" стенками, или super-HALO-структуры. Для этого после изготовления глубоких областей истока/стока проводился отжиг с быстрым подъемом и спадом температуры. Затем стенки НАLО-области, расположенной под стоком/истоком, сужались путем имплантации ионов под углом к ним. Создание таких областей в КМОП-структуре на объемном кремнии привело бы к появлению неприемлемо высокой паразитной емкости перехода и высокого тока утечки. Но в UTB КНИ-структуре благодаря небольшому периметру перехода паразитная емкость мала. Ключевые требования к процес-

су формирования такой структуры — оптимизация уровня легирования затвора, конструкция спейсера и получение резких переходов областей истока/стока.

Разработчиками IBM созданы *п*-канальные транзисторы с минимальными размерами элементов 35 нм и *р*-канальные приборы с размерами элементов 33 нм. Рабочий ток транзисторов при напряжении 1,0 В равен 1100 и 457 мкА/мкм, а па-

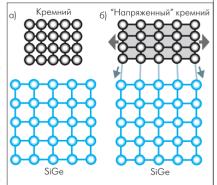

Рис.3. Формирования напряженного кремниевого слоя: а) расположение атомов транзисторов при напряжении 1,0 В равен 1100 и 457 мкА/мкм, а пастой кремния, осажденного поверх SiGe

разитная емкость — 0,27 фФ/мкм и 0,32 фФ/мкм, соответственно. Ток утечки обоих транзисторов — 300 нА/мкм. На основе SiGe-технологии на фирме изготовлен UTB КНИ-транзистор, способный работать на частоте 210 ГГц. Уже в 2003 году разработчики ожидают появления микросхем с такими транзисторами. Но это не единственный новый тип транзистора, предлагаемый таким "генератором идей", как IBM.

### МОП-ТРАНЗИСТОРЫ С УПРАВЛЯЕМОЙ ПРОВОДИМОСТЬЮ КАНАЛА

Эти приборы нельзя непосредственно отнести к альтернативному типу – по своей структуре они подобны традиционным МОП-транзисторам. Но метод их изготовления существенно отличается от современной КМОП-технологии. Он основан на естественном стремлении атомов соединения к упорядоченной ориентации друг относительно друга. При осаждении кремния на подложку из материала с отличным от него межатомным расстоянием кристаллической решетки (например, на кремний-германиевую) атомы кремния стремятся выровняться в соответствии с атомами подложки. Если это расстояние больше, чем в кремнии, происходит "растяжение" атомов последнего, т.е. кремний оказывается напряженным (рис.3) и скорость дрейфа электронов будет на 70% выше, чем в обычном кремнии. В результате, даже не изменяя размеров транзисторов, можно увеличить быстродействие чипа на 35%. Разработчики фирмы считают, что в сочетании с уже освоенными в производстве медной, КНИ- и SiGe-технологиями новый метод позволит фирме попрежнему на год-два опережать остальных производителей полупроводниковых приборов в области промышленной технологии. И, действительно, новые изделия, выполненные на основе структур с напряженным кремнием, фирма рассчитывает создать уже в 2003 году. Но и это не последняя разработка фирмы в области новейших типов транзисторов.

## МОП-ТРАНЗИСТОРЫ С ДВОЙНЫМ ЗАТВОРОМ

Возможность создания МОП-транзистора с двойным затвором изучается достаточно давно, с 90-х годов. Но лишь в конце 2001 года ІВМ объявила о создании альтернативного типа транзистора, который благодаря лучшему управлению эффектом короткого канала, характеристике субпорогового напряжения, близкой к идеальной, и высокой подвижности носителей в канале сможет стать многообещающим кандидатом для будущих микросхем с высокой плотностью размещения элементов и малой потребляемой мощностью. При разработке этого прибора неоценимую помощь оказал опыт фирмы в области КНИ-технологии. Ток транзистора с двумя затворами и, следовательно, его сигнал почти вдвое выше, чем в обычном МОПприборе с большими размерами элементов. Такую структуру легко масштабировать, и на ее базе можно выполнить любой тип МОПтранзистора. Основная задача при ее формировании – получение приемлемого значения порогового напряжения транзисторов быстродействующих логических устройств при контроле значения проводимости канала.

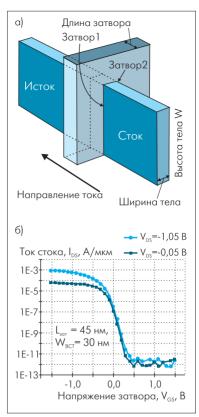

Особый интерес представляет разновидность транзистора с двойным затвором — FinFET. В этом приборе тонкое кремниевое тело (столбик, вставка — fin) "обернуто" затвором, который формирует два самосовмещенных канала, расположенных с двух сторон кремниевого тела (рис.4). Выступающая передняя область тела — исток транзистора, выступающая задняя область — сток. Ток протекает в плоскости, параллельной плоскости тела, т.е., хотя затворы и выступают за пределы этой плоскости, структуру FinFET можно рассматривать как квазипланарную. Активная ширина прибора равна высоте тела-столбика, и ее можно увеличивать путем параллельно-

Рис.4. Структура FinFET (a) и его вольт-амперные характеристики (б)

го включения многих столбиков. По своей топологии FinFET не отличается от традиционного МОП-транзистора. за исключением того. что активная область формируется вставками, а не представляет собой плоский прямоугольник. Производство FinFET легко наладить: все необходимые технологические операции широко используются в современном полупроводниковом производстве и хорошо отработаны. Правда, самый критичный параметр этой структуры - толщина канала - зависит от разрешения процесса литографии.

Фирмой IBM созданы симметричные и асимметричные и р-канальные МОП-транзисторы этого типа, характеристики которых оптимизированы для получения высокого быстродействия и низкого порогового

напряжения, соответственно. Процесс изготовления полностью обедненного симметричного FinFET предусматривает формирование рисунка тела-вставки толщиной 20 нм методами фотолитографии. Структура затвора состоит из термически выращенной пленки оксинитрида толщиной 1,6 нм и поликремния. Выступающие области истока/стока изготовлены путем проведения ионной имплантации под углом  $45^{\rm o}$  с четырех сторон пластины. В результате электрическая длина канала  $L_{\rm eff}$  составила 30 нм. Ток n- и p-канальных FinFET был равен 1300 и 850 мкА/мкм, соответственно.

Высота тела-вставки асимметричных FinFET - 180 нм, толщина затворного диэлектрика - 2,2 нм, поликремниевого затвора - 75 нм. Для легирования материала затвора и приподнятых областей исто-ка/стока до и после вытравливания рисунка затвора проводилась ионная имплантация под углом  $30^{\circ}$ . Благодаря соответствующей экранировке имплантируемых ионов с одной стороны затвора был сформирован поликремний p-типа, а с другой - n-типа. Пороговое напряжение транзистора составило примерно 0,1 В. Ток логического устройства на базе такого транзистора в выключенном состоянии при  $V_{gs} = 0$  не превышал 60 нА/мкм. Пороговое напряжение насыщения равно 0,15 В при рабочем токе 55 нА/мкм и токе утечки 7 нА/мкм.

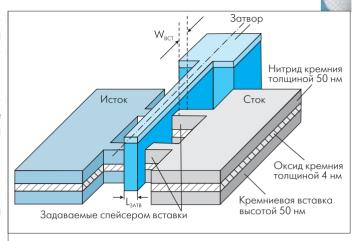

Совместными усилиями Калифорнийского университета в Беркли, фирмы Intel и Национальной лаборатории Лоуренса создана FinFET-структура с длиной канала менее 20 нм, в которой размеры кремниевой вставки задаются промежутками между поликремниевыми затворами, а области истока/стока — процессом литографии (рис.5). За счет нанесения "жертвенных" пленок на боковые стенки каждого промежуточного зазора разработчикам удалось вдвое увеличить ток транзистора и уменьшить толщину вставки в сравнении с приборами, изготовленными только с помощью процесса литографии. Структура затвора состоит из термически выращенного оксида толщиной 2,4 нм и SiGe толщиной 400 нм.

Рис.5. Структура FinFET, предложенная Калифорнийским университетом

#### ВЕРТИКАЛЬНЫЕ МОП-ТРАНЗИСТОРЫ

Наилучших результатов в создании транзисторов этого типа достигла фирма Agere Systems. Разработка прибора, названного транзистором с вертикально замещенным затвором (Vertical Replacement-Gate — VRG), была начата в 1999 году в стенах Bell Labs, где тогда трудились разработчики. Особенности нового прибора: возможность контроля с высокой точностью длины канала, равной 50 нм, и применение в качестве затворного диэлектрика с высоким k оксида гафния. Хотя этот материал имеет поликристаллическую структуру, ток утечки VRG-транзистора достаточно мал. Задача нанесения пленки HfO $_2$  также была решена с помощью метода послойного атомного осаждения, позволяющего получать равномерные по толщине пленки на любой поверхности, включая глубокие карманы или узкие канавки.

Появление новых альтернативных транзисторных структур позволяет утверждать, что полупроводниковая промышленность в ближайшие годы по-прежнему будет развиваться в соответствии с законом Мура. К тому же, по своим характеристикам UTB КНИ-транзисторы и транзисторы с двойным затвором превосходят МОП-транзисторы, изготовленные на объемном кремнии. Сейчас ведутся работы по совершенствованию методов проектирования и производства таких устройств с тем, чтобы полностью реализовать их возможности. Объем этих работ велик, но, тем не менее, появления каких-либо из рассмотренных выше транзисторов и схем на их основе можно ожидать уже в 2004 году. Это позволяет главному исполнительному директору фирмы Intel Крейгу Барретту утверждать, что закон Мура не только жив и здоров, но по-прежнему остается основной движущей силой развития высокотехнологичной промышленности, а следовательно, и экономического роста страны.

Semiconductor International, March, 2000. Материалы фирм Intel, IBM, Agare Systems.

# Самая "быстрая" микросхема

И снова ІВМ

Фирма IBM сообщила о создании, как она утверждает, самой быстродействующей микросхемы на частоту 110 ГГц, изготавливаемой по 0,18-мкм SiGe-технологии с использованием медных межсоединений и алюминиевой металлизации (толщиной 4 мкм) для формирования сигнальных линий. Основной элемент микросхемы — HBT с  $f_{max} = 285$  ГГц. Ток каскада кольцевого генератора при напряжении 3,6 В равен 2 мА. Фирма намерена уже в 2002 году выпустить опытные образцы микросхемы, предназначеной для связного оборудования, в том числе коммутационных систем и маршрутизаторов оптических коммуникационных сетей. Освоить их производство планируется к середине 2003 года. Electronic News, 2002, Feb. 25.