## Пример реализации однотактного процессорного ядра RISC-V в САПР Altera Quartus II

А.В. Строгонов, д.т.н.<sup>1</sup>, А. Винокуров, к.т.н.<sup>2</sup>, А.И. Строгонов<sup>3</sup>

УДК 004.31 | ВАК 2.2.2

В России продолжается популяризация и развитие открытой архитектуры RISC-V. Сегодня разработкой проектов на базе открытой архитектуры RISC-V занимается ряд российских компаний и ведущих университетов. Например, микроконтроллер Hackee на базе ядра SCR1 (от российского разработчика Syntacore) был спроектирован совместно магистрантами НИУ «МИЭТ» и специалистами компании Yadro. «Микрон» представил микроконтроллер «МІК32 Амур» (К1948ВК018) на базе RISC-V и отладочную плату на его основе. Есть проекты и других российских компаний, действующих в рамках «Альянса RISC-V» [1]. Одним из направлений исследований в этой области является отработка прототипов процессоров на платформе ПЛИС. В статье рассмотрен пример реализации однотактного процессорного ядра RISC-V в базисе ПЛИС Cyclone V с применением САПР Altera Quartus II.

ля реализации процессора RISC-V в данной работе была выбрана однотактная микроархитектура, которая выполняет всю команду за один такт. Изза того, что все действия выполняются за один такт, эта микроархитектура не требует никаких дополнительных регистров, недоступных для программиста. Основным преимуществом однотактной микроархитектуры является простой принцип ее работы.

В данной разработке в качестве основного языка был выбран VHDL, хотя процессор можно реализовать на двух языках: SystemVerilog и VHDL. Коды SystemVerilog/VHDL основных функциональных блоков RISC-V приведены в разделе 7.6.1 работы [2]. В работах [2] и [3] синтез кодов SystemVerilog/VHDL осуществлялся с помощью программы Synplify Premier от Synplicity.

процессорного ядра RISC-V возникли некоторые вопросы, связанные с синтезатором-компилятором QIS САПР

При адаптации VHDL-кодов функциональных блоков

Quartus II. Прояснить эти вопросы помогла оригинальная версия переводного учебника [3]. При разработке проекта в базисе ПЛИС Cyclone V были сохранены оригинальные коды SystemVerilog/VHDL и обозначения сигналов и шин.

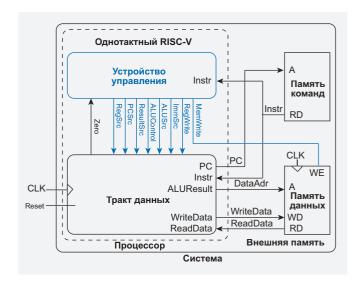

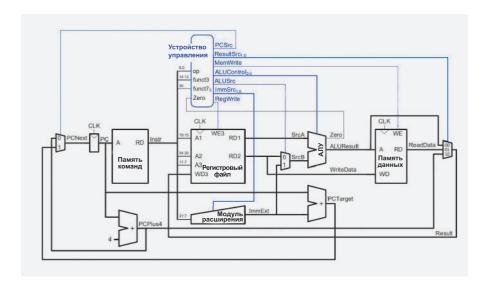

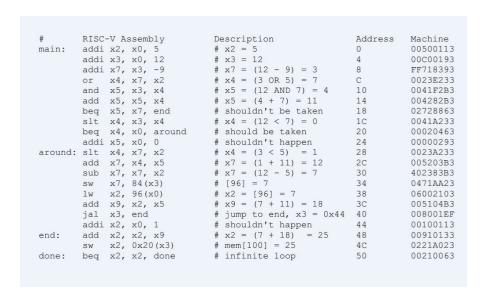

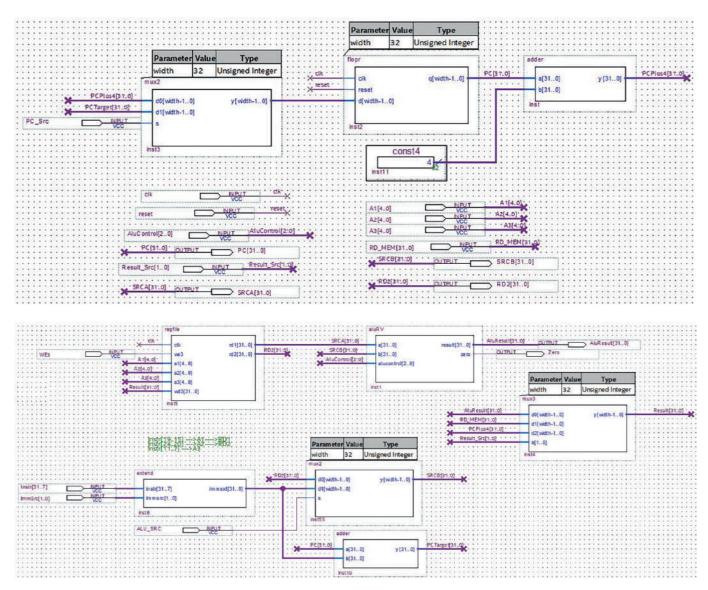

Структурная и функциональная схемы однотактного процессорного ядра RISC-V (с поддержкой команды addi) показаны на рис. 1 и 2. На рис. 3 представлена тестовая

Рис. 1. Структурная схема однотактного процессорного ядра RISC-V

Воронежский государственный технический университет, профессор кафедры твердотельной электроники, тел. +79102471470, andreistrogonov@mail.ru.

Воронежский государственный технический университет, доцент кафедры твердотельной электроники.

Воронежский государственный университет, факультет компьютерных наук, кафедра программирования и информационных технологий, ассистент.

программа (машинный код хранится в шестнадцатеричном файле riscvtest.txt), зашитая в ПЗУ (рис.7.64 и 7.65 из [2]). Тестируются следующие команды: add, sub, and, or, slt, addi, lw, sw, beq, jal. Если тест проходит успешно, то значение  $25 (0 \times 19)$  должно записаться по адресу  $100 (0 \times 64)$ .

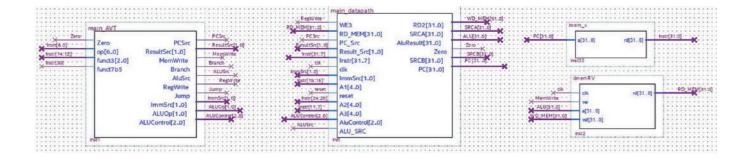

Верхний уровень иерархии проекта в САПР Quartus II, в отличие от работы [2], представлен не структурным файлом (объект riscvsingle, пример 7.1 из [2]) на языке VHDL, а иерархической схемой в графическом редакторе (рис. 4). На рис. 5 в качестве примера показан тракт данных, соответствующий примеру 7.5 (объект datapath).

При адаптации RISC-V в САПР Altera Quartus II возник ряд проблем. Все шины данных во всех функциональных блоках (в работе [2] они называются строительными блоками) должны быть 32-разрядными. В некоторых функциональных блоках требуется увеличение разрядности шин с 8 до 32 (регистр с сигналом сброса flopr, пример 7.8 [2]; шинный мультиплексор 2:1, пример 7.10 [2]; шинный мультиплексор 3:1, пример 7.11 [2]).

Синтезатор Quartus II не поддерживает пакет расширения IEEE. NUMERIC\_STD\_UNSIGNED.all от Synopsys или Mentor Graphics. Поэтому в данной работе использовали пакеты IEEE.NUMERIC\_STD.all и IEEE. std\_logic\_unsigned.all.

Возникла также проблема с памятью команд (асинхронное ПЗУ). При

Рис. 2. Функциональная схема однотактного процессорного ядра RISC-V

**Рис. 3.** Ассемблерный и машинный коды (крайний правый столбец – прошивка ПЗУ, текстовый файл riscvtest.txt)

Рис. 4. Верхний уровень иерархии однотактного процессорного ядра RISC-V в САПР Quartus II

Рис. 5. Тракт данных однотактного процессорного ядра RISC-V в САПР Quartus II

```

10385 VMDL error at ipzu.vhd(28): index value 64 is outside the range (63 downto 0) of object "ram_content"

10657 VMDL Subprogram error at ipzu.vhd(28): failed to elaborate call to subprogram "MREAD"

12132 Can't elaborate user hierarchy "ipzu:inst3"

144001 Generated suppressed messages file C:/Quartus-Proekt_2024_v15/RISCV_simple/output_files/Riscv_simpl.map.smsg

Quartus Prime Analysis & Synthesis was unsuccessful. 3 errors, 4 warnings

293001 Quartus Prime Full Compilation was unsuccessful. 5 errors, 4 warnings

```

Рис. 6. Ошибка компиляции VHDL-кода ПЗУ из примера 7.14 работы [1]

компиляции исходного VHDL-кода ПЗУ (пример 7.14) возникает ошибка компиляции (рис. 6). Причина неудачной инициализации ОЗУ в проекте заключается в том, что операции ввода-вывода файлов в VHDL не поддерживаются синтезатором в Quartus II. Пример 1 (рис. 7) демонстрирует «подправленный» (сделан по шаблону XST [4, 5]) VHDLкод, который все же проходит безошибочную компиляцию с загрузкой из текстового файла riscvtest.txt, однако mif-файл конфигурации ПЗУ создается пустым (с нулевым

содержимым) (пример 2, рис. 8). Это говорит о том, что VHDL-код ПЗУ с загрузкой из файла является не синтезируемым в САПР Quartus II, но может быть использован, например, в САПР Xilinx.

Воспользоваться встроенной мегафункцией ПЗУ ROM: 1PORT не получилось по причине ограничения разрядности адресной шины и того, что ПЗУ работает в синхронном режиме.

В руководстве пользователя [4] указано, что Quartus II поддерживает системные команды \$readmem и \$readmemh в Verilog для инициализации памяти с помощью текстового файла. Поэтому было принято решение использовать оригинальный SystemVerilog-код ПЗУ (пример 7.14). На рис. 4 показан проект процессорного

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use std.textio.all;

entity rom_prog is

port(

addr : in std_logic_vector(31 downto 0);

dout : out std_logic_vector(31 downto 0));

end entity;

architecture syn of rom_prog is

type RomType is array(0 to 63) of bit_vector(31 downto 0);

impure function InitRomFromFile (RomFileName : in string) return RomType is

FILE RomFile : text is in RomFileName;

variable RomFileLine : line;

variable ROM : RomType;

beain

Рис. 7.

for I in RomType'range loop

readline (RomFile, RomFileLine);

Пример 1:

hread (RomFileLine, ROM(I));

VHDL-код

end loop;

ПЗУ, который

return ROM;

end function;

проходит

безошибочную

signal ROM : RomType := InitRomFromFile("riscvtest.txt");

компиляцию

process (addr)

в САПР

begin

Quartus II, но

dout <= to_stdlogicvector(ROM(conv_integer(addr)));</pre>

с генерацией

end process;

end syn;

«пустого»

mif-файла

```

```

WIDTH=32;

DEPTH=64;

ADDRESS RADIX=UNS;

DATA_RADIX=BIN;

CONTENT BEGIN

19:

18:

17:

16:

15:

14:

13:

12:

11:

10:

9:

8:

7:

5:

4:

3:

2:

1:

0:

END;

```

```

Рис. 8. Пример 2: фрагмент сгенерированного «пустого» mif-файла из VHDL-кода ПЗУ

```

```

--begin_signature

--imem_v

--end_signature

WIDTH=32;

DEPTH=64;

ADDRESS_RADIX=UNS;

DATA_RADIX=BIN;

CONTENT BEGIN

20: 0000000001000010000000001100011;

19:

00000010001000011010000000100011;

18:

0000000100100010000000100110011;

0000000000100000000000100010011;

17:

000000001000000000000000111101111:

16:

0000000010100010000010010110011;

15:

00000110000000000010000100000011;

14:

13:

000001000111000110101010000100011;

12:

01000000001000111000001110110011;

11:

00000000010100100000001110110011;

10:

00000000001000111010001000110011;

9:

000000000000000000000001010010011:

8:

00000000000000100000010001100011;

7:

0000000010000011010001000110011;

6:

00000010011100101000100001100011:

5:

00000000010000101000001010110011;

00000000010000011111001010110011:

4:

3:

0000000001000111110001000110011;

11111111011100011000001110010011;

2:

00000000110000000000000110010011;

1:

0:

0000000010100000000000100010011;

END;

```

**Рис. 9.** Пример 3: фрагмент сгенерированного mif-файла из SystemVerilog-кода ПЗУ

Рис. 10. RTL-представление из SystemVerilog-кода ПЗУ

ядра RISC-V в САПР Quartus II с использованием ПЗУ и ОЗУ на SystemVerilog.

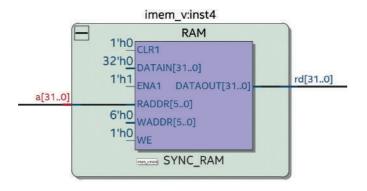

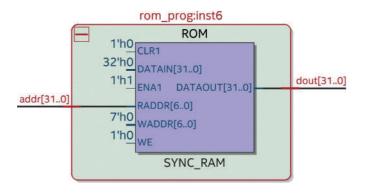

Пример 3 (рис. 9) показывает, что САПР генерирует заполненный mif-файл (64 строки (слова) по 32 бита в каждой; система счисления содержимого DATA RADIX представлена в двоичном формате BIN, а содержимого адресов – в беззнаковом десятичном UNS) из SystemVerilog-кода ПЗУ. Рис. 10 показывает, что асинхронное ПЗУ организуется на базе синхронного ОЗУ с 6-разрядной адресной шиной RADDR[5..0].

Тем не менее, можно организовать инициализацию ПЗУ ([5]) непосредственно из VHDL-кода (пример 4, рис. 11).

```

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use std.textio.all;

entity rom_prog is

port(

addr : in std_logic_vector(31 downto 0);

dout : out std_logic_vector(31 downto 0));

end entity;

architecture syn of rom_prog is

type RomType is array(0 to 80) of bit_vector(31 downto 0);

impure function InitRomFromFile (RomFileName : in string) return RomType is

FILE RomFile : text is in RomFileName;

variable RomFileLine : line;

variable ROM : RomType;

beain

for I in RomType'range loop

readline (RomFile, RomFileLine);

hread (RomFileLine, ROM(I));

end loop;

return ROM;

end function;

signal ROM : RomType :=

(X"00500113", X"00000000", X"00000000", X"00000000", X"00C00193", X"00000000", X"00000000", X"FF718393",

X"00000000", X"00000000", X"00000000", X"06002103"

X"00000000", X"00000000", X"000000000", X"005104B3"

X"00000000", X"00000000", X"00000000", X"000104B3", X"00000000", X"00000000", X"00000000", X"00100113", X"00000000", X"00000000", X"00000000", X"0000113", X"00000000", X"00000000", X"00001133",

X"00000000", X"00000000", X"00000000", X"0221A023",

X"00000000", X"00000000", X"00000000", X"00210063");

begin

process (addr)

begin

dout <= to_stdlogicvector(ROM(conv_integer(addr)));</pre>

-- dout <= ROM(conv_integer(addr));</pre>

end process;

end syn;

```

Рис. 11. Пример 4: инициализация ПЗУ непосредственно из HDL-кода

Вы давно знаете нас как надежного и проверенного поставщика материалов для электронной промышленности. Сегодня мы перешли на следующий уровень и стали их производителем. Сделанные нами материалы уже применяются более чем в тысяче техпроцессов на российских производствах. Мы убеждены, что современные отечественные материалы не должны уступать ведущим мировым брендам по своим техническим и эксплуатационным характеристикам. И активно работаем над этим — в собственной лаборатории и на нашем производстве в России.

**ГИДРОНОЛ** — собственная линейка эффективных жидкостей для отмывки печатных узлов, очистки трафаретов и оборудования. Разработанные с учетом специфики российского производства высококачественные жидкости подходят для любого известного техпроцесса и технологии. Всегда в наличии независимо от условий и обстоятельств. С решениями Гидронол процесс отмывки полностью в ваших руках.

Сделано нами — сделано на совесть.

Рис. 12. RTL-представление из VHDL-кода ПЗУ (Пример 4)

В этом случае нужно будет заполнять дистанцию между реальными командами тремя пустыми значениями, например, X"00500113", X"00000000", X"00000000", X"00000000", Х"00С00193", по причине того, что счетчик команд уве-

личивает свое содержимое на 4, поскольку команды в RISC-V являются 4-байтовыми. В этом случае потребуется 80 строк и использование 7-разрядной адресной шины RADDR[6..0] (рис. 12). Пример 5 (рис. 13) демонстрирует фрагмент сгенерированного mif-файла при инициализации ПЗУ непосредственно в HDL- коде.

Выявилась также проблема компиляции ОЗУ данных. VHDL-код из работ [2, 3] используется так же и для реализации ОЗУ MIPS-процессора [6]:

- · mips.vhd

- From Section 7.6 of Digital Design & Computer Architecture

- Updated to VHDL 2008 26 July 2011 David\_Harris@hmc.edu.

В VHDL-коде ОЗУ (пример 7.15 из работ [2, 3]) используется to\_integer, оператор wait on и 8-разрядная адресная шина a(7 downto 2) (пример 6, рис. 14). Первые две причины приводят к ошибкам компиляции в САПР Quartus II, которые можно исправить, заменив to integer на conv integer с соответствующим пакетом IEEE.std\_logic\_unsigned.all, и использовать один оператор process на запись и считывание (пример 7, рис. 15).

Использование 8-разрядной адресной шины a(7 downto 2) ОЗУ данных приводит к неправильному функционированию процесса. Поэтому был

```

--begin_signature

--rom_prog

--end_signature

WIDTH=32;

DEPTH=128:

ADDRESS_RADIX=UNS;

DATA_RADIX=BIN;

CONTENT BEGIN

0000000001000010000000001100011;

80:

8:

11111111011100011000001110010011;

7:

6:

5:

4:

000000011000000000000110010011;

3:

2:

1:

0:

0000000010100000000000100010011;

END:

```

**Рис. 13.** Пример 5: фрагмент сгенерированного mif-файла при инициализации ПЗУ непосредственно в HDL-коде

```

-- чтение или запись в память

loop

if rising_edge(clk) then

if (we = '1') then mem(to_integer(a(7 downto 2))) := wd;

end if:

end if;

rd <= mem(to_integer(a(7 downto 2)));</pre>

wait on clk, a;

end loop:

```

Рис. 14. Пример 6: фрагмент VHDL-кода ОЗУ данных (пример 7.15, работы [1, 2])

```

library IEEE;

use IEEE.STD LOGIC 1164.all;

use STD.TEXTIO.all;

use IEEE.std_logic_unsigned.all;

entity dmem_heris is

port(clk, we: in STD_LOGIC;

a, wd: in STD_LOGIC_VECTOR(31 downto 0);

rd: out STD_LOGIC_VECTOR(31 downto 0));

end:

architecture a of dmem_heris is

type ramtype is array (63 downto 0) of

STD LOGIC VECTOR(31 downto 0);

signal mem: ramtype;

beain

— чтение или запись в память

process(clk,we,a)

begin

if rising_edge(clk) then

if (we =

'1') then mem(conv integer(a(31 downto 2))) <= wd;

end if:

end if;

rd <= mem(conv_integer(a(31 downto 2)));

end process:

end a:

```

Рис. 15. Пример 7: фрагмент VHDL-кода ОЗУ данных с одним оператором process на запись и считывание

## Посты оптического микроконтроля

• Микроскоп МИКРО 200

тел.: (+375 17) 377-90-64, e-mail: office@optes.by

```

module aluRV(input logic [31:0] a, b,

input logic [2:0] alucont output logic [31:0] result,

alucontrol,

output logic

zero);

logic [31:0] condinvb, sum;

logic

// overflow

isAddSub;

logic

// true when is add or subtract operation

assign condinvb = alucontrol[0] ? ~b : b;

assign sum = a + condinvb + alucontrol[0];

assign isAddSub = ~alucontrol[2] & ~alucontrol[1] |

~alucontrol[1] & alucontrol[0];

always_comb

case (alucontrol)

3'b000: result = sum;

// add

3'b001: result = sum;

3'b010: result = a & b;

// subtract

// and

3'b011: result = a | b;

// or

3'b100: result = a ^ b;

3'b101: result = sum[31

// xor

result = sum[31] ^ v;

3'b110: result = a << b[4:0]; // sll

3'b111: result = a >> b[4:0]; // srl

default: result = 32'bx;

endcase

assign zero = (result == 32'b0);

assign v = \sim (alucontrol[0] ^ a[31] ^ b[31]) & (a[31] ^ sum[31]) & isAddSub;

endmodule

```

Рис. 16. Пример 8: код АЛУ с поддержкой команды SLT

использован оригинальный SystemVerilog-код ОЗУ с 32-разрядной адресной шиной. Как вариант можно использовать доработанный VHDL-код (см. пример 7, рис. 15).

В работах [2, 3] разработка VHDL-кода АЛУ вынесено в самостоятельную задачу. Однако, код АЛУ можно взять из [6] от MIPS-процессора (пример 8, рис. 16). VHDL-код в точности соответствует схеме на рис. 5.18, б из работы [2]. АЛУ поддерживает команду SLT (set if less than – «установить, если меньше, чем», когда A < B, Result = 1), а также логические сдвиги влево (LSL) или вправо (LSL).

В работе [2] приведена программа тестбенча (объект testbench, пример 7.12). Он проверяет наличие записи в память данных и сообщает об успехе, если правильное значение (25) записано по адресу 100.

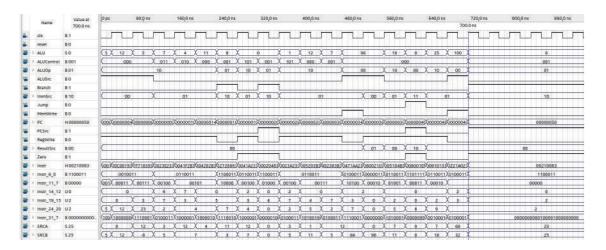

Но мы не будем его использовать, а подтвердим правильность разработки функциональным моделированием

с использованием симулятора ModelSim Altera Starter Edition и векторного редактора. Функциональное моделирование показывает, что тест проходит успешно (рис. 17). Значение 25 (0 $\times$ 19) записывается в ОЗУ по адресу 100 (0 $\times$ 64). Проект работает на максимальной частоте 58 МГц (табл. 1).

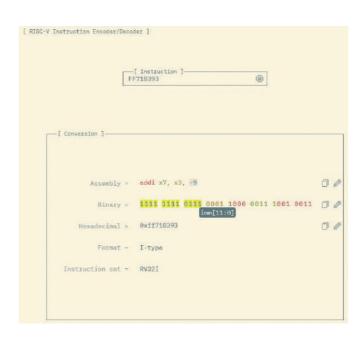

Проверить правильность выполнения команд можно с помощью бесплатной онлайн-программы «кодер/ декодер команд RISC-V» [7] (рис. 18). На рис. 18 показан перевод команды FF718393 (третья команда с адресом 8 на рис. 3), представленной в шестнадцатеричном формате, в ассемблерный код addi x7, x3, -9. В результате выполнения этой команды в регистр с адресом х7 будет занесено число 3: x7 = (12-9) = 3 (см. рис. 17).

Команда FF718393 представляется в двоичном коде с выделением полей команд процессора RV32I. На рис. 18 видно, что это команда относится к типу I. Если сравнить

Таблица 1. Используемые ресурсы ПЛИС Cyclone V 5CGXFC7C7F23CB

| Проект                                                  | Логические ресурсы Адаптивные логические модули (ALM) | Адаптивные таблицы<br>перекодировок (ALUT)<br>для реализации<br>комбинационных функций | Выделенные<br>триггеры<br>логических<br>элементов | Максимальная тактовая частота синхросигнала, МГц (модель Slow 1100 мВ, 85 °C) |

|---------------------------------------------------------|-------------------------------------------------------|----------------------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------------------------------------|

| Асинхронное ПЗУ<br>и синхронное ОЗУ<br>на SystemVerilog | 2347                                                  | 1773                                                                                   | 3008                                              | 58                                                                            |

Рис. 17.

Временная

диаграмма

успешного

прохождения

теста,

представленного на рис. 3

рис. 17 и 18, то можно увидеть, что поля команды, формируемые проектом процессора RISC-V в CAПР Quartus II, правильно заполнены значениями.

## **ЗАКЛЮЧЕНИЕ**

Несмотря на незначительные проблемы с адаптацией HDL-кода однотактного процессорного ядра RISC-V, в данной работе удалось успешно реализовать его в базисе ПЛИС Cyclone V с применением CAПP Altera Quartus II. При этом максимальная рабочая частота данной реализации составила 58 МГц.

Потребовалась доработка VHDL-кода ПЗУ команд и ОЗУ данных, а также замена разрядности шин данных

Рис. 18. Окно онлайн-программы «Кодер/декодер команд RISC-V», позволяющей переводить машинный код в ассемблерный с выделением полей команд в двоичном коде

в некоторых функциональных блоках с 8 на 32 (регистр с сигналом сброса flopr, пример 7.8 [2]; шинный мультиплексор 2:1, пример 7.10 [2]; шинный мультиплексор 3:1, пример 7.11 [2]).

## ЛИТЕРАТУРА

- Строгонов А.В., Бордюжа О.Л., Строгонов А.И. Эффективный подход в разработке управляющих автоматов микропроцессорных ядер // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2024. № 1. С. 78–86.

- 2. **Харрис С.Л., Харрис Д.** Цифровая схемотехника и архитектура компьютера RISC-V / Пер. с англ. В.С. Яценкова, А.Ю. Романова; под ред. А.Ю. Романова. М.: ДМК Пресс, 2021. 810 с.

- 3. **Harris S.L., Harris D.** Digital Design and Computer Architecture RISC-V Edition. 2022. ISBN: 978-0-12-820064-3.

- 4. Intel Quartus Prime Pro Edition User Guide. Design Recommendations. UG-20131. ID: 683082. Version: 2021.10.04.

- 5. XST User Guide. 10.1. ROMs Using Block RAM Resources HDL Coding Techniques // www.xilinx.com.

- 6. https://pastebin.com/ew0SACWy.

- 7. https://luplab.gitlab.io/rvcodecjs/#q=00C00193&abi=false&isa=AUTO.