## Последние достижения при создании чиплетов с использованием мостовых межсоединений

$\mathbf{\mathcal{L}}$ . Суханов<sup>1</sup> УДК 621.3 | ВАК 2.2.2

Сегодня искусственный интеллект (ИИ) все больше проникает во все сферы жизни человека. Также активно развиваются системы связи поколений 5G/6G и такие приложения, как высокопроизводительные вычисления (HPC - high-performance computing), автономные транспортные средства, Интернет вещей, большие объемы данных (для облачных вычислений). Подобные приложения требуют более совершенных технологий корпусирования, в том числе с использованием чиплетов. В данной статье рассматриваются различные современные решения с применением мостовых межсоединений, которые позволяют существенно снизить стоимость и размеры систем на базе чиплетов.

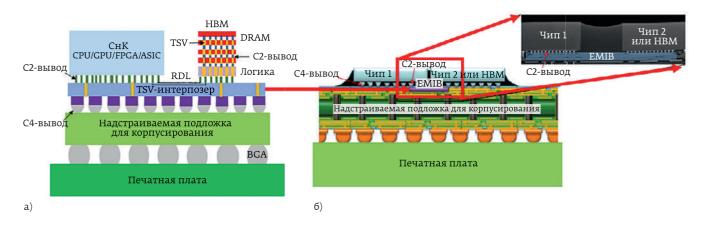

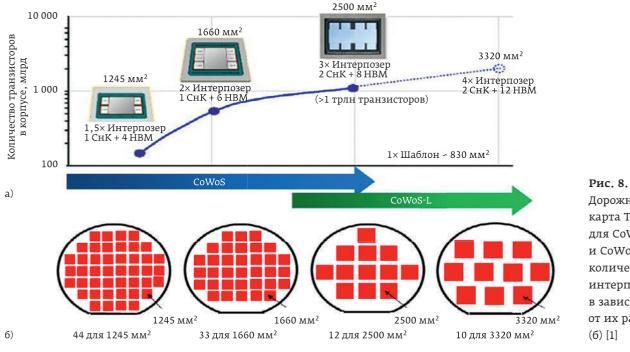

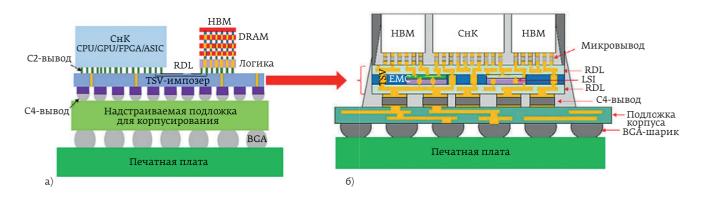

дной из самых популярных передовых технологий корпусирования является 2,5D- или 3D-интеграция интегральных схем (ИС), что схематически показано на рис. la. Компания TSMC назвала интеграцию 2,5D ИС «чип на пластине на подложке» (Chip-on-waferon-substrate, CoWoS).

Видно, что устройства системы на кристалле (СнК), такие как центральный процессор (CPU) и графический процессор (GPU), а также память с высокой пропускной способностью (high bandwidth memory, HBM), поддерживаются пассивным (2,5D) или активным (3D) переходными слоями с отверстиями в кремнии (through-silicon vias, TSV) – интерпозерами. Наконец, весь модуль прикрепляется к печатной плате с помощью шариков припоя (BGA) и паяльной пасты. Такая система с несколькими микросхемами и гетерогенно-интеграционное корпусирование обусловлены требованиями к производительности и форм-фактору и предназначены для приложений с чрезвычайно высокими плотностью и производительностью

Первые документы по интеграции 2,5D ИС были опубликованы в 2005 году. В 2013 стало доступно большое количество GPU от самых разных производителей на сравнительно простых интерпозерах. Спустя почти 20 лет после первого упоминания о 2,5D ИС появился GPU с шестью HBM2 на «огромном», по меркам микроэлектроники, активном интерпозере размером 160 x 160 мм<sup>2</sup> и это уже сложнейшая 3D-интеграция.

Что же ждет нас дальше? Может быть – весь ИИ в одном устройстве, а точнее в одной 3D-микросхеме?

2,5D или 3D ИС с TSV-интерпозером обладают высокой стоимостью. Одна из ключевых причин этого заключается в том, что при производстве TSV-интерпозера используется дорогой технологический процесс (64 нм), а также наблюдаются потери выхода годных из-за большого размера интерпозера и присутствия межсоединений.

Давайте разберемся с самыми последними достижениями в технологиях микроэлектроники, которые позволят заменить дорогостоящие TSV-интерпозеры. За последние 5-7 лет стали все более «популярны» так называемые кремниевые мосты. Что это такое? Каких видов они бывают? Какое развитие они получили?

#### ВСТРОЕННЫЙ МНОГОКРИСТАЛЬНЫЙ **МЕЖБЛОЧНЫЙ МОСТ**

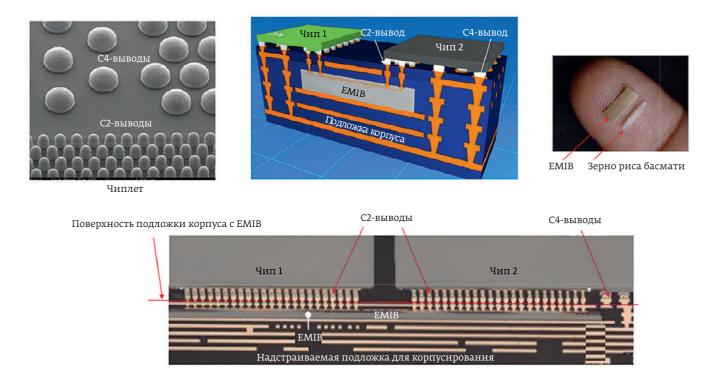

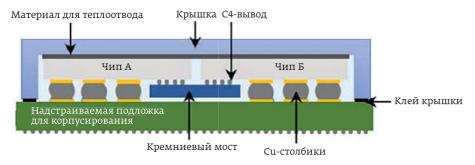

В 2016 компания Intel опубликовала первую статью о мосте для связи чиплетов. Ключевой задачей того времени было показать замену TSV-интерпозера (рис. la) на встроенный многокристальный межкомпонентный мост (Embedded Multi-die Interconnect Bridge, EMIB), как схематически показано на рис. 16 и рис. 2. Видно, что кристалл ЕМІВ встроен в полость подложки корпуса, которая поддерживает чиплеты с тонкими металлическими слоями линий перераспределения (redistribution layers, RDL). Размер такого моста очень мал, и при этом полностью отсутствует громоздкий TSV-интерпозер.

Для EMIB есть как минимум три важные задачи (рис.16 и рис. 2):

ООО «Остек-ЭК», заместитель технического директора, Sukhanov.D@ostec-group.ru.

Рис. 1. Интеграция 2,5D или 3D ИС с TSV-интерпозером (а) и чиплеты без TSV-интерпозера (EMIB) (б) [1]

Рис. 2. Решение с EMIB компании Intel [1]

- создание на пластине двух разных типов выводов для межсоединений, а именно C2-bumps, или микровыступов (неразрушаемых столбиковых выводов) и C4-bumps (припойных шариковых выводов), которые частично разрушаются при операции межсоединения, при этом у EMIB нет подобных объемных выводов (bumps);

- внедрение перемычки в полость наплавленной подложки и последующее ламинирование верхней поверхности подложки, чтобы она была достаточно плоской для соединения чиплетов;

- соединение чиплетов на подложке с помощью встроенного моста.

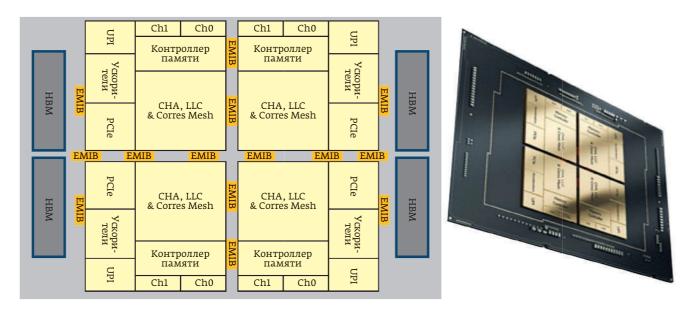

На рис. 3 показан продукт, состоящий из четырех СнК, четырех НВМ и четырнадцати EMIB.

#### ПРЯМАЯ ГЕТЕРОГЕННАЯ ИНТЕГРАЦИЯ ОТ ІВМ

Дальнейшим развитием кремниевых мостов для межсоединений стала прямая гетерогенная интеграция (Direct Bonded Heterogeneous Integration, DBHi, рис. 4), которую предложила компания IBM. Уже к 2021 году был представлен ряд материалов, изготовленных по этой технологии.

Рис. 3. Процессор Sapphire Rapids компании Intel [1]

Рис. 4. DBHi от IBM [1]

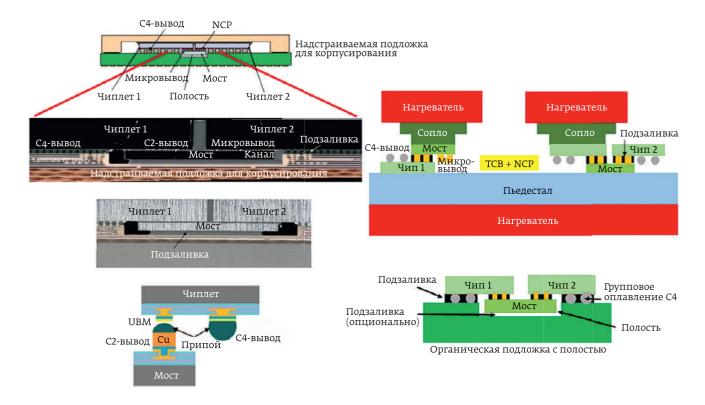

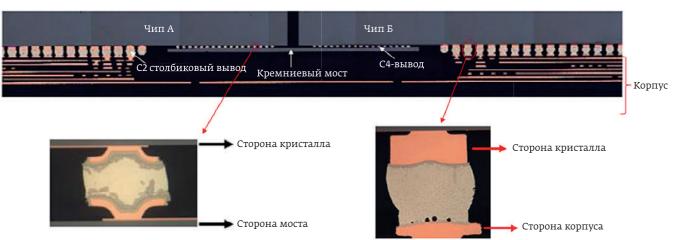

Основные различия между EMIB Intel и DBHi IBM:

- EMIB Intel содержит два типа выводов (С4 и С2) на чиплетах, а на самом мосту нет подобных выводов (рис. 2), тогда как DBHi IBM содержит только С4-выводы на чиплетах и С2-выводы на мосту (рис. 4);

- y Intel EMIB мост встроен в полость надстроенной подложки с помощью материала для монтажа кристаллов, а затем ламинирован другим слоем сверху, в то время как IBM DBHi представляет собой просто обычную подложку с полостью сверху (рис. 4).

Рис. 5. Si-мост DBHi от IBM для чиплетов на подложке корпуса сборки без полости [1]

Процесс сборки DBHi очень прост (рис. 4). Сначала на чип l наносится непроводящая паста (non-conductive paste, NCP). После этого чип l и мост соединяются с помощью термокомпрессионного соединения (thermocompression bonding, TCB). Затем NCP наносится

на мост, а чип 2 и мост соединяются с применением ТСВ. После этих шагов модуль (чип 1 + мост + чип 2) помещается на органическую подложку с полостью, а затем проходит стандартный процесс сборки с оплавлением с перевернутым чипом (reflow flip-chip).

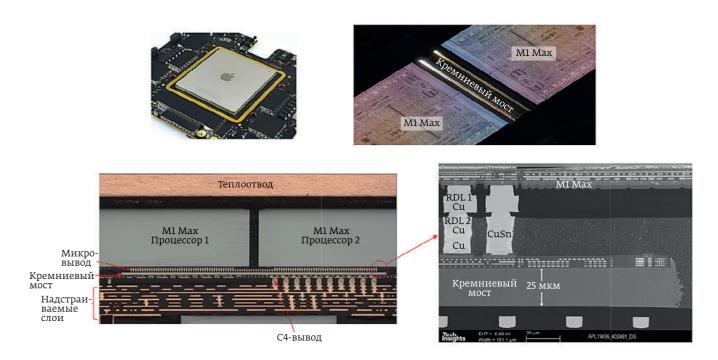

В 2023 году было продемонстрировано, что полость в подложке корпуса не является необходимой для такой технологии (рис. 5). Другие производители также представили решения без полости (рис. 6, 7).

#### ЛОКАЛЬНОЕ ПОЛУПРОВОДНИКОВОЕ СОЕДИНЕНИЕ ОТ TSMC (LSI)

В 2023 году компания TSMC опубликовала материал о замене CoWoS кремниевым мостом, встроенным в эпоксидный компаунд для заливки (ероху molding compound, EMC), с разветвленными RDL. Основная причина для использования этой технологии состоит в том, чтобы справиться с потерей уровня выхода годных при производстве с постоянно

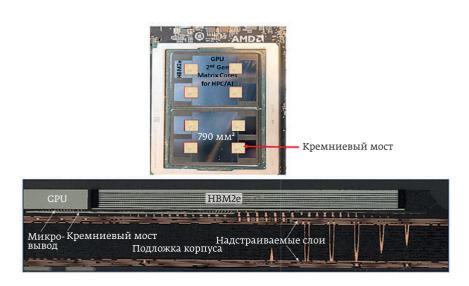

**Рис. 6.** Вычислительный ускоритель AMD Instinct™ MI250X с Si-мостом для чиплетов на подложке корпуса без полости [1]

увеличивающимся размером TSV-межсоединений. Ухудшение выхода годных настолько велико, что стоимость становится «космической».

Рассмотрим несколько примеров от TSMC (рис. 8). Использован CoWoS с шаблоном 1x (830 мм²) для Xilinx, с шаблоном 2x (1660 мм²) для Nvidia. Для шаблона  $3 \times (2500 \text{ мм}^2)$  потеря выхода годных становится слишком

велика, поэтому необходима новая технология межсоединения CoWoS-L (CoWoS + LSI + RDL, LSI – local silicon interconnect). Влияние размера TSV-интерпозера на выход годных очевидно.

На рис. 9 продемонстрирована замена TSV-интерфейса CoWoS на LSI. На рис. 9б показан кремниевый мост, встроенный в EMC с RDL (CoWoS-L). По сути, CoWoS-L -

Рис. 7. UltraFusion от Apple с Si-мостом для СнК на подложке корпуса без полости [1]

Дорожная карта TSMC для CoWoS и CoWoS-L (a) и количество TSVинтерпозеров в зависимости от их размера (б) [1]

## Ostec-Care

### Независимость от скрытых проблем

Рис. 9. Сравнение CoWoS (a) и CoWoS-L (б) компании TSMC [1]

это новый интерпозер, который состоит как минимум из LSI (или кремниевого моста) с TSV или без них и интегрированных RDL и выводов. Малогабаритный LSI унаследовал все привлекательные особенности TSV-интерпозера за счет сохранения субмикронных медных межсоединений и так называемой разводки проводников (RDL), TSV и встроенных конденсаторов с глубокими каналами для обеспечения хорошей производительности системы. В то же время LSI малого размера позволяет избежать проблем, связанных с TSV-интерпозером большого размера – потери выхода годных при производстве. Металлические проводники малогабаритного моста (LSI) имеют шаг (минимум) 0,4 мкм. И в конце концов, крупногабаритный TSV-интерпозер заменяется обновленным интерпозером, который состоит из ЕМС, малогабаритного моста (LSI) с RDL и RDL с TSV и выводами или без них.

200

Подведем итоги, опираясь на хронологию появления той или иной технологии:

• в настоящее время интеграция 2,5D и 3D ИС с TSV-интерпозерами является ключевой технологией корпусирования для высокопроизводительных вычислений, Интернета вещей, автономных

транспортных средств, для области больших данных, приложений мгновенной передачи данных, основанных на искусственном интеллекте и, конечно же, для поколений связи 5G/6G;

- потери выхода годных на производстве увеличиваются из-за постоянно увеличивающегося размера TSV-интерпозера и становятся непомерно велики, как и стоимость изделия;

- TSV-интерпозер может быть просто заменен на Si-мост с RDL;

- TSV-интерпозер может быть заменен на Si-мост с RDL, который соединяет чиплеты с помощью микровыводов, при этом на подложке корпуса отсутствуют полости;

- микровыводы могут быть заменены на соединения медных микростолбиков;

- TSV-интерпозер может быть заменен как минимум Si-мостом (с RDL и с TSV или без них) и встроен в EMC с разветвленными RDL – CoWoS-L.

В статье использованы материалы работы [1].

#### ЛИТЕРАТУРА

1. **Lau J.H.** (Unimicron Technology Corporation). Recent advances in bridges for chiplets communications // Chip Scale Review. November-December 2023.

## Современные средства измерений

# Прецизионные ИСТОЧНИКИ-ИЗМЕРИТЕЛИ

## Работают там, где другие не могут

|                | Число<br>каналов | Минимальное разрешение |                 | Ma                                             | Максимальное |

|----------------|------------------|------------------------|-----------------|------------------------------------------------|--------------|

|                |                  | Источник               | Измеритель      | Максимальный ток                               | напряжение   |

| АКИП-1601/1    | 1                | 1 пА / 100 нВ          | 1 пА / 100 нВ   | DC: ±1,05 A                                    | ±1050 B      |

| АКИП-1601/2    | 1                | 100 фА / 1 мкВ         | 10 фА / 100 нВ  | DC: ±1,515 A<br>DC: ±3,3 A<br>Импульс: ±10,5 A | ±210 B       |

| АКИП-1601/3    | 1                | 10 фА / 100 нВ         | 10 фА / 100 нВ  |                                                |              |

| АКИП-1602/1 🕝  | 1                | 10 фА / 100 нВ         | 10 фА / 100 нВ  |                                                |              |

| АКИП-1602/2 🕝  | 1                | 1 пА / 1 мкВ           | 100 фА / 100 нВ | DC: ±3,3 A                                     |              |

| АКИП-1602/3 🕝  | 1                | 100 фА / 1 мкВ         | 10 фА / 100 нВ  |                                                |              |

| АКИП-1602/4 🕝  | 1                | 1 пА / 1 мкВ           | 100 фА / 100 нВ | DC: ±1,515 A                                   | ±63 B        |

| АКИП-1602/1А 📀 | 2                | 10 фА / 100 нВ         | 10 фА / 100 нВ  | DC: ±3,3 A<br>Импульс: ±10,5 A<br>DC: ±3,3 A   | ±210 B       |

| АКИП-1602/2А 🕝 | 2                | 1 пА / 1 мкВ           | 100 фА / 100 нВ |                                                |              |

| АКИП-1602/3А 🕝 | 2                | 100 фА/1 мкВ           | 10 фА / 100 нВ  |                                                |              |