# ЮБИЛЕЙНАЯ КОНФЕРЕНЦИЯ ISSCC

# ПРОСТО О ПРОЦЕССОРАХ

#### М. Шурыгина

Каждый февраль в Сан-Франциско приезжают лучшие и самые одаренные специалисты полупроводниковой промышленности, чтобы поделиться своими достижениями на международной конференции по твердотельным схемам (International Solid-State Circuits Conference, ISSCC). Первая такая конференция (по транзисторным схемам) состоялась в 1954 году. Она была организована Институтом радиоинженеров (IRE), одним из предшественников Института инженеров по электротехнике и электронике (IEEE), в связи со стремительным ростом интереса к изобретенному в 1947 году транзистору. Появившаяся в результате развития транзисторной технологии микроэлектроника изменила мир так, как ни одна другая технология. В 2013 году состоялась юбилейная (60-я) международная конференция ISSCC. Будучи одним из основных мировых форумов, на которых представляются инновационные решения электроники, ISSCC продолжит "(ЭМ)питать будущее". Какое же будущее ждет микропроцессорную технологию?

### МНОГОЯДЕРНЫЕ ПРОЦЕССОРЫ

### Микропроцессор IBM для семейства System Z

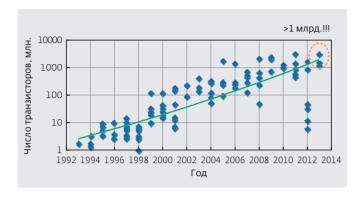

Бурное развитие полупроводниковой технологии привело к резкому повышению степени интеграции и улучшению характеристик микросхем. Если несколько лет назад степень интеграции достигала 1 млрд. транзисторов на кристалле, то сегодня уже можно найти процессоры, содержащие более 2 млрд. транзисторов на кристалле (рис.1). Этот рывок наглядно продемонстрировала корпорация IBM, представив на секции 3 ISSCC 2013, посвященной современным разработкам процессоров, микросхему шестиядерного процессора нового поколения на частоту 5,5 ГГц, содержащую 2,75 млрд. транзисторов на кристалле площадью 598 мм<sup>2</sup>. Процессор предназначен для

мейнфрейма Enterprise EC12 семейства System Z, который ІВМ анонсировала в августе 2012 года. Он изготовлен по 32-нм КНИ-технологии с диэлектриком с высокой диэлектрической постоянной и металлическим затвором (НКМС) и 15 слоями металлизации. Ядро процессора содержит L1 СОЗУ-кэши команд и данных емкостью 64 и 96 Кбит, соответственно, L2 СОЗУ команд и данных емкостью 1 Мбайт каждое и 1071 порт вводавывода. Все ядра коллективно используют расположенное на кристалле L3-кэш ДОЗУ емкостью 48 Мбайт. Чтобы обеспечить оптимальную производительность, функциональность и эффективность процессора, разработчики уделили особое внимание L1-кэшам, выполненным на основе СОЗУ с 6Т-ячейками площадью 0,291 мкм<sup>2</sup> с однофазным считыванием и двухфазной записью.

Многокристальный модуль мейнфрейма должен содержать шесть микросхем процессора, смонтированных на стеклокерамическом 102-слойном основании размером 96×96 мм. В модуле также размещены две микросхемы L4-кэш ДОЗУ емкостью 192 Мбайт каждое (3,3 млрд. транзисторов размещены на площади 526 мм<sup>2</sup>). Пропускная способность ряда сигнальных линий, расположенных в 39 слоях основания, составляет 2,75 Гбит/с, пропускная способность 36-ядерного модуля - 530 Гбайт/с.

Проблема обеспечения требуемой производительности процессора решена с помощью методики, получившей название "структурированный синтез большого блока" (Large Block Structured Synthesis, LBSS). Предложены новые алгоритмы формирования потока данных в контексте синтезируемых блоков большего размера. Успешное применение LBSS-методики привело к переходу от проектирования транзисторной логики, отвечающей в основном требованиям потребителя, к автоматизированному синтезу логики. Для подачи сигналов ФАПЧ использован специализированный блок буферизации и трассировки. Неиспользуемые ядра на входе синхронного сигнала каждого ядра отключабтся с помощью блоков программирования задержки сигнала и контроля рабочего режима.

Различная температурная нестабильность диэлектриков затвора с высоким k вызвала необходимость изучения влияния продолжительности подачи напряжения на длительность импульсов и запирание передающих вентилей. В результате обнаружено, что допустимый коэффициент ошибок при записи со временем растет, что и было подтверждено полученными на основе статического анализа изменениями параметров в конце срока службы прибора.

В микросхемах процессоров использованы глубокие щелевые развязывающие конденсаторы (емкостью более 24 мк $\Phi$  в основном канале и ~6 мк $\Phi$  – в остальных), что позволило отказаться от применения конденсаторов на монтажной керамической пластине.

Корпорация производит свои микросхемы на заводе в East Fishkill по разработанной совместно с контрактной компанией GlobalFoundries технологии.

На демонстрационной секции конференции IBM представила поставленный заказчику мейнфрейм Enterprise EC12, содержащий четыре модуля. На вопрос: "Продолжит ли IBM "запускать" частоту?" докладчик ответил: "Возможно, хотя

**Рис.1.** Динамика увеличения сложности цифровых микросхем

потребуется рассмотреть различные варианты конструкции". Правда, рост частоты не может быть бесконечным [1].

## Укрощение ягуара

Если IBM при создании процессора для System Z ставила задачу получения предельно возможной производительности, то основными достоинствами микроархитектуры Jaguar, представленной компанией AMD на той же секции 3 ISSCC, были малые значения потребляемой мощности и занимаемой площади кристалла: максимальная мощность - от менее 5 до 25 Вт, площадь кристалла - 26,2 мм². Jaguar\* - прямой наследник архитектуры Bobcat - также ориентирован на применение в гибридных АРИ-процессорах. Нельзя сказать, что компания сообщила о совершенно новой разработке. Еще летом 2012 года она достаточно подробно описала архитектуру двухъядерного процессора Jaguar на симпозиуме Hot Chips ("Горячие чипы"), а в феврале этого года Sony объявила о планах начать продажи игровой приставки PlayStation 4, центральный процессор которой содержит восемь процессорных ядер Jaguar. Поэтому доклад АМD, раскрывший ряд достоинств процессора, который позволит компании восстановить конкурентоспособность в сегменте рынка центральных процессоров с малым энергопотреблением, вызвал большой интерес участников конференции.

Для улучшения эксплуатационных характеристик процессоров на основе ядер Jaguar по сравнению с Bobcat-устройствами компания не стала

<sup>\*</sup> Отметим, что x86 совместимые архитектуры AMD можно разделить на две категории: семейство "строительной техники" (Bulldozer, Piledriver и следующие поколения) и семейство "кошачьих" (Bobcat, Jaguar и следующие архитектуры).

создавать совершенно новую архитектуру, а лишь усовершенствовала конструктивное исполнение предшествующей архитектуры. Во-первых, х86совместимые процессоры Jaguar изготавливаются тайваньской компанией TMSC по 28-нм (а не 40-нм) НКМС-технологии с 11-слойной металлизацией. С помощью стандартных средств размещения элементов и трассировки соединений разработчики смогли выполнить процессорное ядро в виде одного блока площадью всего 3,1 мм<sup>2</sup>.

По сравнению с Bobcat, AMD удалось увеличить число инструкций, исполняемых процессорным ядром Jaguar за такт (IPC), на 15% и на 10% - его частотный потенциал (процессор может работать на частоте до 1,85 ГГц), а также энергетическую эффективность. Ширина шины физического адреса увеличена с 36 до 40 разрядов, блока вычислений с плавающей запятой - с 64 до 128 разрядов. Пропускная способность процессора при загрузке с запоминанием составляет 16 байт/цикл (вдвое больше, чем у Bobcat), в сравнении с Bobcat он обрабатывает на 50% более длинную очередь команд, поступающую от планировщика. Улучшена технология Power Gating (управления мощностью), что позволяет полностью перекрывать питание неактивных ядер.

Важнейший фактор, который позволит АМД "побороть" конкурентов, - поддержка расширенного набора инструкций, характерного для процессоров основного рыночного сегмента. К инструкциям, реализуемым процессором Bobcat, у Jaguar добавились новые, в том числе код AVX (Advanced Vector Extensions), а также потоковые SIMD-расширения SSSE3, SSE4.1, SSE4.2 и SSE4A, получившие достаточно широкое распространение в современных медийных приложениях. Добавлен поднабор инструкций продвинутого стандарта шифрования AES - AES-NI

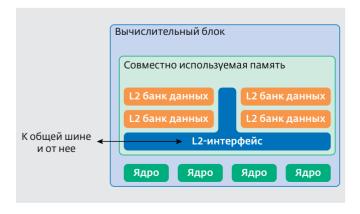

Puc.2. Структура вычислительного блока Jaguar

(AES New Instructions), ускоряющих выполнение операций шифрования/дешифрования в рамках стандарта AES.

Решения на базе Jaguar имеют модульную конструкцию и состоят из вычислительных блоков (Compute Units, CU) площадью 26,2 мм<sup>2</sup>. CU содержит до четырех независимых процессорных ядер Jaguar и совместно используемую 2-Мбайт L2 кэш-память, состоящую из четырех банков емкостью 512 Кбайт каждый, доступ к которым не зависит от числа активных ядер (рис.2). В Bobcat также по 512 Кбайт L2 кэш-памяти на ядро, но ядер всего два. Доступ процессорных ядер к кэш-памяти независимо от числа активных ядер обеспечивает общая для всех шина через специальный интерфейс, который также связан с системной логикой [2].

23 мая этого года AMD объявила о выпуске двух гибридных APU-процессоров на основе ядер Jaguar:

- Elite Mobility APU (кодовое название Temash), первые в мире 28-нм системы на кристалле с малым энергопотреблением (5-8 Вт), предназначенные для сенсорных ноутбуков, планшетников и гибридных компьютеров с 13-дюймовыми и менее экранами. Ожидается, что Elite Mobility APU станет самой производительной однокристальной платформой для планшетников:

- Mainstream APU (кодовое название Kabini), первые и пока единственные в мире однокристальные системы на кристалле для сенсорных ноутбуков начального уровня с сенсорным дисплеем и большим временем автономной работы (более 10 ч в режиме простоя, более 9 ч в сети и более 6 ч в режиме просмотра видео с разрешением 1080р) [3].

AMD прямо не сообщила о возможности создания процессоров с более чем четырьмя ядрами Jaguar, но отметила вероятность появления процессоров с более чем одним вычислительным блоком, т.е. шести- или даже восьмиядерных процессоров. Кстати, в грядущей игровой консоли Xbox компания Microsoft, по слухам, использует CPU с восемью ядрами Jaguar, как, впрочем, и игровая приставка Sony. Компания AMD не намерена останавливаться на достигнутом и уже готовит замену линейки APU-процессоров Kabini серией гибридных процессоров Веета. Из технической спецификации этих процессоров известно, что они будут выполнены на основе несколько модифицированной микроархитектуры Jaguar+ и, что наиболее вероятно, следующего поколения интегрированной графики компании AMD. Традиционно, новинки будут

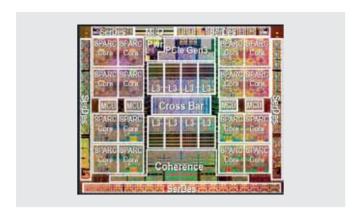

Рис.3. Структура процессора Spark-T5

характеризоваться высоким уровнем производительности и оптимизированными показателями мощности потребления. В продажу APU серии AMD Веета должны поступить в 2014 году.

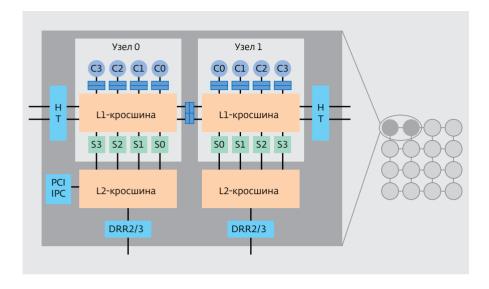

# Самый производительный, по утверждению создателя, серверный процессор

Компания Oracle описала серверный процессор следующего поколения SPARC T5, выполненный по 28-нм технологии с 13-слойной металлизацией и содержащий 1,5 млрд. транзисторов на площади кристалла 478 мм<sup>2</sup>. Микропроцессор с 16 ядрами работает на частоте 3,6 ГГц, поддерживая восемь потоков команд на одно ядро (одновременно до 128 потоков команд). Каждое ядро имеет встроенные аппаратные ускорители шифрования AES/DES, обмена ключами RSA, хеширования SHA/MD5, аппаратный генератор случайных чисел. Микросхема также содержит совместно используемую L3 кэшпамять емкостью 8 Мбайт, L2-кэш ядер емкостью 128 Кбайт, L1-кэши данных и команд емкостью 16 Кбайт каждый и матричный коммутатор на девять портов. Поддерживается интерфейс РСІе 3.0 и четыре контроллера памяти DDR3 (рис.3). В сравнении с 40-нм процессором SPARC Т4 предыдущего поколения, в новой микросхеме вдвое увеличены число ядер и емкость L3 кэш-памяти, а пропускная способность памяти - в три раза. Производительность новой архитектуры системы ввода-вывода данных равна 5 Тбайт/с. Процессоры входят в состав недавно представленного компанией сервера SPARC T5, который может содержать до восьми сокетов (т.е. 128 вычислительных ядер) [4, 5].

## Китайские многоядерные процессоры 24-ядерный процессор

Тема поиска дальнейших возможностей компьютеризации проявилась и в новейших

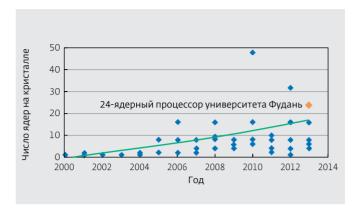

Рис.4. Динамика увеличения числа ядер на кристалле

проектах, представленных на конференции ISSCC этого года. Изготовители процессоров в стремлении сократить энергопотребление снижают напряжение питания разрабатываемых схем, поступаясь их производительностью. Для компенсации потерь в производительности они увеличивают степень параллелизма микросхем. Как видно из предыдущих докладов, для процессоров наступила "ядерная эра" и схемы с более чем восемью ядрами становятся обыденными (рис.4). Но с увеличением числа ядер все более сложным становится обеспечение связи между ними для своевременного и точного выполнения поставленных задач. И здесь интерес представляет решение, принятое специалистами шанхайского университета Фудань при создании высокопроизводительного и энергоэффективного процессора с 24 ядрами на одном кристалле. Отличительные особенности процессора:

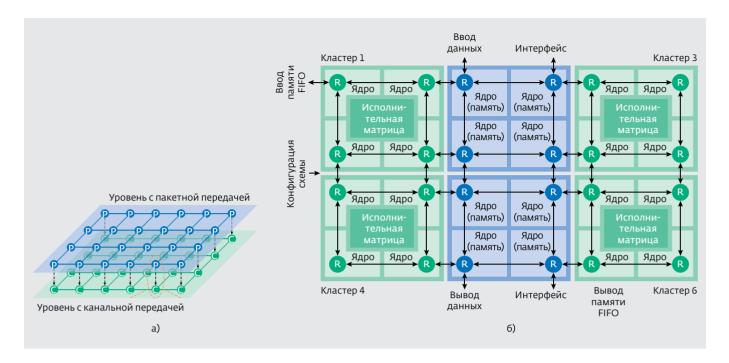

• двухсекционная архитектура сети на кристалле (network-on-chip, NoC), энергоэффективность которой составляет 11 Тбит/с/Вт, а общая производительность двух секций – 435 Гбит/с;

Рис.5. Двухуровневая сеть на кристалле (а) и структура 24-ядерного процессора (б)

- гетерогенная реконфигурируемая матрица процессоров секций NoC, позволяющая улучшить производительность схемы при выполнении вычислений в мультимедиа и коммуникационных приложениях;

- улучшенная иерархия памяти, включая наличие приоритетной многостраничной памяти и низкоприоритетного регистрового файла, а также секционирование и совместное использование памяти.

Сеть на кристалле формируют две 4×6 матрицы процессорных ядер: одна с пакетной коммутацией данных (в дальнейшем пакетная сеть), расположенная над такой же матрицей с канальной передачей (канальная сеть), управляемой с помощью пакетной передачи. Каждое ядро одной из матриц может контактировать с соседними ядрами своей матрицы и матрицы другой секции (рис.5а). Пакетная сеть - более гибкая и хорошо изученная, но она может передавать лишь небольшие объемы данных. Канальная сеть отличается высокой энергоэффективностью (при передаче данных объемом более 33 слов энергопотребление ее меньше, чем у пакетной сети), но ее трудно реконфигурировать. В двухсекционной сети пакетная секция может пересылать канальной параметры реконфигурации схемы. Поскольку в пакетной секции передаются данные малого объема, емкость FIFO-памяти, включенной между процессорным ядром и сетью,

невелика, хотя для разводки линий требуется 75% площади сети и доля потребляемой мощности секции в общем энергопотреблении тоже составляет 75%. В пакетном уровне используется координатный алгоритм маршрутизации, маршрутизация в канальном уровне полностью задается записанной программой.

Ядра распределены по шести кластерам (рис.5б), каждый из которых имеет собственный управляемый напряжением генератор на частоту 400 МГц-2 ГГц. Для сбора данных в узле назначения тактовый сигнал передается совместно с разрядом данных. По мнению разработчиков, при такой синхронизации частота тактового сигнала не будет ограничена дальностью связи. Все ядра одинаковые, но кластеры отличаются. Два представляют собой гетерогенные реконфигурируемые матрицы, содержащие 16 исполнительных процессорных блоков, которые соединены упрощенной канальной сетью, управляемой пакетной коммутацией. Исполнительные блоки выполняют различные функции, в том числе БПФ четырех точек, умножения/деления, арифметические/логические. Два других кластера связаны с внешней памятью, причем емкость их памяти данных вдвое больше, чем у кластеров первого типа.

Процессор выполнен ПО 65-нм КМОПтехнологии изготовления микросхем с малым энергопотреблением компании TSMC. Занимает

**Рис.6.** Блок схема ядра GS464V, используемого в процессоре Godson-3B1500

площадь кристалла 18,8 мм<sup>2</sup>, работает на частоте 850 МГц при напряжении 1,2 В и рассеиваемой мощности 523 Вт. Это соответствует энергетической эффективности 39·10<sup>9</sup> операций/с/Вт (26 пДж/операцию), что в 1,75 раза лучше, чем у предыдущего 16-ядерного процессора университета Фудань [6].

#### Godson

Своеобразной традицией при рассмотрении работ, представленных на ISSCC, стал рассказ об очередном улучшении китайского процессора Godson (божий сын). Надо сказать, что разработчик - Институт компьютерных технологий (Institute of Computing Technology) - обещает выпустить его 28-нм версию осенью этого года. Но на конференции ISSCC был представлен серверный 64-разрядный восьмиядерный процессор Godson-3B1500, работающий с набором команд Mips64\*. Он выполнен компанией Loongson Technology по 32-нм КМОП НКМСтехнологии с десятислойной медной металлизацией и содержит 1,14 млрд. транзисторов на кристалле площадью 182,5 мм². Благодаря усовершенствованию архитектуры Godson-3B1500 работает при значениях напряжения от 1,0 до 1,3 В на частоте 1,0-1,5 ГГц. Производительность на операциях удвоенной точности с плавающей запятой составляет 172,8 CFLOPS на частоте 1,35 ГГц. Максимальная потребляемая мощность - 40 Вт, т.е. энергетическая эффективность улучшена на

35% по сравнению с процессором предыдущего поколения Godson-3B.

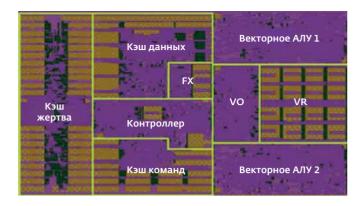

Новый процессор семейства Godson содержит ядра GS464V усовершенствованной версии, которые объединены в два вычислительных блока. Модернизированное ядро имеет два 256-разрядных векторных АЛУ, каждый с четырьмя процессорами компании MADD Electronics Group, и 128-разрядный ARM-интерфейс стандарта АХІ (рис.6). Ядра могут работать на различных частотах и при различных напряжениях, для чего предусмотрены схемы сдвига уровня, изоляция логики, асинхронная память FIFO, динамическое изменение частоты и напряжения.

При создании процессора Godson-3B1500 в архитектуру Godson-3B были внесены два изменения. Во-первых, изменены емкости кэш-памяти:

- емкость L1-кэш данных ядра увеличена с 32К до 64 Кбайт и стала равна емкости кэш-памяти команд;

- в ядро введена новая четырехвходовая кэшпамять жертв собственной разработки емкостью 128 Кбайт;

- емкость общей для всех ядер кэш-памяти последнего уровня (last-level cache, LLC) увеличена с 4 до 8 Мбайт.

Второе изменение, внесенное в архитектуру, касается увеличения быстродействия вводавывода данных. Вместо гипертранспортной (НТ) шины версии 1 использована НТ-шина версии 2 разработки ARM (рис.7). Кроме того, DDRII 800 интерфейс доступа к памяти заменен DDRIII 1200 интерфейсом с дополнительным многоканальным контроллером, поддерживающим пропускную способность используемой памяти DDR2/3, равной до 153,6 Гбит/с. Для контроля изменений условий работы процессора в схеме предусмотрены ИК-датчики и детектор напряжения [7].

<sup>\*</sup> Процессоры семейства Godson разрабатываются компанией Loongson Technology при участии и финансировании Академии наук КНР с 2002 года. Архитектура MIPS64 была лицензирована в 2007 году через компанию STMicroelectronics и подверглась модификации.

**Рис.7.** Архитектура микропроцессора Godson-3B1500

Осенью этого года Loongson планирует начать поставки процессора с 28-им проектными нормами десяти китайским производителям серверов, в том числе Dawning, Great Wall и Inspur. Выполнение этого плана будет означать осуществление давней мечты китайских технократов создание отечественного компьютера на основе отечественного микропроцессора.

# ПРОЦЕССОРЫ ДЛЯ МОБИЛЬНЫХ УСТРОЙСТВ

# Архитектура "большой.малый"

Потребность в улучшении восприятия пользователями мобильных устройств и в продлении срока службы их батарей стимулировала применение новейших технологий и архитектурных решений при разработке процессоров приложений. Достижения в этой области вызвали большой интерес специалистов, присутствовавших

Рис.8. Структура процессора Exynos Octa с двумя кластерами четырехканальных процессоров

на секции 9, посвященной процессорам приложений и ускорителям аудиовидеоопераций мобильных устройств. Чуть ли ни центральным выступлением конференции стал доклад компании Samsung, посвященный 32-нм системе на кристалле Exynos Octa, в основу которой положена широко разрекламированная компанией ARM технология big.little (большой. малый) [8].

Цель применения такой гибридной архитектуры с двумя типами центральных четырехъядерных процессоров -Cortex-A7 с меньшей производительностью, но большей, чем

у Cortex-A15, энергоэффективностью, для выполнения основных операций мобильного устройства, и Cortex-A15 для решения самых интенсивных задач. Однако по сравнению с Cortex-A7 площадь, занимаемая процессором Cortex-A15, оказалась в пять раз больше (19 против  $3.8 \text{ мм}^2$ ) (рис.8), а потребляемая мощность - почти в шесть раз выше: производительность по эталонной тестовой программе Dhrystone "большого" процессора составляла 30 тыс. при мощности 6 Вт, а "соседа" -8 тыс. при 0,5 Вт.

Как и в варианте 32-нм центрального процессора Exynos на основе четырехъядерного Cortex-A9, который компания Samsung подробно описала на конференции ISSCC 2012 [9], в новом процессоре для регулировки потребляемой мощности и производительности используются аналоговые методы динамического управления прямым и обратным смещением кристалла. Каждый процессор может быть полностью отключен, а затем за счет управления напряжением и частотой каждое ядро может быть активизировано индивидуально. Для оптимизации производительности и потребляемой мощности разработчики пересмотрели библиотеку моделей на уровне регистровых передач с точки зрения уменьшения числа вентилей для логического синтеза и библиотеку ядер с точки зрения критических каналов передачи данных.

В зависимости от отклонений процесса производства рабочая частота "больших" процессоров составляет от 200 МГц до 1,8 ГГц, "малых" от 200 МГц до несколько больше 1,2 ГГц. Емкость L2 кэш-памяти данных процессоров Cortex-A15

равна 2 Мбайт, Cortex-A7 – 512 Кбайт. Оба кластера процессоров совместно пользуются когерентной шиной, позволяющей переключать программное приложение между двумя процессорами менее чем за 20 тыс. тактовых циклов.

Отвечая на вопросы специалистов относительно свойств и рентабельности процессора с архитектурой big.little, докладчик неизменно отвечал, что реальная работа процессора зависит от программных средств приложения и используемой операционной системы, а он всего лишь разработчик схемы, а не софта. Ожидается, что планируемый к выпуску в этом году процессор Exynos Octa будет применен в планшетных компьютерах и сможет конкурировать с 22-нм процессором Haswell компании Intel. Кроме того, по мнению специалистов компании Samsung, он перспективен и для 3D игровых систем, и для устройств воспроизведения видеозаписи мобильных устройств. Но для подтверждения этого потребуется тщательное тестирование работы процессора в мобильных устройствах [10].

## Еще один процессор Samsung

Во втором докладе на секции 9 компания Samsung описала "сочлененный" мультимедийный процессор, содержащий центральный процессор с ARM v7a-архитектурой (тактовая частота 1,7 ГГц), универсальный графический процессор (GPGPU) с многоформатным видеокодеком и подсистему памяти с пропускной способностью 12,8 Гбайт/с. Кодек обрабатывает 240 Мпикселей/с при частоте 60 кадров/с и разрешении 1080р.

В микросхему процессора входят пять процессорных ядер и подсистема обработки изображения, ускоряющая воспроизведение видеоданных. В нем предусмотрено параллельное выполнение задач, параллельная работа конвейеров и ядер, а также ее регулировка. Возможно управление межъядерным конвейерным режимом работы и обменом данными между памятью ядер "на лету". Система управления питанием позволяет формировать значения потребляемой мощности каждого центрального и графического процессоров, памяти и логических устройств. Кроме того, для максимального

снижения энергопотребления предусмотрена регулировка подачи тактового импульса. При использовании специализированных маломощных мультимедийных графических ускорителей, а также технологии изготовления маломощных устройств на основе предложенной микросхемы возможно создание устройств для следующего поколения мультимедийных приложений [11].

## Другие процессоры приложений

Представитель компании Renesas подробно рассказал о предназначенной для мобильных устройств системе на кристалле, содержащей двухъядерный (Cortex-A9) процессор, многорежимный LTE/HSPA-модем, 2D/3D графические ускорители и блок управления электропитанием. Система выполнена по 28-нм НКМС-технологии и содержит 724,79 млн. транзисторов, размещенных на кристалле площадью 478 мм<sup>2</sup>. Тактовая частота равна 1,5 ГГц, потребляемая мощность по тестовой программе Dhrystone - 640 мВт на 1,2 ГГц [12].

Интерес вызвал И доклад ученых Массачусетского технологического института, в котором был описан реконфигурируемый процессор для компьютерной фотографии. Он рассчитан на поддержку функций обработки изображения в расширенном динамическом диапазоне (HDR). Это позволяет формировать сложную картинку на основе многочисленных изображений с различной фотоэкспозицией. Возможно получение HDR-изображения с тональной компрессией, качественного снимка при низком уровне освещенности, в котором объединены изображения, снятые со вспышкой и без нее.

Основной блок реконфигурируемого процессора - билатеральный фильтр, состоящий из блока установки координатной сетки, устройства поворота, блока, выполняющего функцию интерполяции. Все элементы фильтра соединены трехмерной структурой передачи данных, названной билатеральной сеткой. При обработке изображение разделяется на интенсивные точки сетки, и изображения подсеток сортируются по интенсивности и значимости. Для обработки изображения в 10 Мпикселов в процессоре предусмотрена память емкостью 665 Мбайт.

Процессор выполнен по 40-нм КМОПтехнологии. Работает при напряжении питания 0,5-0,9 В (напряжение на входе-выходе - 1,8-2,5 В). При 0,5 В частота процессора составляет 25 МГц, при 0,9 В - 98 МГц. Потребляемая мощность -2,7 мВт [11].

## ПРОЦЕССОРЫ СО СВЕРХНИЗКИМ **ЭНЕРГОПОТРЕБЛЕНИЕМ**

## Процессор, работающий при напряжении питания, близком к пороговому значению

Энергоэффективная обработка данных имеет важное значение и для широкого спектра новых приложений - от технологии мониторинга различных жизненных показателей человека (Body Area Networks, BAN) до автоматизации зданий и контроля параметров оборудования. Сокращение энергопотребления в рабочем режиме и утечки в режиме ожидания становится все более важным фактором, который необходимо учитывать при проектировании цифровых схем. Однако значительная часть исследований по-прежнему направлена на повышение эффективности, а не на увеличение срока службы батарей благодаря повышению эффективности энергопотребления.

Решению этой проблемы способствует разработанный учеными бельгийского центра прикладных разработок в сфере микро- и наноэлектроники IMEC и научно-исследовательского центра Holst Centre процессор со сверхнизким энергопотреблением, надежно работающий при напряжении питания, близком к пороговому. Тактовая частота процессора достигает 1 МГц при напряжении, равном 0,4 В. При выполнении БПФ потребляемая мощность процессора составила 79 мкВт, т.е. ничтожную долю мощности, потребляемой при стандартных значениях напряжения.

Процессор содержит 32-разрядные функциональные устройства, обеспечивающие регулировку напряжения с помощью динамически реконфигурируемых блоков. Снижение рабочего напряжения при обеспечении производительности, необходимой для нормальной работы микросхемы и надежного ее удержания в диапазоне рабочих напряжений и температур, оказалось возможным в результате прямого смещения транзисторов процессора. Это позволило ему работать при значении напряжения несколько выше порогового, присущего используемым КМОПтранзисторам. Рабочее напряжение в зависимости от текущих требований к производительности может регулироваться в пределах номинального значения напряжения процессора, равного 1,1 В, и минимального значения 0,4 В.

Естественные отклонения техпроцесса при изготовлении процессора могут привести к колебаниям напряжения при его работе.

При значениях напряжения, близких к пороговому, эти колебания могут быть достаточными для прекращения работы процессора. Чтобы избежать этого, разработчики присоединили к наиболее важным блокам с жестким временным режимом специализированные триггеры, так называемые canary-триггеры, которые отключаются до отказа подключенных блоков, позволяя повысить их рабочее напряжение прежде, чем шумы повлияют на работу процессора. Кроме того, автоматическая регулировка смещения устраняет падение напряжения силовых ключей, что также повышает энергоэффективность и надежность процессора в условиях работы при напряжении, близком к пороговому значению.

Процессор предназначен для биомедицинских приложений, например, для считывания данных ЭКГ и ЭЭГ. Для этого была разработана архитектура интерфейса ядра процессора, обеспечивающая работу при сверхнизком напряжении и автоматическую регулировку требуемой для конкретного приложения производительности. Кроме того, проводится непосредственный мониторинг работы процессора, гарантирующий его высокую надежность. Интерфейс позволяет индивидуально управлять состоянием отдельных компонентов микросхемы, например, отключать процессорное ядро или снижать напряжение блоков памяти, когда эти компоненты не требуются. Кроме того, с помощью программного интерфейса можно динамически переключать режимы работы процессора, оптимизируя число активных функциональных блоков в соответствии с выполняемым алгоритмом. Функциональные блоки, неиспользуемые в работе, для снижения потребления энергии отключаются [13].

## Хорошо спим и быстро просыпаемся

Энергоэффективность имеет первостепенное значение и для будущих поколений систем на кристалле. Но для снижения потребляемой мощности таких систем требуются все новые высокотехнологичные методы. Это и объясняет интерес, проявленный к созданному компанией Texas Instruments процессору на основе ядра Cortex-M0 с нулевым энергопотреблением в режиме ожидания и временем "пробуждения" 400 нс. Это достигнуто благодаря применению в нем сегнетоэлектрического ОЗУ (FRAM), 256-бит ячейки памяти которого на основе сегнетоэлектрических конденсаторов распределены среди логических элементов и хранят состояние триггеров, не потребляя энергию. Компания отказалась от применения

централизованной сегнетоэлектрической памяти большой емкости из-за большого времени активизации, стоимости трассировки и потребляемой мощности, обусловленных отсутствием параллельного доступа к триггерам.

Помимо ядра и FRAM емкостью 64 Кбайт схема содержит постоянную память емкостью 10 Кбайт, 8-Кбайт СОЗУ, а также UART- и SPI-интерфейсы. Выполнена микросхема по 0,13-мкм технологии. Тактовая частота системного блока составляет 9 МГц, энергонезависимой памяти – 125 МГц. Потребляемый ток при выполнении команд СОЗУ и FRAM равен 75 и 170 мкА/МГц, соответственно, потребляемая энергия поддержки и хранения состояния всей системы, содержащей 2537 триггеров, СОЗУ и FRAM,- 4,72/320 и 1,34/384 нДж/нс, соответственно. Напряжение питания схемы -1.5 B.

Микросхема рассчитана на применение в приложениях с питанием аккумулированной энергией и в ручных приборах с ограниченным охлаждением: сенсорных узлах и носимых электронных устройствах, электронных системах здравоохранения, интеллигентных РЧ-идентификаторах и другом оборудовании, требующем сверхнизкого энергопотребления [14].

## НЕ ПРОЦЕССОРЫ, НО ГДЕ-ТО РЯДОМ С НИМИ

Рассматривая процессоры, представленные на ISSCC 2013, следует отметить, что впервые за много лет компания Intel не сообщила ни о грядущем 22-нм процессоре Haswell, ни о каком-либо другом разрабатываемом процессоре. Не представила систему на кристалле Project Denver и компания Nvidia. Обе компании рассказали о системах межсхемного интерфейса. Цель их работ - сокращение затрат на ввод-вывод данных, площади кристалла, занимаемой блоками, выполняющими эти функции, и потребляемой мощности современных высокоэффективных компьютерных

Выступление представителя микропроцессорного гиганта Intel было посвящено маломощной высокоскоростной 64-канальной системе вводавывода данных с суммарной пропускной способностью порта 1 Тбит/с и энергетической эффективностью 2,6 пДж/бит. Для получения высокой плотности соединений специалисты компании использовали соединители с высокой плотностью контактов Ardent Concepts и микрокабели Samtec, присоединяемые к верхней стороне корпуса. Сейчас это довольно широкие кабели с диаметром проводов 0,5 мм. В перспективе диаметр жгута

не будет превышать 1-2 мм. Отказоустойчивость системы обеспечивает механизм восстановления работы неисправного канала. Применение блоков с различными значениями мощности, таких как блок КМОП-синхронизации и реконфигурируемый драйвер передатчика на токовых переключателях или переключателях напряжения, позволило регулировать пропускную способность в диапазоне 0,128-1 Тбит/с и нелинейную энергоэффективность в диапазоне 0,8-2,6 пДж/бит при изменении напряжения питания в интервале 0,6-1,08 В. Потребляемая мощность схемы составляет 2,6 мВт.

Пока Intel никак не привязывает представленный интерфейс к своим процессорным архитектурам, но в будущем он наверняка попадет в суперсерверные платформы. Правда, отмечается, что путь до коммерциализации системы интерфейса очень длинный.

Специалисты компании Nvidia описали синхронизированный во времени несимметричный последовательный канал, обеспечивающий связь на коротком расстоянии между кристаллами, смонтированными в одном корпусе. Канал реализован в 28-нм КМОП-микросхеме. Его пропускная способность составляет 20 Гбит/с. Напряжение питания - 0,9 В, энергетическая эффективность - 0,54 пДж/бит. Докладчик не привязал разработку ни к графическому процессору Tesla, что могло бы свидетельствовать о новом уровне его масштабируемости, ни к проекту Denver [15].

0.00

Тенденции к снижению рабочего напряжения микросхем и, следовательно, сокращению потребляемой энергии, а также к уменьшению площади схемы, реализующей специфические функции, не прекращаются. Это относится и к микропроцессорам. Процессоры, представленные на конференции ISSCC 2013, выполнены по различным вариантам. При этом лучшие результаты достигнуты по таким показателям, как увеличение уровня интеграции, улучшение отношения производительность-потребляемая мощность, рост функциональности. Описано несколько впервые реализованных в промышленности микросхем с проектными нормами от 0,13 мкм до 28 нм. Развитие этих тенденций, конечно же, не прекратится. Подождем, что покажут крупные разработчики и производители микропроцессоров, в том числе и Intel, и Nvidia в 2014 году.

### ЛИТЕРАТУРА

- **Dempsey P.** ISSCC 2013: IBM adds digital logic synthesis methodology for System z. - www. techdesignforums.com/blog/2013/02/20/isscc-2013-ibmdevelops-new-digital-logic-synthesis-methodology-forsystem-z/

- **Dempsey P.** ISSCC 2013: AMD constraints help tame Jaguar. - www.techdesignforums.com/blog/2013/02/21/ isscc-2013-amd-jaguar

- AMD Amplifies Mobile Experience with Responsive Performance, Rich Graphics, Elite Software and Long Battery Life. - www.amd.com/us/press-releases/Pages/ amd-rejuvenates-mobile-2013may23.aspx

- 4. **Shilov A.** Oracle Unveils 16-Core SPARC-T5 Processors. New Servers. - www.xbitlabs.com/news/other/ display/20130328053158\_Oracle\_Unveils\_16\_Core\_ SPARC\_T5\_Processors\_New\_Servers.html

- SPARC T5 PROCESSOR. ORACLE DATA SHEET www. oracle.com/us/products/servers-storage/servers/sparc/ oracle-sparc/t5-processor-ds-1922863.pdf

- Wilson R. Dual networks cut power on 24-core multimedia chip. - www.electronicsweekly.com/news/ design/embedded-systems/dual-networks-cut-power-on-24-core-multimedia-chip-2013-03

- Merritt R. Slideshow: China's Godson processors to power servers in 2014. - www.eetimes.com/General/ PrintView/4407272

- М.Шурыгина. Инновации на уровне ядра. Энергоэффективные процессорные архитектуры. - Электроника: НТБ, 2012, №8, с.

- Гольцова М. Конференция ISSCC. Кремний основа устойчивого развития современного мира. - Электроника: НТБ, 2012, №3,с.72-84.

- 10. Samsung details Exynos Octa at 60th ISSCC. -www. eedailynews.com/2013/02/samsung-details-exynos-octaat-60th.html

- 11. ISSCC 2013 Session 9 Mobile Application Processors & Media Accelerators. - mandetech.com/2013/03/17/isscc-2013-session-9-mobile-application-processors-mediaaccelerators

- 12. **R.Merritt.** Slideshow: Samsung cagey on smartphone SoC at ISSCC. -www.eetimes.com/electronicsnews/4407832/Slideshow-Mobile-at-ISSCC-with-Samsung-Mediatek?pageNumber=2

- 13. Ultra-low power processor operates at near-threshold voltage. - IMEC News - www2.imec.be/be\_en/press/ imec-news/ulp2013.ht

- 14. **Bush S.** ISSCC: Cortex-M0 sleeps on nothing and wakes in 400ns. - www.electronicsweekly.com/news/design/ embedded-systems/isscc-cortex-m0-sleeps-on-nothingand-wakes-in-400ns-2013-02/

- 15. Notable Papers at ISSCC 2013. www.cdrinfo.com/ sections/news/Details.aspx?NewsId=34926