## COBPEMEHHЫE CAПР SYNOPSYS -

# НОВЫЕ ВОЗМОЖНОСТИ ДЛЯ ТРАДИЦИОННЫХ ТЕХНОЛОГИЙ

Д.Радченко, главный инженер-консультант по САПР, Synopsys Dmitry.Radchenko@synopsys.com

Сегодня взгляды многих разработчиков передовых системна-кристалле (СнК) устремлены на технологические процессы со все меньшими топологическими нормами. Уже стали реальностью технологии уровня 20/22 нм, осваивается уровень 14 нм, микроэлектронный мир вплотную подошел к разрешению в 10 нм, еще несколько лет назад считавшемуся непреодолимым в силу фундаментальных ограничений. Может сложиться впечатление, что разработка и изготовление передовых ИС на основе полупроводниковых технологий уровня 40/65 нм и выше сегодня уже неактуальна. Однако на практике дело обстоит не так – для очень многих задач эти технологии не только достаточны, но и оптимальны. Но для того, чтобы в полной мере раскрыть потенциал этих технологий, решать на их основе задачи создания современных СнК, необходимы самые передовые методологии и системы автоматизированного проектирования (САПР). В частности, методологии и инструменты проектирования, созданные компанией Synopsys для применения в новейших технологиях, открывают новые возможности и в рамках более традиционных технологических процессов.

### ТРАДИЦИОННЫЕ ТЕХНОЛОГИИ: ШАНС НА ДОЛГУЮ ЖИЗНЬ

Каждый технологический процесс проходит определенные стадии жизненного цикла: разработка, внедрение, рост, достижение максимального уровня развития, спад и постепенный уход с рынка. Анализ жизненных циклов позволяет увидеть, на каких технологических уровнях сегодня выполняется наибольшее число новых разработок интегральных схем (ИС).

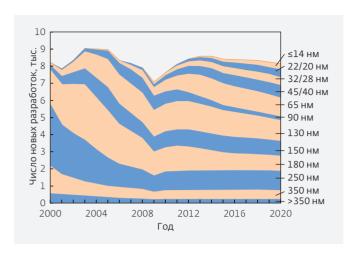

Компания IBS провела исследование, посвященное технологиям, используемым в новых разработках ИС и СнК с 2000 по 2015 год, и сделала прогноз развития полупроводниковых технологий на период до 2020 года. Согласно результатам этого исследования, на сегодняшний день до 90% всех новых разработок выполняется с применением проектных норм 180, 150, 130 и 65 нм (рис.1). Процессы с нормами 45/40, 32 и 28 нм находятся на стадии роста. Новейшие процессы с проектными нормами 22/20 нм и 14 нм

переживают этап начального внедрения в серийное производство.

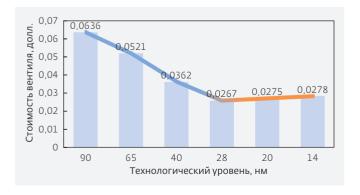

Следует отметить, что при переходе на технологии с проектными нормами менее 20 нм компании-разработчики микросхем столкнулись с новой тенденцией. Если до этого с появлением каждого нового технологического уровня росла производительность ИС и одновременно снижалась удельная стоимость вентиля, то при достижении уровня 20 нм дальнейшее уменьшение себестоимости приостановилось (рис.2). Это связано с существенным ростом сложности производства. В частности, для фотолитографии с разрешением 20 нм и менее необходимо использовать технологию двойного экспонирования, что требует дополнительных фотошаблонов. В результате, у многих компаний возникли трудности с переходом на технологический уровень ниже 20 нм. Соответственно, замедлился рост числа новых разработок на базе 22/20/14-нм технологий (см. рис.1).

**Рис.1.** Распределение новых разработок по используемым технологическим процессам с 2000 по 2020 год

Многие отраслевые аналитики прогнозируют, что в результате снижения темпов внедрения новых процессов, технологии с проектными нормами 130/90 и 65/40-нм будут иметь длительный жизненный цикл. По всей видимости, такая же тенденция позднее будет наблюдаться и в отношении 32/28-нм процессов. Вместе с тем, требования потребителей к изделиям микроэлектроники продолжают расти. Как их обеспечить?

До недавнего времени создание перспективных решений в области микроэлектроники означало проектирование микросхем только под новейшие технологические процессы. Отчасти эта тенденция сохраняется, прежде всего, для наиболее массовых приложений, требующих наивысшей производительности и минимального энергопотребления. Яркий тому пример – комплекты ИС для мобильных устройств или персональных компьютеров.

В то же время, сегодня большие перспективы открываются и при разработках под технологические

**Рис.2.** Стоимость вентиля для разных технологических процессов

процессы, которые уже некоторое время присутствуют на рынке. Технологические процессы с проектными нормами 40/65-нм достигли сегодня высокого уровня качества и выхода годных СБИС, внедрены на множестве полупроводниковых производств, поэтому в рамках данной статьи будем называть такие технологии "традиционными". Их применение для перспективных разработок открывает сегодня массу перспектив.

Ведь кроме технологического процесса, понятие "перспективной разработки" включает в себя и другие составляющие – например, схемотехнические решения, оптимальность топологии, комбинацию используемых IP-блоков и т.п. Так, на основе хорошо отработанной 65-нм технологии можно создать чип, сочетающий в себе самые передовые характеристики и высокий уровень надежности. Причем стоимость его будет значительно ниже, чем у функционально аналогичного изделия, изготовленного по 22-нм процессу.

Спектр приложений, в которых используют ИС на базе традиционных технологий, весьма широк – от автомобильных и медицинских систем до Интернета вещей. При всем различии требований к таким системам, ИС для данных приложений строятся на основе множества общих принципов. Как правило, эти СБИС могут содержать один или несколько процессоров, блоки обработки и анализа сигналов, преобразователи сигналов, аналоговые интерфейсные ІР-блоки, энергонезависимую память и, возможно, МЭМС-датчики. Во многих СнК используются блоки цифровой обработки сигналов, например в приложениях для глобальных навигационных спутниковых систем, обработки видео или повышения качества звука в слуховых аппаратах. Причем микросхемы для управления двигателем, коробкой передач, подвеской, тормозной системой и другими агрегатами автомобиля работают в условиях вибрации и повышенных температур, а напряжение питания может изменяться в пределах от одного до нескольких десятков вольт. Общей задачей при проектировании таких систем является уменьшение занимаемой кристаллом площади и повышение его энергоэффективности, что позволяет увеличить срок службы батарей в портативных устройствах или снизить нагрузку на аккумулятор в автомобильных приложениях.

Достижение высоких характеристик СБИС возможно только при использовании наиболее совершенных методологий и инструментов проектирования. Прогресс в микроэлектронике затрагивает не только технологии производства интегральных схем. Инструменты проектирования совершенствуются

одновременно с ним и зачастую опережая его. Современные САПР позволяют спроектировать изделие, характеристики которого считались недостижимыми еще несколько лет назад, в рамках той же самой технологии. Сегодня на рынке доступны методологии и инструменты проектирования, разработанные для новейших технологических процессов, но позволяющие достичь нового качества результатов проектирования и для традиционных процессов.

По сути, применение современных средств САПР для создания ИС с проектными нормами 40/65-нм и более позволяет достичь ряда характеристик, сопоставимых с характеристиками ИС с меньшими проектными нормами. При этом затраты на производство 65-нм кристаллов будут значительно ниже затрат на запуск производства СБИС по 22-им процессу.

Таким образом, для ИС на основе традиционной технологии ключевым фактором становится уровень проектных решений. Именно он во многом обеспечивает конкурентные преимущества создаваемого изделия. Поэтому разработчики таких ИС не в меньшей, а иногда и в большей степени нуждаются в самых современных средствах САПР, позволяющих максимально использовать все возможности технологического процесса.

## ИНСТРУМЕНТЫ ПРОЕКТИРОВАНИЯ ИС ДЛЯ ПЕРЕДОВЫХ И ТРАДИЦИОННЫХ ТЕХНОЛОГИЙ. ПЛАТФОРМА GALAXY

Прежде всего, решающее значение имеет интеграция инструментов проектирования в связанный единой методологией маршрут, построенный на единой платформе. Возможность проводить детальный анализ и оптимизацию различных параметров проекта в рамках интегрированного процесса проектирования помогает обнаружить потенциальные проблемы на ранних этапах разработки ИС. Например, все задачи проектирования могут быть решены в рамках платформы проектирования Galaxy от компании Synopsys.

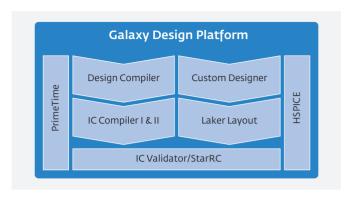

Платформа Calaxy (Calaxy Design Platform) - это комплекс инструментов, интегрированных в единую среду проектирования. Они служат как для создания СБИС на основе библиотечных элементов, так и для разработки полностью заказных схем. Galaxy позволяет проводить разработку аналоговых, цифровых или смешанных схем от уровня регистровых передач (RTL) или уровня принципиальной электрической схемы до уровня топологии GDSII\*. Маршрут

**Рис.3.** Состав платформы разработки Galaxy

проектирования на базе платформы Galaxy включает в себя логический синтез вентильного представления, разработку и верификацию топологии, экстракцию паразитных параметров, а также временной, статический и формальный анализ проектов. Для заказных блоков предусмотрена возможность создания принципиальной электрической схемы и топологии на уровне транзисторов, моделирование схемы и экстракцию паразитных параметров. В состав платформы Galaxy входят такие инструменты, как Design Compiler, IC Compiler, IC Validator, Galaxy Custom Router, Custom Designer, HSPICE, Star-RC, PrimeTime и др. (рис.3).

Design Compiler (DC) - это инструмент синтеза логических схем, оптимизации энергопотребления и занимаемой площади. Он также позволяет интегрировать в схему специальные логические элементы для формирования путей сканирования, необходимых при производственном контроле годности ИС. Для проектирования топологии используется инструмент IC Compiler, обеспечивающий планировку кристалла, размещение элементов и блоков, синтез деревьев тактовых синхросигналов, оптимизацию целого ряда физических параметров, направленную на повышение уровня выхода годных ИС и т. д. За анализ временных характеристик и целостности сигналов отвечает инструмент PrimeTime. В состав платформы Galaxy входит также инструмент Custom Designer, который используется для проектирования заказных решений, в том числе - для проектирования электрических принципиальных схем (Custom Designer Schematic Editor) и топологии (Custom Designer Layout Editor). Он тесно интегрирован с инструментом проектирования топологии ІС Compiler и средствами схемотехнического моделирования HSPICE. Физическую верификацию проекта и экстракцию паразитных RC-параметров можно выполнять с помощью таких инструментов, как ІС Validator и StarRC. Во всех инструментах реализованы

GDSII (Graphic Database System II) – формат файлов баз данных, который используется для обмена данными по топологии интегральных схем между различными САПР или для создания фотошаблонов.

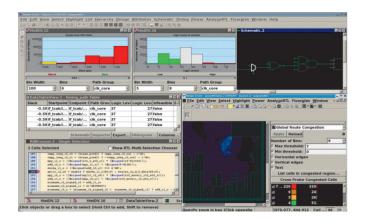

**Рис.4.** Перекрестный анализ различных представлений проекта в DC Graphical

наиболее современные методы и алгоритмы проектирования, которые позволяют создать оптимизированные решения для использования в изделиях на базе традиционных технологий. Рассмотрим лишь некоторые из них.

#### ОПТИМИЗАЦИЯ ПЛОЩАДИ ИС

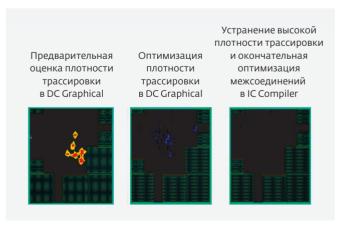

При проектировании ИС, наряду с достижением требуемого быстродействия, большое значение имеет минимизация площади кристалла. Это необходимо для обеспечения высокого уровня выхода годных схем и снижения их себестоимости. Соответственно, инструменты САПР должны обеспечить оптимизацию размещения блоков и эффективное использование трассировочных ресурсов кристалла. Инструмент Design Compiler Graphical (DC Graphical) в процессе логического синтеза позволяет проводить структурную оптимизацию логической схемы для уменьшения плотности трассировки, чтобы более эффективно использовать доступную площадь кристалла. Это важно, поскольку на последующем этапе при размещении и трассировке компонентов, снижение плотности трассировки может быть затруднено или окажется невозможно.

DC Graphical определяет участки схемы с высокой плотностью трассировки, которые могли возникнуть как по причине неоптимальной компоновки кристалла, так и в силу громоздкой структуры логических элементов с множеством межсоединений (причиной последнего, как правило, является структура исходного RTL-описания).

В инструменте DC Graphical имеется возможность перекрестного анализа различных представлений проекта (топологического, списка цепей и RTL). Можно проследить выбранную цепь на электрической схеме, в топологии и в RTL-описании и проанализировать

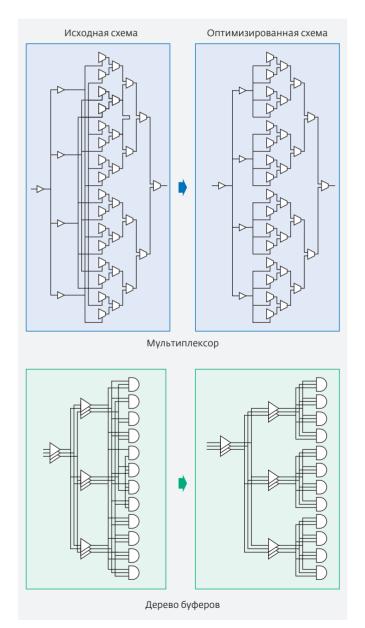

параметры данной цепи (рис.4). Это позволяет, в том числе, идентифицировать ту часть RTL-описания проекта, которая является источником повышенной плотности трассировки, и при необходимости внести в нее изменения. Однако в большинстве случаев делать этого не нужно, так как в DC Graphical реализован алгоритм, который автоматически выбирает оптимальные с точки зрения трассировки конфигурации логических элементов и структур их построения и генерирует список цепей с уменьшенной плотностью трассировки (рис.5).

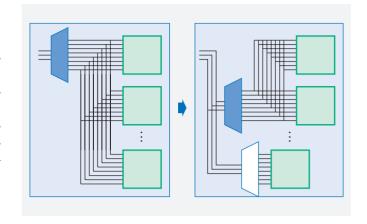

Kpome того, DC Graphical идентифицирует совместно используемые логические схемы и реструктурирует их так, чтобы минимизировать

Рис.5. Оптимизация логических схем в DC Graphical

**Рис.6.** Пример реструктурирования дешифратора адреса

требуемые ресурсы трассировки. Данный алгоритм позволяет решить проблему трассировки сигналов, которые используются по всему блоку или даже кристаллу, например адресных линий дешифратора (рис.6). Алгоритмы, реализованные в DC Graphical, позволяют вносить изменения в список цепей с минимальным влиянием на параметры быстродействия, уменьшая занимаемую схемой площадь и ее энергопотребление. DC Graphical передает все результаты выполненной оптимизации и сформированное размещение элементов в инструмент IC Compiler, который окончательно оптимизирует межсоединения в процессе проектирования топологии кристалла (рис.7).

#### СНИЖЕНИЕ ЭНЕРГОПОТРЕБЛЕНИЯ

Кроме уменьшения площади, важной задачей является снижение энергопотребления кристалла.

**Рис.7.** Совместная работа DC Graphical и IC Compiler позволяет устранить повышенную плотность трассировки

Для этого в платформе Galaxy применяются специальные технологии и алгоритмы, в том числе усовершенствованные алгоритмы управления тактовыми сигналами, оптимальное использование логических элементов с различными пороговыми напряжениями, поддержка отключаемых доменов и доменов с различными напряжениями питания, ряд других методов энергосбережения.

Для снижения динамической мощности на вентильном уровне в процессе логического синтеза могут быть введены специальные элементы управления тактовыми сигналами. Они позволяют исключить работу определенных частей логических схем в холостом режиме (например, когда не нужно менять их логические состояния в каждом рабочем цикле). Кроме того, в некритичных по быстродействию цепях возможна замена более мощных логических элементов на менее мошные.

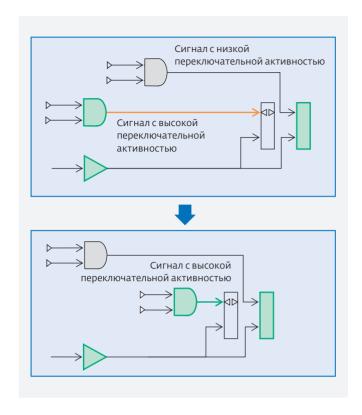

Для снижения динамической мощности используется также механизм минимизации длины так называемых "активных" проводников, по которым передаются сигналы с высокой переключательной активностью (рис.8). Это позволяет не только уменьшить динамическую мощность,

**Рис.8.** Минимизация длины проводников сигналов с высокой переключательной активностью

но и улучшить точность оценки энергопотребления в процессе синтеза.

Для снижения статического энергопотребления (токов утечки) в инструментах DC Graphical и IC Compiler реализован алгоритм, благодаря которому минимизировано использование логических элементов с низким пороговым напряжением. Согласно этому алгоритму при синтезе цепей по умолчанию используются логические элементы с высоким пороговым напряжением, а более быстрые, но обладающие более высокими токами утечки элементы с низким пороговым напряжением, используются только в том случае, когда нет другой возможности обеспечить требования по быстродействию.

Кроме того, при помощи спецификации в формате UPF (IEEE 1801) предусмотрена возможность введения специальных элементов управления электропитанием всего кристалла. Разработчики могут определять на кристалле блоки (домены) с различными величинами напряжения питания и разрешенные состояния в этих доменах (определять правила для выключения, включения, сохранения состояния системы). Все это автоматически учитывается инструментом DC Graphical при логическом синтезе и инструментом IC Compiler при создании планировки и топологии кристалла.

## ДОПОЛНИТЕЛЬНАЯ ТОПОЛОГИЧЕСКАЯ ОПТИМИЗАЦИЯ

Еще одна возможность, которой обладают инструменты платформы Galaxy, - умение учитывать различные значения сопротивлений слоев металлизации при разводке кристаллов. В платформе Galaxy применяется технология Layer Optimization, которая учитывает различное сопротивление верхних и нижних слоев металлизации в процессах оптимизации логической схемы, а также глобальной и детальной трассировки. Этот алгоритм позволяет разводить критичные с точки зрения быстродействия цепи в верхних слоях металлизации с меньшим сопротивлением.

Кроме того, DC Graphical оценивает величину сопротивления переходных отверстий, чтобы повысить точность расчета быстродействия схемы и обеспечить лучшую корреляцию результатов логического синтеза и пост-топологического анализа (с помощью PrimeTime). Последнее достигается за счет использования обоими инструментами одинаковых алгоритмов размещения элементов и глобальной трассировки (Zroute). Предварительное размещение элементов, полученное в результате логического синтеза в DC

Graphical, передается в IC Compiler для дальнейшего проектирования топологии.

Часто даже в полностью цифровых системах возникает необходимость выровнять небольшие группы проводников по длине и сопротивлению, например при разводке сигналов от выходных буферов DDR до макро-ячеек приема/передачи данных и управления протоколом обмена. Иногда нужно вручную создать фрагмент топологии с определенным взаиморасположением нескольких ячеек и проводников и повторить (клонировать) этот фрагмент несколько раз. Для решения подобных задач удобно использовать инструмент Galaxy Custom Router, тесно интегрированный с IC Compiler и имеющий с ним общую базу данных. Galaxy Custom Router позволяет быстро и удобно провести необходимую работу с топологией, а затем сохранить этот проект для дальнейшего проектирования топологии в инструменте IC Compiler.

Мы рассмотрели лишь некоторые возможности инструментов платформы Galaxy, позволяющие добиться высоких результатов и качества проектирования. Рынок микроэлектронных устройств, которые производятся с использованием традиционных технологий, сегодня растет. И современные инструменты САПР позволяют существенно расширить возможности ИС, созданных на основе этих технологий. Это открывает перед разработчиками новые перспективы, поскольку широкий спектр изделий теперь можно спроектировать и изготовить не только на основе самых передовых технологических процессов, но и с использованием гораздо более доступных традиционных технологий, добиваясь нужного результата на этапе проектирования с помощью CAΠP Synopsys.

#### ЛИТЕРАТУРА

- **Bollar Mark.** The new landscape of advanced design. [Электронный ресурс] URL:www.techdesignforums.com.

- **Bollar Mark.** Are advanced designs only possible at emerging process nodes? [Электронный ресурс] URL:www.techdesignforums.com.

- Casale-Rossi Marco. Automotive ICs drive advanced design at established nodes. [Электронный ресурс] URL:www.techdesignforums.com.

- Collins Luke. Synopsys claims latest Design Compiler shrinks existing netlist area, leakage up to 10%. [Электронный ресурс] URL:www.techdesignforums.com.