## **МОДЕЛИРОВАНИЕ**

# НИЗКОВОЛЬТОВЫХ НАНОМЕТРОВЫХ СОВМЕЩЕННЫХ МОП-ПРИБОРОВ

**В.Ракитин,** rakitin@niifp.ru

Для уменьшения относительных размеров полупроводниковых приборов и снижения их напряжения питания используются различные физико-технологические и конструктивносхемотехнические методы [1]. Так, предлагают и уже используют новые типы транзисторов: КНИ, КМОП, многозатворные, нанопроволочные [2], с контактами Шоттки [3], с туннельными истоками [4] и др. Для уменьшения напряжения питания применяют различные режимы работы: подпороговый, с прямым смещением подложки, с адаптивным смещением, с динамическим изменением питания и др. Переход к трехмерным структурам позволяет повысить плотность размещения элементов. Вертикальный нанопроволочный МОП-транзистор с кольцевым затвором занимает минимально возможную сегодня площадь. Совмещенные МОП-транзисторы (СМОП) априори рассчитаны на низкое напряжение питания, что допускает создание максимально компактной конструкции приборов и схем на их основе [5]. Цель данной работы – рассмотрение метода моделирования работы низковольтовых нанометровых совмещенных МОП-приборов.

### ПРИНЦИП ДЕЙСТВИЯ КОНСТРУКЦИИ СМОП

Совмещенные приборы достаточно хорошо известны, и некоторые из них широко распространены. Так четырехслойный р-n-p-n-прибор (тиристор) можно рассматривать как совмещение n-p-n-биполярного транзистора с p-n-p-транзистором. Основная идея СМОП заключается в совмещении активных областей п-и р-канальных МОП-транзисторов. При этом у них могут быть общими затворы и подзатворные

области (каналы). Последнее имеет смысл, если проводимость активной области близка к собственной проводимости кремния (или к фоновой концентрации примеси порядка  $10^{13}$ – $10^{14}$  см<sup>-3</sup>). Отметим, что переход к нелегированным каналам является общей тенденцией в конструкции нанометровых МОП-транзисторов.

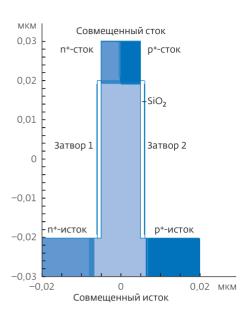

В состав СМОП-транзистора должны входить источник подвижных носителей обоих знаков

**Рис.1.** Разрез двухзатворного нанометрового СМОП с p-n-переходами

(электронов и дырок) – совмещенная область истока – и их приемник – совмещенный сток, который должен беспрепятственно поглощать оба типа носителей (рис.1). В качестве совмещенного истока здесь использован p-n-переход, потенциал  $n^+$ -области которого равен 0, а на  $p^+$ -область подано напряжение питания  $V_s$ . При низких напряжениях ( $V_s \le 0.6$  В) сквозной ток через p-n-переход много меньше рабочих токов в каналах транзисторов.

Фактически в составе СМОП-прибора имеются два МОП-транзистора (виртуальных): п-и р-канальные, а сам СМОП является вентилем (усилителем), у которого затвор – входной электрод, а общий сток – выходной электрод.

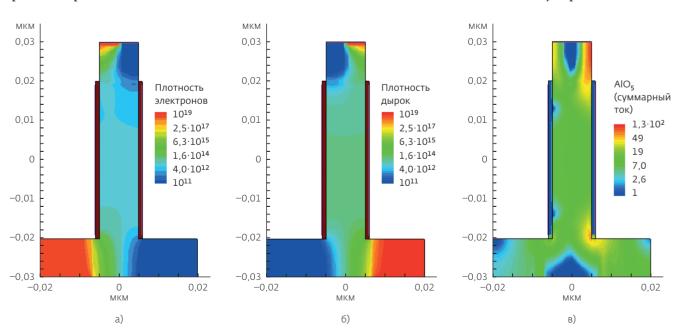

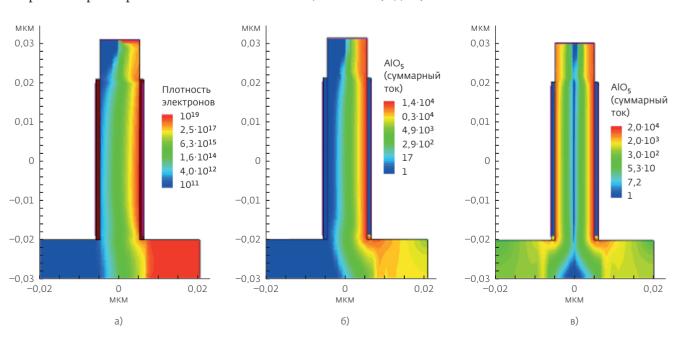

В симметричном приборе (на кремнии с затвором из металла со среднезонной работой выхода 4,65 эВ) при значениях напряжения на затворе V<sub>д</sub> и стоке V<sub>d</sub>, равных половине напряжения питания  $V_{s}$ , концентрации электронов и дырок, а также электронный и дырочный токи примерно одинаковы (рис.2). Если значения напряжения на затворе и напряжения питания близки  $V_{\sigma} = V_{s}$ , в канале симметричного СМОП-транзистора концентрация электронов выше концентрации дырок и в нем преобладает электронный ток (рис.3). Наличие области электронной проводимости между п+-истоком и п+-стоком выравнивает их потенциалы, и на выходе совмещенного транзистора устанавливается низкий (нулевой) потенциал. При нулевом напряжении на затворе в канале преобладают дырки и на выходе транзистора устанавливается высокий потенциал. Таким образом, при подаче на затвор входного сигнала на стоке появляется инвертированный сигнал, т.е. простейший СМОП-прибор работает как инвертирующий усилитель.

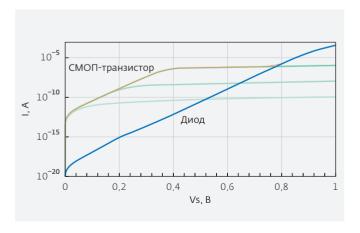

В состав СМОП-транзистора входит прямо смещенный р-п-переход (аналогично КМОП-прибору с прямым смещением подложки), что приводит к постоянному протеканию в канале диодного (сквозного) тока Is. Поэтому принципиальным

**Рис.2.** Плотность электронов (а), дырок (б) и общего тока (в) в СМОП-транзисторе  $(V_q = V_d = V_s/2 = 0.4 \text{ B})$

**Рис.3.** Плотность электронов (a), дырок (б) и тока электронов (в) при  $V_d = V_d = V_s = 0.4$  В

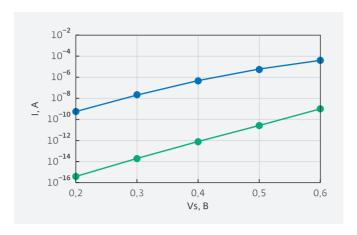

является вопрос о соотношении этого тока с рабочим током СМОП-прибора (рис.4). Как видно из рис.4, значение рабочего тока (определяющего быстродействие транзистора) может на пятьшесть порядков (в рамках используемой модели) превышать сквозной ток диода.

СМОП-транзистор допускает большое разнообразие конструктивных исполнений: планарное или трехмерное, с вертикальным или горизонтальным каналом, с одним или несколькими затворами. СМОП-транзистор с кольцевым затвором, который может быть выполнен на нанопроволоке. В качестве совмещенных истоков/стоков могут использоваться р-п-переходы, контакты

Рис.4. Зависимости тока СМОП-транзистора, ограниченного активной нагрузкой, и паразитного диода от напряжения питания

Рис.5. Входная (а) и выходная (б) характеристики СМОП-транзистора

**Рис.6.** Зависимость рабочего и паразитного тока СМОП-транзистора от  $V_{\rm s}$

Шоттки, туннельные контакты и др. В частности, совмещенный исток может быть областью локальной генерации носителей обоих типов (например, фотогенерации).

СМОП-приборы могут использоваться как в линейных, так и в цифровых устройствах. Сложные логические функции реализуются за счет сложения потенциалов на затворе, токов в объединенных стоках или в многозатворных конфигурациях.

#### МОДЕЛЬ НАНОМЕТРОВОГО СМОП-ТРАНЗИСТОРА

Моделирование СМОП-транзистора с нанометровыми размерами выполнялось с помощью

программы DESSIS пакета ISE TCAD. Результаты моделирования справедливы как для вертикальной конструкция (см. рис.1), так и для горизонтального транзистора. Толщина тела транзистора варьировалась в диапазоне 10-20 нм, длина затворов - 40-100 нм, эффективная толщина диэлектрика (оксида кремния) - 1-2 нм. Ширина тела транзистора составляла 1 мкм. Концентрация фоновой примеси в теле принималась равной  $10^{13}$  см $^{-3}$ . Учитывалась рекомбинация носителей по механизму Шокли-Рида-Хола со временем жизни неосновных носителей заряда 10-100 мкс и со скоростью поверхностной рекомбинации 103-104 см/с. Нижние из указанных значений являются типичными для обычных интегральных приборов и приняты в DESSIS по умолчанию. В качестве стоков/истоков использовались как высоколегированные области, так и контакты Шоттки. В первом случае п+-область легировали мышьяком, p+-область - бором. Концентрация каждого типа примеси составляла  $10^{19}$  см<sup>-3</sup>. Во втором случае контакт Шоттки задавался работой выхода металла. Совмещенный сток формировался непосредственно за счет перекрытия высоколегированных областей или с помощью проводящей связи. Истоки были разнесены на ширину тела транзистора, и совмещенным истоком служила область между ними. В качестве материалов затвора рассматривались металлы как со среднезонной работой выхода, равной 4,65 эВ, так и металлы с работой выхода в диапазоне от 4,1 до 5,2 эВ.

**Рис.7.** Плотность носителей (а) и токов (б) при  $V_q = V_s$  и при  $V_q = V_s/2$  (в)

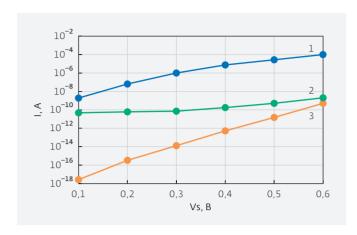

Рис.8. Зависимости рабочего (1), паразитного (2) и сквозного (3) токов н-СМОП-транзистора от напряжения питания

При моделировании простейшего инвертирующего СМОП-усилителя затворы объединялись. В других случаях они управлялись независимо или в соответствии со схемой соединения. Для анализа более сложных элементов вводились дополнительные затворы. Моделировались основные статические характеристики, рассчитывались малосигнальные параметры, анализировались переходные процессы. Рассматриваемые результаты моделирования характерны для СМОП-транзистора, приведенного на рис.1.

#### ХАРАКТЕРИСТИКИ СИММЕТРИЧНОГО СМОП-ТРАНЗИСТОРА

основные Рассмотрим статические теристики примере симметричного СМОП-транзистора с напряжением питания  $V_s = 0,6$  В. Входная характеристика простейшего СМОП-прибора - зависимость тока стока от напряжения на затворе при фиксированном напряжении на стоке (0,3 В) (рис.5а) - отличается от характеристик обычных МОП-транзисторов тем, что ток меняет свое направление в зависимости от напряжения на затворе. При значениях напряжения, больших половины напряжения питания, ток втекает в прибор, при меньших значениях - вытекает из него. Из рис.5а следует, что значение сквозного тока I<sub>s</sub> на несколько порядков меньше рабочего тока. Семейство выходных характеристик СМОПтранзистора (построенное с шагом по напряжению на затворе, равном 0,1 В) (рис.5б) является суперпозицией BAX n- и p-канальных транзисторов. Диапазон значений положительных и отрицательных токов определяется работой выхода металла затвора.

Максимальное значение эффективного напряжения симметричного СМОП-транзистора равно половине напряжения питания, т.е. значительно меньше, чем у транзисторов в составе КМОПструктуры. Токи СМОП-транзистора, по сути, подпороговые и сравнительно невелики, что является платой за низкое напряжение питания. При уменьшении напряжения питания рабочие и сквозные токи экспоненциально уменьшаются (рис.6).

#### МОДЕЛИРОВАНИЕ И ХАРАКТЕРИСТИКИ НЕСИММЕТРИЧНОГО СМОП-ТРАНЗИСТОРА

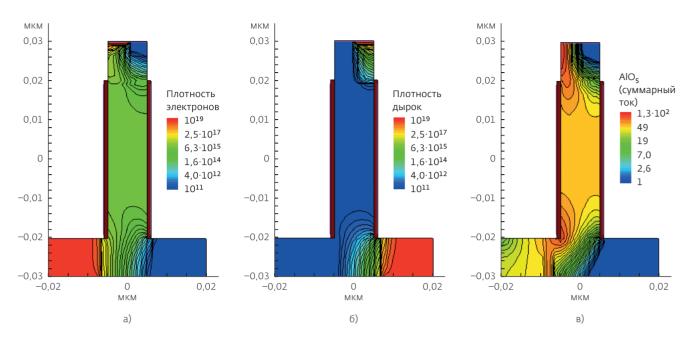

несимметричных Использование СМОПтранзисторов (н-СМОП) позволяет значительно увеличить рабочие токи. В н-СМОП-приборе в качестве затворов использовались металлы с различной работой выхода. Было проведено исследование влияния работы выхода затворов

Рис.9. Выходные (а) и передаточные (б) характеристики н-СМОП-транзистора

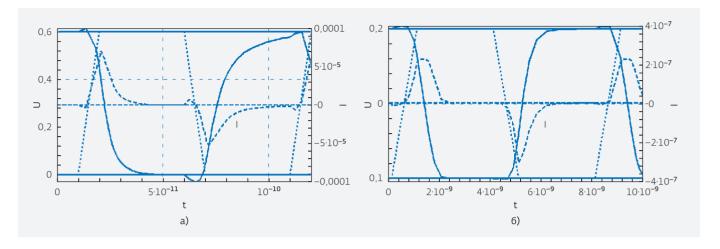

Рис.10. Переходные процессы в СМОП-транзисторе при питании 0,6 В (а) и 0,2 В (б)

двух вариантов н-СМОП-транзисторов с работой выхода материала затворов 1 и 2 – 4,3 эВ и 5,0 эВ соответственно. Было получено, что под затвором 1 в основном присутствуют электроны, а под затвором 2 – дырки (рис.7), при этом концентрация носителей и плотность тока значительно растут.

Рост рабочего тока н-СМОП-транзистора, обусловлен снижением барьера между истоком и каналом, тогда как барьер между п<sup>+</sup>- и р<sup>+</sup>-истоками не изменяется, т.е. значение сквозного тока сохраняется (рис.8). Вместе с тем появляется паразитный ток утечки между стоком и истоком, особенно существенный при низких значениях напряжениях питания.

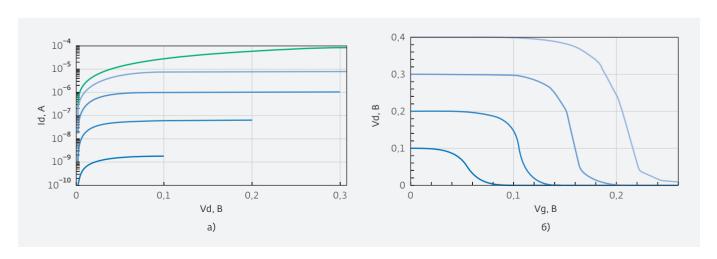

Результаты моделирования выходных и передаточных характеристик н-СМОП-транзисторов при значениях напряжения питания 0,4-0,1 В приведены на рис.9 (изображена только часть шкалы).

Передаточные характеристики позволяют оценить коэффициент усиления СМОП-транзистора по напряжению, равный примерно 10. Он может быть увеличен на порядок при усложнении конструкции за счет добавления второго слоя затворов (каскодное включение).

Результаты моделирования показали возможность применения н-СМОП-транзисторов в аналоговых и цифровых схемах при значительном снижении напряжения питания вплоть до 0,2 В. Значительное ухудшение усилительных свойств н-СМОП-транзистора при напряжении питания меньше 0,1 В связано с существованием больших паразитных токов.

Динамические характеристики н-СМОПтранзистора в режиме большого сигнала моделировались при внешней нагрузке порядка 1 фФ (емкость затвора СМОП-транзистора порядка 0,2 фФ). В таких условиях при напряжении питания 0,6 В СМОП-прибор удовлетворительно передает импульсную последовательность с частотой до 10 ГГц (рис.10а). Задержка переключения транзистора не превышает 20 пс и линейно возрастает при увеличении емкости нагрузки. При напряжении питания 0,2 В рабочая частота снижается до 100 МГц (рис.10б).

00 00 00

Моделирование ряда конструкций СМОПтранзисторов, в том числе с минимальным топологическим размером 10 нм, показало, что они работоспособны при напряжении питания вплоть до 0,1 В, имеют коэффициент усиления по напряжению 10 и выше и могут функционировать на гигагерцовых частотах.

Показано, что параметры СМОП-транзисторов, отвечают основным требованиям цифровых и аналоговых систем – минимизации размеров при низковольтовом питании и достаточно высоком быстродействии.

#### **ЛИТЕРАТУРА**

- 1. **Hanson S. et al.** Ultralow-voltage, minimum-energy CMOS. IBM J. Res.&Dev., 2006, №50, p.469–490.

- Appenzeller J. et al. Toward Nanowire Electronics. IEEE Tran. ED, 2008, №55, p.2827-2845.

- 3. **Larson J. et al.,** Overview and Status of Metal S/D Schottky-Barrier MOSFET Technology. IEEE Tans. ED., 2006, №53, p.048-1058.

- 4. **A. Seabaugh et al.** Low-Voltage Tunnel Transistors for CMOS. Proc. IEEE, 98, 2010, p.2095-2110.

- 5. **Ракитин В.В.** Совмещенные транзисторы. Электронная промышленность, 2004, с.59-63.