# Платформа Synopsys для проектирования цифровых систем - новый уровень технологий проектирования СнК

К. Розе<sup>1</sup>, Д. Радченко<sup>2</sup>

УДК 004.9:621.3.049.774 | ВАК 05.27.00

Платформа проектирования Synopsys Design Platform представляет собой полный набор инструментов для проектирования цифровых, аналоговых и смешанных схем и позволяет инженерам-разработчикам СнК целиком пройти маршрут от спецификации уровня RTL на одном из языков описания аппаратуры до уровня GDSII, а если проект содержит заказную или аналоговые части, то выполнить полный цикл проектирования, начиная от ввода схемы на уровне транзисторов и заканчивая физической верификацией GDSII.

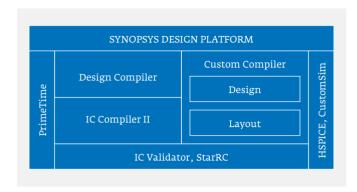

а рис. 1 изображена платформа проектирования Synopsys Design Platform. Ключевыми инструментами платформы, отвечающими за цифровое проектирование, являются Design Compiler, IC Compiler II и PrimeTime. За проектирование на уровне транзисторов в платформе отвечает инструмент Custom Compiler. Он предоставляет богатый набор функций для автоматизации проектирования как в схемном, так и в топологическом представлениях и интерфейс с инструментами моделирования (HSPICE, CustomSim). Также важной частью платформы являются инструменты StarRC и IC Validator, первый из которых предназначен для экстракции паразитных RC-параметров цепей как на уровне вентилей, так и на уровне транзисторов, а второй – для проведения физической верификации. Эти инструменты используются как в цифровом, так и в полнозаказном/аналоговом маршруте проектирования.

В рамках данной статьи мы уделим основное внимание только основным инструментам цифрового маршрута проектирования, экстракции и физической верификации. Подробно об инструментах полнозаказного / аналогового проектирования мы расскажем в одной из следующих статей.

Современные инструменты автоматизированного проектирования СНК невозможно рассматривать поодиночке. Их нужно оценивать во взаимосвязи с другими инструментами, решающими последующие задачи в маршруте проектирования, а также с учетом взаимодействия с вендорами ІР-блоков и библиотек. Необходимость такого подхода вызвана сложностью современных проектов, связанной с жесткими требованиями по быстродействию, потребляемой мощности и занимаемой площади,

и особенностями существующих полупроводниковых технологий, в базисе которых проводится проектирование CHK. Synopsys активно сотрудничает с ведущими полупроводниковыми фабриками для того, чтобы максимально учитывать в своих инструментах особенности технологических процессов и их влияние на качество результатов.

Инструменты, входящие в платформу проектирования Synopsys Design Platform, используют большое количество общих алгоритмов и функций. Те из них, которые применяются в начале маршрута проектирования, часто решают задачи, ранее относившиеся к более поздним этапам. Например, сегодня Design Compiler осуществляет не только синтез, но и размещение логических элементов, проводит оптимизацию быстродействия с учетом сопротивления проводников в различных металлических слоях. При этом IC Compiler II начинает свою работу сразу с оптимизации полученных от Design Compiler результатов размещения с учетом дерева синхросигналов. IC Compiler II интегрирован с инструментами StarRC и IC Validator, что позволяет избежать дополнительных итераций и увеличения сроков завершения проектирования и / или минимизировать время, необходимое на внесение исправлений на поздних этапах проектирования (ЕСО).

Взаимная связь между инструментами платформы, обусловленная общими базовыми алгоритмами, прозрачной инфраструктурой и совместимыми интерфейсами, позволяет пользователю получить сквозной сходящийся маршрут проектирования для достижения желаемых показателей быстродействия, мощности и площади. Эти инструменты имеют общие настройки, позволяющие эффективно и в минимальные сроки реализовывать проекты с различными характеристиками, используя специализированные функции и одинаковые заданные значения переменных, что дает дополнительный толчок для

roze@synopsys.com.

dmitry.radchenko@synopsys.com.

**Рис. 1.** Платформа проектирования Synopsys Design Platform

быстрого построения маршрута проектирования, максимально эффективного для решения конкретной задачи проекта.

Все инструменты Synopsys Digital Platform в настоящее время используют многоядерную параллельную обработку данных, которая позволяет в разы сократить время получения результатов. Также во всех инструментах платформы начали применяться методы самообучения машин (machine learning), благодаря которым возможно создание и использование более быстрых и надежных моделей для анализа трассируемости, быстродействия, мощности и других важных характеристик проекта. Результатом являются ускоренное прохождение по маршруту и общее сокращение сроков проектирования.

Таким образом, Synopsys Design Platform представляет собой полную систему проектирования СнК, позволяющую получать максимально высокое качество результатов за наименьшее время и с минимальными затратами.

Для того чтобы облегчить разработчикам внедрение новых технологий при реализации их проектов, Synopsys предлагает к использованию набор так называемых рекомендуемых методологий проектирования (RM – Recommended Methodologies) (см. табл.). Эти методологии включают в себя базовые наборы скриптов и документации по подготовке библиотек, иерархическому и одноуровневому маршрутам проектирования.

В этой статье мы рассмотрим основные инструменты платформы проектирования от Synopsys, отвечающие за ключевые этапы проектирования.

#### **DESIGN COMPILER**

Первым инструментом в нашем обзоре будет Design Compiler – инструмент логического синтеза, предназначенный для трансляции и оптимизации схемы из описания на уровне RTL в список цепей (netlist) на уровне стандартных ячеек.

В современном проекте СНК в каждом логическом блоке (модуле), не считая макроблоков и памяти, может содержаться более миллиона логических вентилей. Объем синтеза и оптимизации, который должен выполнить Design Compiler, очень большой. Необходимо собрать логическую схему и оптимизировать ее по ряду параметров, таких как быстродействие, динамическое

## Номенклатура рекомендуемых методологий проектирования RM

| Тип проекта                                      | Рекомен-<br>дуемая<br>методоло-<br>гия | Скрипты,<br>связанные<br>с инстру-<br>ментом<br>и версией | Скрипты,<br>связанные<br>с фабрикой | Связанные с технологической библиотекой, с арифметикой с плавающей запятой и ограничениями | Комментарии                                                                                                                                     |

|--------------------------------------------------|----------------------------------------|-----------------------------------------------------------|-------------------------------------|--------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|

| Общего при-<br>менения                           | RM                                     | +                                                         | +                                   |                                                                                            | Идеально для качества результатов<br>«из коробки» для общего примене-<br>ния и для оценочного прогона                                           |

| Специаль-<br>ные                                 | RM+                                    | +                                                         | +                                   |                                                                                            | Идеально для качества результатов «из коробки» для конкретных задач (высокопроизводительных, с ограничениями на площадь, с высокой связностью)  |

| Arm CPUs<br>Cortex-A53,<br>A55, A72, A73,<br>A75 | Arm<br>QuickStart                      | +                                                         | +                                   | +                                                                                          | Разработано совместно с Arm, зави-<br>сит от технологии, перекрывает весь<br>маршрут (имплементацию, пере-<br>дачу в изготовление, верификацию) |

и статическое энергопотребление, площадь и т.д. Дополнительная сложность возникает из-за необходимости учета планировки кристалла, а также того факта, что оптимизация должна проводиться во всех режимах работы блока одновременно.

Поэтому разработчики инструмента уделяют повышенное внимание оптимизации применяемых алгоритмов и использования вычислительных ресурсов. Вместе это позволяет повышать производительность Design Compiler с каждым новым релизом инструмента. Так, за последний год, по результатам анализа регрессионного набора тестов, в среднем производительность Design Compiler выросла на 15%. Кроме того, постоянный анализ алгоритмов и их оптимизация позволяют повышать качество получаемых результатов. Дополнительно стоит отметить развитие оптимизации с использованием распараллеливания вычислений на нескольких ядрах.

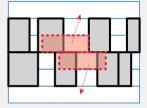

Во многих современных проектах при разработке топологии инженеры сталкиваются с проблемами трассируемости цепей. Часто данные проблемы возникают из-за высокой локальной связности логических элементов в критических цепях. В Design Compiler присутствует алгоритм оптимизации, который минимизирует количество необходимых проводников и их локальных пересечений с учетом планировки и размещения, решая таким образом вышеобозначенные проблемы. Этот алгоритм также работает с тестовой логикой и scan-цепями. Он минимизирует влияние scan-цепей на трассировку, осуществляя в том числе перекоммутацию scan-цепей путем размещения триггеров.

Еще одной проблемой, приводящей к ухудшению трассируемости, является планировка кристалла, в которой есть так называемые узкие каналы, образующиеся между массивами макроблоков. Для нахождения и оптимизации таких ситуаций Design Compiler Graphical использует такой же алгоритм глобальной трассировки, как в инструменте IC Compiler II. Алгоритм буферизации применяет трассировщик Zroute для точного определения объема трассировочных ресурсов и свободной площади для наиболее оптимальной расстановки необходимого числа и номенклатуры буферов. Эта технология позволяет существенно повысить качество результатов в проектах со сложной планировкой.

Параметры слоев трассировки также влияют на качество результатов. Величины сопротивлений проводников в различных слоях при применении передовых технологий варьируются значительно сильнее, чем в случае традиционных технологий. На этапе оптимизации Design Compiler использует индивидуальные значения сопротивлений для каждого слоя трассировки вместо усредненной величины по всем металлическим слоям. Это позволяет существенно увеличить точность оценки значения RC-параметров для каждой конкретной цепи, что к тому

же повышает точность корреляции результатов между инструментами логического синтеза и создания топологии. Более того, Design Compiler позволяет учитывать не только сопротивления самих проводников, но и переходов между металлическими слоями (via), вклад которых в общую величину сопротивления всей цепи от ячейки к ячейке в передовых технологиях также очень существенен. Это лишь небольшая часть алгоритмов, имеющихся в распоряжении Design Compiler, в которых используются технологии. традиционно применяемые в инструментах топологического проектирования (рис. 2).

Не менее важной задачей, чем выполнение логического синтеза, является передача всей созданной при синтезе информации на следующий этап проектирования – топологический. С помощью одной пользовательской команды Design Compiler создает файлы со всеми необходимыми данными для передачи в IC Compiler II. Эти файлы загружаются в IC Compiler II также путем выполнения всего одной команды. Таким образом IC Compiler II получает в свое распоряжение хорошо подготовленный к оптимизации список цепей с данными размещения и руководство для синтеза деревьев синхросигналов и детальной трассировки.

#### IC COMPILER II

Инструмент IC Compiler II предназначен для топологического проектирования. Он разработан на основе новой архитектуры и структуры данных, ориентированных на достижение наибольшей скорости работы и высокого качества результатов. Особое внимание уделено поддержке больших сложных СнК с многоуровневой физической иерархией, содержащих более 100 млн ячеек. В рамках экосистемы платформы проектирования Synopsys было проведено объединение многих алгоритмов и функций, общих для Design Compiler и IC Compiler II, в частности функций оптимизации размещения, RC-экстракции, управления энергопотреблением (UPF) и т.п., а также обеспечен обмен данными внутри платформы для получения сквозного маршрута проектирования.

Работа по оптимизации алгоритмов и сокращению времени проектирования по маршруту продолжается при подготовке каждого нового релиза инструмента. Модель данных IC Compiler II обеспечивает поддержку распределенных процессорных архитектур, используемых в настоящее время на большинстве этапов маршрута физического проектирования. Также непрерывно внедряются новые алгоритмические решения, позволяющие сократить время работы инструмента на каждом из этапов. По результатам регрессионного тестирования IC Compiler II за последний год время прохождения по полному маршруту физического проектирования было сокращено на 25%.

Особое внимание в последних релизах инструмента IC Compiler II уделяется получению высокого качества

#### Устранение превышенной Оптимизация на основе Поддержка малых плотности трассировки глобальной трассировки геометрических элементов • Буферизация на основе Zroute • Выведение цепей, критичных • Специализированная оптимизация к временным характеристикам, лля минимизации количества лля устранения превышения пересечений и длин проводников плотности трассировки на верхние слои • Встроенная оптимизация • Моделирование сопротивления для тестирования Узкий канал переходов с превышенной • Учет плотности плотностью • Поддержка правил, отличных от правил по умолчанию • Точная оценка RC-параметров Непомещаюшиеся проводники велутся в обхол • Список цепей для более простой • Повышение корреляции трассировки по всему маршруту • Отличное качество результатов • Возможность уменьшения • Улучшение сложных планировок • Высокая корреляция площади планировки

Рис. 2. Некоторые ключевые технологии Design Compiler

результатов «из коробки» (Out-of-the-box), то есть с использованием настроек инструмента по умолчанию. Что же представляет собой этот подход и чем он привлекателен для инженера разработчика? Основой данного подхода являются мощные и стабильные алгоритмы, толерантные к небольшим изменениям входных данных, позволяющие получать наиболее оптимальные результаты для проектов на ранней стадии разработки и с неполными входными данными. Важным фактором является также простой в использовании интерфейс, позволяющий пользователю выбрать желаемый маршрут проектирования и пройти по нему. Единые рекомендуемые маршруты RM, упомянутые ранее, являются ключом, помогающим инженерам быстро и эффективно адаптировать инструмент к особенностям конкретного проекта. Дополнительной помощью инженерам-разработчикам в последних релизах IC Compiler II являются так называемые «мегаустановки», то есть переменные, осуществляющие настройку алгоритмов инструмента на работу с особенностями передовых технологических процессов (таких как 7 и 5 нм).

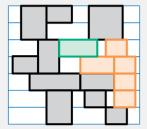

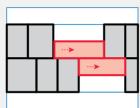

Стоит упомянуть, что в последних релизах особое внимание разработчиков IC Compiler II было уделено улучшению алгоритмов как глобального размещения ячеек, так и их легализации (рис. 3), что обеспечивает улучшение

трассируемости путем детализированного учета параметров трассировки в нижних слоях, сокращение длины проводников за счет оптимальной ориентации ячеек, оптимизацию доступа к пинам, выравнивание пинов и границячеек при детальном размещении и легализации и т. д.

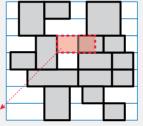

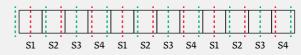

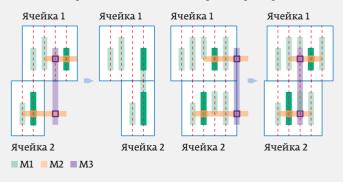

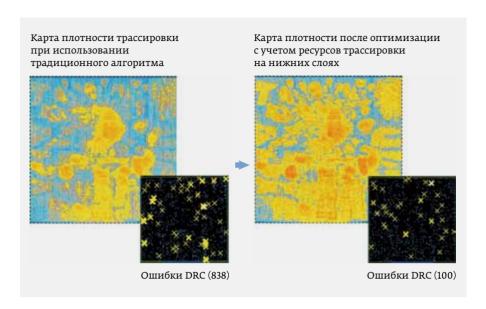

Пример, показанный на рис. 4, демонстрирует, как алгоритм размещения с учетом трассируемости в нижних слоях трассировки помогает существенно уменьшить количество нарушений правил проектирования (DRC). Традиционный алгоритм размещения рассчитывает трассируемость путем вычитания сумм свободных и занятых вертикальных и горизонтальных ресурсов трассировки по всем слоям. Такой расчет не учитывает возможные проблемы трассируемости в нижних слоях. Точная оценка трассируемости в нижних слоях позволяет алгоритму размещения IC Compiler II принимать более правильные решения о том, какие ячейки нуждаются в перемещении и на какое расстояние. Результатом является улучшенное размещение ячеек, в конечном итоге сводящее к минимуму нарушения правил проектирования.

Еще одним интересным примером новейших технологий в IC Compiler II является технология оценки RC-параметров на основе трассировки (RDE – Route-Driven Estimation), в которой применяются современные

алгоритмы с самообучением для создания моделей RC-параметров, базирующихся на глобальной трассировке, созданной с помощью алгоритма Zroute. Данные, полученные при глобальной трассировке, используются для проведения оценки RC-параметров с помощью статистической модели данных. При этом, глобальная трассировка выполняется один раз, но на основании полученных результатов создаются многомерные таблицы, в которых сохраняются данные трассируемости по слоям для всех цепей, индексированные с использованием их характеристик, таких как длина провода, слой в котором

расположены пины, количество нагрузок и т.д. Последующая оценка RC-параметров производится на основании этих таблиц с применением интерполяции и экстраполяции и затем используется при оптимизации.

Говоря о модели данных применяемой в IC Compiler II, необходимо отметить новые возможности, которые она предоставляет в области планировки кристалла. Новая модель данных поддерживает многоуровневую вложенную физическую иерархию проекта. Это дает возможность разработчику планировать кристалл, оптимизируя все уровни иерархии в контексте единого проекта,

#### Поточный легализатор

- Результат работы легализатора по умолчанию

- Одно значительное перемещение

- Результат работы поточного легализатора

- Поток небольших перемещений

#### Оптимизация ориентации в легализаторе

Для уменьшения количества перемещений ячеек

Ячейки переворачиваются с целью удовлетворения правилам проектирования при легализации и во избежание перемещения ячеек

- Сторона размещения и вертикальный трек для технологий TSMC Nx и N7+

- На каждом четвертом минимальном поле размещения ячейки конфигурация проводников повторяется – необходим маршрут с оптимизацией ориентации и с учетом вариантов

#### Дефрагментация рядов размещения

Предварительное уплотнение ячеек

- Ячейки с кратной высотой образуют фрагментированные ряды размещения

- Широкие ячейки с единичной высотой оказывается сложно легализовать излишние значительные перемещения приводят к потери площади

- Уплотнение ячеек с кратными высотами в группы сводит к минимуму фрагментацию с небольшими пропусками, непригодными для использования при размещении

- Существенно снижается количество значительных перемещений – выполняются небольшие перемещения в пределах ряда

# Вертикальное расположение пинов TSMC N7

- Выравнивание по вертикали расположенных поблизости соединенных пинов для обеспечения возможности прямого соединения на слое М1 путем удлинения пинов

- Устранение ситуаций, когда два соединенных пина в соседних рядах смещены друг относительно друга на один трек

- Эмпирические данные показывают, что случай смещения на один трек более сложен с точки зрения трассировки

Рис. 3. Оптимизация размещения и легализация ячеек в IC Compiler II

Рис. 4. Оптимизация трассируемости в IC Compiler II с учетом нижних слоев трассировки

включая определение границ блоков, размещение макроячеек и пинов, определение временных ограничений (рис. 5).

Важно отметить, что ICC II Design Planning позволяет оптимально работать с проектами с многократно используемыми блоками (МІВ). Так, специальный алгоритм определяет наилучшее расположение портов, подходящее для всех экземпляров MIB. Важным аспектом работы с МІВ является то, что разработчику нет необходимости определять эталонную копию блока, чтобы повысить

качество результатов: все операции внутри маршрута планировки в инструменте IC Compiler II разработаны таким образом, чтобы находить оптимальные решения для всех экземпляров МІВ.

Подробнее о возможностях планировки СнК с использованием инструмента IC Compiler II мы уже рассказывали ранее.

# **PRIMETIME**

Ключевым инструментом для контроля параметров проекта перед передачей в изготовление (sign-off) и доработки проекта в связи с выявлением ошибок на поздних стадиях проектирования (ЕСО) является инструмент PrimeTime.

Инструмент PrimeTime является отраслевым стандартом и рекомендуется к использованию всеми полупроводниковыми производствами в отрасли.

Так как PrimeTime используется для проверки законченных проектов, то одним из его ключевых качеств является возможность обрабатывать большие объемы информации. Представьте себе проект, в котором количество стандартных и макроячеек может доходить до миллиарда, а суммарный размер файлов паразитных RC-параметров составляет несколько терабайт. Весь этот огромный объем данных может быть успешно обработан инструментом PrimeTime за приемлемое время на имеющихся в распоряжении разработчиков

серверах, несмотря на то, что внедрение исчерпывающего статического временного анализа на основе логических путей (PBA – Path Based Analysis), являющегося более точным по сравнению с анализом на основе графов (GBA – Graph Based Analysis), привело к серьезному увеличению объема обрабатываемых данных и повлекло увеличение времени обработки. Разработчики инструмента PrimeTime постоянно работают над повышением производительности и точности работы инструмента. Важной особенностью PrimeTime

Рис. 5. Иерархическая планировка проекта в IC Compiler II

См.: ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2017. № 4. С. 72.

Рис. 6. Зависимость скорости работы PrimeTime от размера проекта и используемых аппаратных ресурсов

является возможность использования не только многоядерных процессоров, но и распределенных вычислений (рис. 6).

Разумеется, инженеры компании Synopsys работают не только над повышением производительности PrimeTime, но и над тем, чтобы максимально полно использовать результаты его работы для доработок проекта в связи

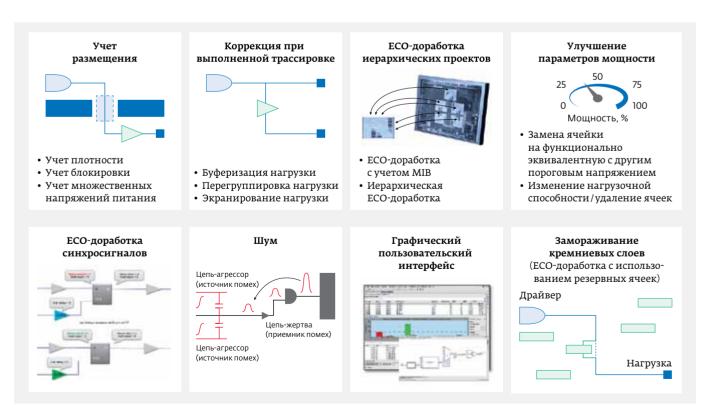

с выявлением нарушений типа setup, hold power, area и transition на поздних стадиях проектирования (ECO). В этой связи PrimeTime становится ключевым инструментом не только для контроля, но и для максимально быстрого завершения проектирования (рис. 7). Каким образом? По результатам анализа проекта с учетом его топологических параметров PrimeTime генерирует необходимые

**Рис. 7.** ECO-функции инструмента PrimeTime

скрипты и параметры для исправления найденных нарушений с помощью инструмента IC Compiler II.

PrimeTime может считывать полную информацию о размещении в формате DEF и с момента ее загрузки располагает данными о том, в каких местах возможно добавление новых логических ячеек, а в каких нет. При этом во внимание принимаются не только свободные и занятые места, но и области высокой локальной плотности элементов, добавление дополнительных ячеек в которые может негативно сказаться на качестве результатов проектирования и параметрах СнК. Так как кроме данных размещения файл DEF содержит полную информацию о трассировке, PrimeTime может проводить высокоэффективную ЕСО-доработку посредством вставки буферов и элементов задержки на уже проложенные проводники.

PrimeTime поддерживает иерархические проекты, включая, что очень важно, проекты с многократно используемыми блоками (MIB). Для таких блоков PrimeTime ЕСО генерирует один общий файл изменений и доработок, являющийся наиболее оптимальным для любого экземпляра MIB.

Также PrimeTime помогает проводить финальную оптимизацию потребляемой мощности: как статической (токи утечек), так и динамической.

Недавно в PrimeTime была добавлена возможность внесения изменений в деревья синхросигналов с использованием параллельной оптимизации путей и данных (CCD – Concurrent Clock and Data).

И наконец, в PrimeTime есть возможность устранения шумовых помех с помощью дополнительной буферизации или замены буферов на более мощные для цепи – приемника или обратной операции для цепи – источника помех (только в том случае, если это не ухудшает характеристики цепи).

Прежде чем закончить наш рассказ о возможностях PrimeTime, необходимо упомянуть о том, что все вышеперечисленные ЕСО-функции инструмента доступны разработчикам также и при запуске PrimeTime в среде IC Compiler II для проведения ECO-доработки с качеством PrimeTime, не покидая инструмента проектирования топологии

#### **STARRC**

Как мы уже упоминали выше, для проведения полноценного статического sign-off-анализа в PrimeTime необходимо наличие файлов паразитных RC-параметров всех цепей проекта для всех условий эксплуатации и всех режимов работы проекта (таких как температура и напряжение). Наличие этих данных требуется для так называемого

Рис. 8. Возможности совместной работы IC Validator и IC Compiler II

многовариантного многокритериального (multi-corner multi-mode – MCMM) анализа.

Для проведения МСММ-экстракции служит инструмент StarRC, который выполняет экстракцию и аннотирование значений RC-параметров для каждой цепи в топологии проекта. StarRC поддерживает проекты как иерархического, так и плоского (не иерархического) типа. Естественно, что одними из ключевых свойств такого инструмента являются точность и скорость работы. Без необходимой точности невозможно выполнить этап sign-off, обеспечив соответствие проекта требуемым параметрам, а при недостаточной скорости работы будет сложно уложиться в заданные сроки проектирования.

На финальных этапах оптимизации размещения и трассировки разработчики могут выполнять экстракцию RC-параметров с помощью StarRC в составе инструмента IC Compiler II для получения максимально точных их значений и повышения качества конечного результата, а также улучшения корреляции результатов со статическим анализом в PrimeTime.

## **IC VALIDATOR**

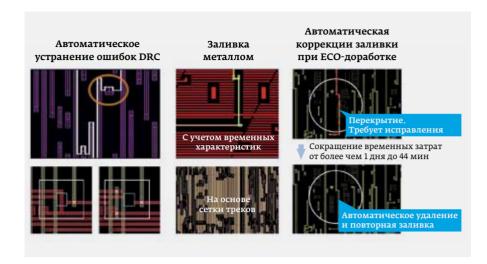

Для проведения физической верификации проекта на соответствие правилам проектирования (DRC) и проверки на соответствие топологии схемы исходному списку цепей (LVS), а также для заливки металлом свободного пространства (Metal Fill) используется инструмент IC Validator. Он является сертифицированным инструментом DRC- и LVS-проверки на большинстве полупроводниковых фабрик в мире, в числе которых как крупнейшие лидеры области из Тайваня и Кореи, так и относительно небольшие и ориентированные на автомобильную промышленность европейские полупроводниковые фабрики.

В соответствии с идеологией платформы проектирования, проверки IC Validator можно использовать и как инструмент физической верификации для финальной физической верификации проекта перед передачей на производство, и в составе IC Compiler II. Это позволяет начать DRC-проверку, как только будет завершена детальная трассировка цепей, и автоматически исправить найденные ошибки DRC с помощью обратной связи от IC Validator к IC Compiler II, тем самым уменьшив количество или полностью исключив дополнительные итерации DRC-проверок и устранения ошибок. Часто это позволяет отказаться от трудоемкой и подверженной ошибкам операции ручного исправления найденных ошибок в топологии схемы.

Следующей ключевой особенностью IC Validator является возможность проводить заливку металлом с учетом влияния добавленного металла на быстродействие критических цепей проекта. Для таких цепей заливка будет произведена по модифицированному алгоритму под управлением инженера – разработчика топологии проекта.

И последняя особенность IC Validator, которую мы упомянем в данной статье, – возможность автоматически изменять заливку металлом в тех областях топологии, где произошли изменения на поздних стадиях проектирования, например, после проведения ECO-доработки. IC Validator автоматически, без участия инженера, находит в топологии такие области и приводит заливку металлом в соответствие изменившейся топологии путем локального удаления металла и повторного выполнения заливки (рис. 8).

В данной статье мы постарались кратко описать основные инструменты и особенности цифровой части платформы проектирования Synopsys Design Platform. Более подробно об этих и других инструментах Synopsys мы расскажем в следующих публикациях.