## Инструмент физической верификации нового поколения IC Validator NXT

K. Pose<sup>1</sup>, Д. Радченко<sup>2</sup>

УДК 004.9:621.3.049.774 | ВАК 05.13.12

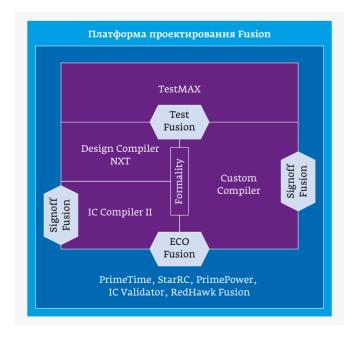

Данной статьей мы продолжаем серию публикаций, рассказывающих о платформе проектирования Synopsys Fusion Design Platform, представляющей собой законченную высокоинтегрированную среду для разработки цифровых, аналоговых и смешанных интегральных схем.

прошлой публикации мы сделали краткий обзор основных инструментов, входящих в эту платформу: Design Compiler – для синтеза логических схем, IC Compiler II – для проектирования топологии интегральных схем, PrimeTime – для временного статического анализа, StarRC – для экстракции паразитных RC-параметров, и IC Validator – для проведения физической верификации проекта на соответствие правилам проектирования (DRC/LVS). Кроме того, в платформу Fusion также входят инструменты аналогового и смешанного проектирования. Это инструмент Custom Compiler, предназначенный для проектирования схемотехники и топологии, а также различные инструменты моделирования на транзисторном уровне, такие как HSPICE, CustomSim и FineSim. Практически все инструменты входящие в платформу Fusion являются взаимно интегрированными. Haпример, Design Compiler использует алгоритмы размещения и оценки RC-параметров от IC Compiler II, и наоборот, IC Compiler II использует алгоритмы Design Compiler для логической оптимизации списка цепей (netlist), StarRC – для точной экстракции RC-параметров (на этапе sign-off), а IC Validator – для проверки правил проектирования «на лету». Помимо взаимной интеграции, инструменты активно используют алгоритмы машинного обучения (ML) для достижения максимально возможного качества результатов при минимальном времени работы инструмента.

В целом можно говорить о том, что платформа Fusion состоит из нескольких частей. В левой области рис. 1 представлена часть, предназначенная для цифрового проектирования, в правой — для аналогового и смешанного. Нижняя область рисунка является общей для обоих частей платформы и предназначена для финальных проверок перед передачей проектов на производство (sign-off). Инструменты, представленные в этой области, могут работать как с проектами на уровне стандартных ячеек,

так и с проектами на уровне транзисторов. К ним относятся, в частности, инструменты StarRC и IC Validator NXT. О последнем из них мы сегодня и поговорим. С момента прошлой публикации к названию инструмента добавилось NXT (сокращение от слова next, то есть это инструмент следующего, нового поколения), и теперь его полное название — IC Validator NXT. Кроме IC Validator, такую добавочную часть в названии получил и Design Compiler. Что же поменялось в инструменте и почему мы считаем IC Validator NXT инструментом нового поколения?

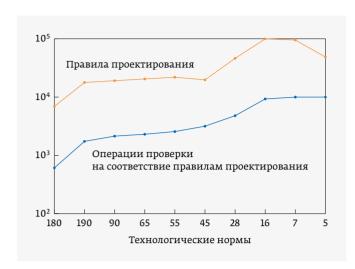

По мере того, как возрастает сложность ИС, что сопряжено с существенным увеличением их физического размера при одновременном уменьшении проектных норм, растет и сложность физической верификации (рис. 2). Действительно, возникает необходимость в проверке на соответствие правилам проектирования все большего количества полигонов; при этом экспоненциально растет

**Рис. 1.** Платформа проектирования Fusion Design Platform и ее инструменты

roze@synopsys.com.

dmitry.radchenko@synopsys.com.

<sup>&</sup>lt;sup>®</sup> См.: ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2018. № 2. С. 96–104.

Рис. 2. Зависимость количества правил проектирования топологии от технологических норм

и количество самих этих правил. Например, на технологических нормах 16 нм проект с площадью кристалла около 80 мм<sup>2</sup> содержит около 2 млрд транзисторов, а для технологии 5 нм при той же площади число транзисторов увеличится до 12 млрд. Традиционные подходы к физической верификации перестают работать эффективно, потому что:

- время работы инструментов для DRC-, ERC-, LVS-проверок становится слишком большим;

- инструменты требуют всё больших аппаратных pecypcob;

- результаты работы сложно интерпретировать, что влечет за собой трудности в исправлении ошибок.

Вывод однозначный: нужны как новые алгоритмы, так и новые методологии для проведения физической верификации.

Именно поэтому и появился инструмент IC Validator NXT – инструмент для DRC-, LVS-, ERC-проверок и проверок заливки (FILL) нового поколения.

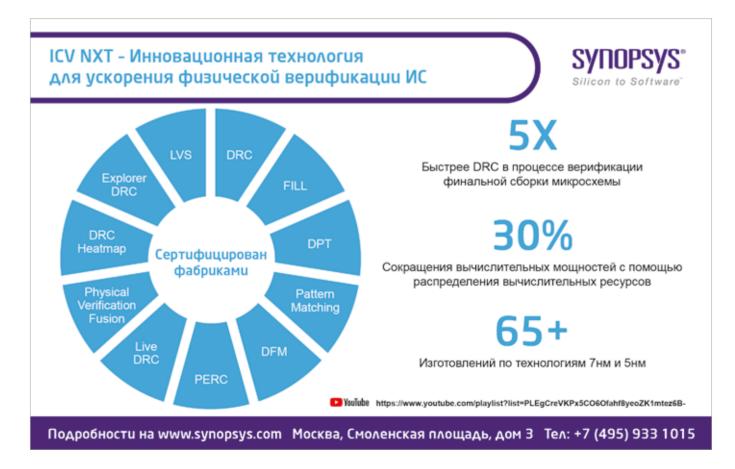

Традиционно процесс физической верификации ассоциируется с проверкой правил топологии проекта (DRC). Но важно помнить, что требования современной физической верификации гораздо шире проверки базовых правил топологии, поэтому IC Validator NXT, являясь инструментом физической верификации нового поколения, поддерживает все

особенности современных технологических процессов ведущих фабрик и предоставляет все необходимые возможности для физической верификации проектов глубокого субмикронного уровня с учетом DPT, Pattern Matching, DFM, а также проверок LVS и PERC (рис. 3).

Компания Synopsys тесно работает со всеми ведущими фабриками, такими как TSMC, Samsung, GlobalFoundries и др., и IC Validator поддерживает сертифицированные наборы правил топологического проектирования от этих фабрик.

Кроме самого инструмента, изменения претерпела и методология. IC Validator NXT, являясь частью платформы Fusion, позволяет сократить общее время, затрачиваемое на физическую верификацию проекта, путем пошаговой верификации проекта во время прохождения по маршруту создания топологии, работая в составе инструментов IC Compiler II или Custom Compiler, а также путем использования функции Live DRC для локализованной верификации во время инкрементальных ЕСО-изменений на финальных стадиях проекта.

Новые подходы к методологии физической верификации для увеличения производительности включают следующее:

- выполнение проверки на соответствие правилам проектирования (DRC) в процессе разработки топологии блоков (или ІР-блоков) с целью нахождения и исправления максимального количества ошибок на каждом уровне физической иерархии;

- проведение DRC-проверки на уровне подсистем и на верхнем уровне только после того, как будут

Рис. 3. Основные компоненты инструмента IC Validator NXT и взаимодействие с производством

- устранены все ошибки на уровне блоков или большинство из них;

- использование для запуска проверок максимально возможного количества динамически распределяемых аппаратных ресурсов.

#### IC VALIDATOR FUSION TECHNOLOGY™

Рассмотрим подробнее, каким образом можно интегрировать инструмент физической верификации IC Validator NXT в процесс разработки топологии блоков, то есть использовать его задолго до того, как будет готова сборка всего проекта в целом (рис. 4).

Можно запускать IC Validator NXT для DRC-проверки с использованием топологического представления макроблоков и стандартных ячеек вместо их абстрактов, как только будет завершена детальная трассировка цепей, и производить устранение найденных DRC-ошибок автоматически с помощью обратной связи от IC Validator NXT к IC Compiler II. Данная технология называется ADR (Automatic DRC Repair – технология автоматического устранения DRC-ошибок). Она сводит к минимуму количество дополнительных итерации типа «проверка DRC – инкрементальное устранение ошибок». Часто это позволяет отказаться от ручного исправления найденных ошибок в топологии схемы – трудоемкой и чреватой внесением новых ошибок операции. Таким

образом, не покидая среду проектирования топологии IC Compiler II, разработчик получает топологию высокого качества, которая не содержит DRC-ошибок на уровне блоков и не потребует устранения ошибок на поздних стадиях. В дальнейшем такой подход позволяет сократить время DRC-проверок на верхнем уровне. Это подобно тому, как если бы можно было мыть посуду в процессе приготовления пищи.

Но это еще не всё. IC Validator NXT может помочь и на более ранних стадиях проектирования, например при планировании кристалла и создании сетки электропитания или синхросигналов. Исправление DRC-ошибок, связанных с сеткой питания, на поздних этапах проектирования – достаточно сложный и времязатратный процесс. Функция IC Validator Live DRC (рис. 4) может выполнять онлайн-проверку созданных металлических структур, помогая разработчику создать корректный дизайн сетки питания до этапов размещения и трассировки.

В том случае, если блок большой, для начальных проверок целесообразно использовать IC Validator Explorer, о чем будет рассказано ниже.

Кроме DRC-проверки, сочетание инструментов IC Validator NXT и IC Compiler II предоставляет возможность проводить dummy-заливку и заливку металлом с учетом влияния добавленного металла на быстродействие критических цепей проекта. Для таких цепей

**Рис. 4.** Интеграция инструмента IC Validator NXT в процесс разработки топологии проекта (интеграция с IC Compiler II)

заливка будет произведена по модифицированному алгоритму под управлением инженера – разработчика топологии проекта.

Последняя особенность интеграции IC Validator NXT в процесс проектирования топологии, которую упомянем в данной статье, - возможность автоматически изменять заливку металлом в тех областях топологии, где произошли какие-либо изменения на поздних стадиях проектирования, например после проведения ECO. IC Validator NXT автоматически, без участия инженера, находит измененные области в топологии блока и приводит заливку металлом (путем локального снятия заливки и добавления новой заливки) в соответствие с произошедшими изменениями топологии.

То же касается и так называемого верхнего уровня. Полноценные DRC-проверки и заливку также можно выполнять не выходя из инструмента IC Compiler II.

Тот же маршрут с интеграцией IC Validator NXT используется и для проектирования полнозаказных схем. Инженерам-топологам более не нужно сначала завершать проектирование топологии, а уже затем запускать DRC-проверки и исправлять ошибки. Благодаря технологии Live DRC инструмента IC Validator NXT DRC-проверки выполняются непосредственно в процессе создания элементов топологии либо на любом ее фрагменте

в любой момент времени. Так как объем проверок в каждый момент невелик, можно считать, что они происходят в реальном масштабе времени. В случае обнаружения ошибок инженер может исправить их немедленно, поскольку все проверки выполняются без выхода из среды проектирования.

Кроме сред проектирования Custom Compiler и IC Compiler II инструмент IC Validator NXT поддерживает интеграцию с инструментом Cadence Virtuoso.

#### ПОВЫШЕНИЕ ПРОИЗВОДИТЕЛЬНОСТИ РАБОТЫ

Физическая верификация является одной из завершающих и наиболее критичной фазой маршрута физического проектирования. От нее часто зависит, состоится ли передача проекта на изготовление в соответствии с запланированным графиком.

Компания Synopsys активно работает над предоставлением дополнительных возможностей для увеличения производительности инженеров, разрабатывающих топологии проектов, и сокращения общего времени, затрачиваемого на проведение физической верификации.

ICV Explorer, Heat Map и Elastic CPU management – лишь часть из многих составляющих инструмента IC Validator NXT, созданных специально для повышения производительности процесса физической верификации.

#### **Explorer DRC**

Инновационная технология для верификации проектов на ранних стадиях

Заявка на патент на ICV Explorer подана в 2016 году!

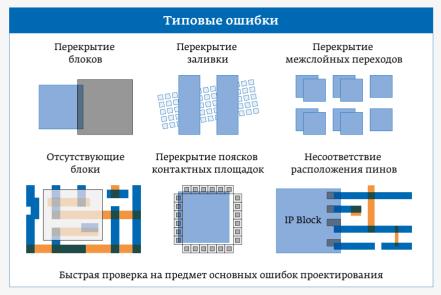

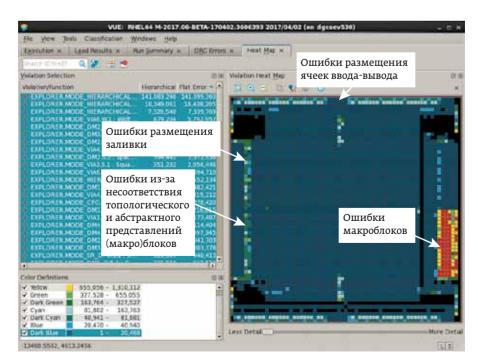

#### Рис. 5. Основные проверки Explorer DRC

Благодаря ICV Explorer (рис. 5) время физической верификации проектов, находящихся в процессе проектирования, может быть сокращено примерно в пять раз. ICV Explorer позволяет быстро находить грубые ошибки в проектах большого или очень большого размера,

которые часто присутствуют в них на ранних стадиях, такие как ошибки размещения макроблоков памяти, вводавывода, сетки электропитания и т. д. Избегая на этой стадии время- и ресурсозатратных проверок более сложных правил, ICV Explorer помогает выявлять подобные ошибки

за минимальное время и с использованием только минимально необходимых вычислительных ресурсов. Использование ICV Explorer не требует изменения набора правил проектирования (DRC Runset). Инструмент IC Validator NXT, работая в режиме Explorer, автоматически определит оптимальную последовательность и составляющие проверок.

ICV DRC Heat Map (рис. 6) позволяет существенно сократить время, затрачиваемое на анализ и исправление ошибок, найденных в процессе физической верификации. Эта функция предоставляет информацию об ошибках в проекте в форме двумерной гистограммы, отражающей количество ошибок в разных областях проекта с помощью температурной цветовой гаммы, где красный цвет соответствует наибольшему количеству DRC-ошибок. Каждый тип

Рис. 6. Использование DRC Heat Map

ошибок может отображаться на отдельной гистограмме и путем наложения на топологическое представление проекта обеспечить обратную связь для разработчиков, помогая им в эффективном анализе причин возникновения и устранении DRC-ошибок.

По мере приближения проекта к передаче на изготовление на фабрику у инженеров-разработчиков часто возникает необходимость запрашивать большое количество серверов для того, чтобы получить достаточные вычислительные ресурсы для финальных DRC- и LVS-проверок. Всё возрастающие требования к количеству вычислительных ресурсов, требующихся для своевременного завершения физической верификации больших проектов, становятся проблемными для многих компаний.

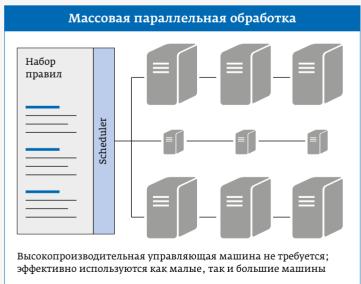

IC Validator NXT обладает способностью эффективно распределять задачи физической верификации на тысячи микропроцессоров и ядер. Этой задачей в данном инструменте управляет планировщик (scheduler) нового поколения (рис. 7), выполняющий оценку, мониторинг и балансировку использования физической памяти, требующейся для проведения операций из списка проверок, и распределяющий задачи по различным процессорам оптимальным образом с точки зрения минимизации общего вычислительного времени, машинной памяти и использования жесткого диска. Этот планировщик обладает способностью динамического перераспределения задач с одних аппаратных ресурсов на другие, в том случае если на каком-либо сервере произошел

аппаратный сбой или обнаружены сбои обмена данными по сети, с локальным диском или нехватка памяти. Поэтому IC Validator NXT способен автоматически восстанавливать и продолжать работу до окончания выполнения физической верификации без потери результатов ее расчетов.

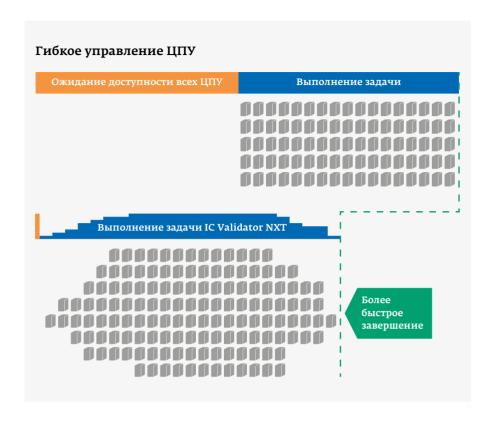

IC Validator NXT также позволяет эффективно и гибко использовать имеющиеся компьютерные ресурсы с помощью новейших технологий Elastic CPU management (рис. 8). Этот подход снимает традиционные ограничения на начало и завершение работы инструмента: технологии динамического (в процессе работы) добавления и удаления хостов, поддерживаемые инструментом IC Validator, позволяют инструменту начать работать, не дожидаясь, когда все требуемые хосты освободятся, используя при этом имеющиеся в наличии, и постепенно добавлять новые хосты, когда они становятся свободными, а также, если необходимо, освобождать хосты, не останавливая при этом работу самого инструмента.

В настоящее время многие компании, занимающиеся разработкой СБИС и СНК, начинают рассматривать применение предоставляемых провайдерами облачных ресурсов для ускоренного прохождения процесса физической верификации с использованием большого количества аппаратных ресурсов. Инструмент IC Validator NXT полностью поддерживает работу в облаках и уже используется разработчиками для физической верификации реальных проектов.

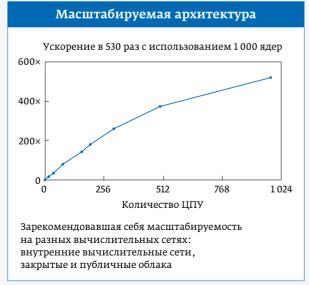

#### Наиболее быстрая передача на изготовление всего кристалла

Масштабируемость более чем до 1 000 ЦПУ позволяет выполнять этап Sign-off для всего кристалла за считанные часы

Puc. 7. Использование распределенных вычислительных ресурсов инструментом IC Validator NXT

Рис. 8. Пояснение принципа гибкого использования аппаратных ресурсов (технологий Elastic CPU management). В верхней части схематично показаны этапы выполнения при классической организации, в нижней - работа IC Validator NXT

#### **ЗАКЛЮЧЕНИЕ**

В данной статье мы постарались рассказать об основных новых возможностях инструмента IC Validator NXT – новом поколении инструмента для физической верификации DRC/LVS и заливки. Главное отличие нового поколения инструмента от предыдущего – резкое повышение эффективности использования в маршруте проектирования. Это достигается благодаря выполнению ранних запусков верификации непосредственно в процессе разработки топологии, широким возможностям по интеграции в более ранние этапы проектирования и гибкому использованию вычислительных инфраструктур – как локальных, то есть имеющихся у компаний, так и облачных.

В следующих статьях мы продолжим знакомить читателей с новым поколением инструментов проектирования. Каких именно? Возможно, о каком инструменте или инструментах компании Synopsys вам было бы интересно прочитать, нам подскажете вы. наши читатели?

М.: ТЕХНОСФЕРА, 2014. – 296 с.,

ISBN 978-5-94836-365-3

#### КНИГИ ИЗЛАТЕЛЬСТВА «TEXHOCФЕРА»

Цена 760 руб.

### ВАЛИДАЦИЯ НА СИСТЕМНОМ УРОВНЕ. ВЫСОКОУРОВНЕВОЕ МОДЕЛИРОВАНИЕ И УПРАВЛЕНИЕ ТЕСТИРОВАНИЕМ

М. Чэнь, К. Цинь, Х.-М. Ку, П. Мишра При поддержке ЗАО «СКАН»

Перевод с англ. под ред. А. Н. Ланцева

В этой книге описываются методы высокоуровневого моделирования и валидации комплексных систем аппаратных средств и программного обеспечения, включая архитектуры с многоядерными процессорами. Читатели узнают, как избежать затрат времени и ошибок при всесторонней системной валидации, в том числе при моделировании систем и их отказов, а также об автоматической генерации специализированных тестов и эффективных методиках валидации с использованием подобных тестов и подтверждения работоспособности систем. Методологии, описанные в этой книге, помогут разработчикам улучшить качество валидации благодаря выполнению тестов на ранних стадиях проектирования при одновременном снижении стоимости этих процессов и усилий, направленных на валидацию систем в целом.

Эта книга предназначена для студентов старших курсов, аспирантов, исследователей, разработчиков инструментов САПР, проектировщиков и менеджеров, заинтересованных в развитии эффективных инструментов и методов проектирования и валидации на системном уровне, генерации направленных тестов и функциональной валидации гетерогенных конструкций СНК.

#### КАК ЗАКАЗАТЬ НАШИ КНИГИ?

№ 125319, Москва, а/я 91; **\** +7 495 234-0110; **\** +7 495 956-3346; **knigi@technosphera.ru**, **sales@technosphera.ru**

### РОССИЙСКАЯ НЕДЕЛЯ ВЫСОКИХ ТЕХНОЛОГИЙ

12-я международная выставка

# НАВИТЕХ

www.navitech-expo.ru

21-24 апреля 2020

Организатор форума:

Оператор форума:

Стратегические партнеры форума:

Организатор выставки: