## Современные тенденции развития ПЛИС: от системной интеграции к искусственному интеллекту

А. Строгонов, д. т. н. $^{1}$ , П. Городков $^{2}$

УДК 621.3.049.774 | ВАК 05.27.01

Программируемые логические интегральные схемы на каждом этапе своего развития решали различные задачи. В период становления ПЛИС применялись преимущественно в качестве программируемых интерфейсов, а сегодня они выполняют сложнейшие задачи в области искусственного интеллекта, Интернета вещей, телевидения высокого разрешения, телекоммуникаций, беспроводных сетей 5С и др. В наиболее совершенных ПЛИС реализованы передовые схемотехнические решения, в частности многоядерные процессоры, высокоскоростные память, трансиверы и интерфейсы. Для их производства применяются новейшие конструкторско-технологические приемы, в том числе многоуровневые и 3D-структуры, технологические процессы с топологическими нормами 7 нм и менее. В статье представлен обзор современных ПЛИС от ведущих мировых производителей, приводится их классификация по методам программирования, рассматриваются архитектурные особенности.

настоящее время на рынке ПЛИС представлена продукция следующих компаний: Xilinx, Achronix Semiconductor, Atmel, Intel (Altera), Lattice Semiconductor, Microsemi (Actel), Cobham Semiconductor Solutions (Aeroflex), QuickLogic и др. Компании Tabula, Achronix, SiliconBlue, Tier Logic, M2000 начинали свою деятельность в области ПЛИС как стартапы. В 2015 году Tabula прекратила свою работу. Большая часть рынка поделена примерно поровну между Intel и Xilinx. Многие крупные полупроводниковые компании, такие как Harris, Cypress, AMD, Philips/Signetics, Texas Instruments, National Semiconductor, Excel, Samsung, Plessey, AMI, SGS, Toshiba, Dynachip, IBM, Motorola, Lucent и др., ранее разрабатывавшие ПЛИС, уже ушли с этого рынка. Однако появились новые игроки, например китайская компания Gowin Semiconductor.

Современные ПЛИС принято классифицировать по технологии программирования: флеш, СОЗУ и «антифьюз». Наиболее перспективными считаются программируемые элементы, выполненные по технологии электрически стираемых перепрограммируемых ПЗУ (EEPROM)

и флеш-технологии (МОП-транзисторы с плавающим затвором), обеспечивающие энергонезависимое сохранение конфигурации и многократное перепрограммирование, а также элементы на базе СОЗУ.

## ПЛИС НА ОСНОВЕ ФЛЕШ-ТЕХНОЛОГИИ

Флеш-ячейка представляет собой МОП-транзистор с плавающим затвором, который можно отключить, подав заряд на плавающий затвор. Основные производители ПЛИС на основе флеш-технологии: Intel (Altera), Xilinx, Lattice, Microsemi (Actel).

Компания Microsemi выпускает ряд серий ПЛИС на базе флеш-технологии, в частности ProASIC3, IGLOO, FUSION и ПЛИС СнК SmartFusion, SmartFusion2, PolarFire. Например, серия SmartFusion2 представляет собой ПЛИС СнК, которую производят на тайваньской фабрике UMC по 65-нм технологии. В устройстве используются массивы программируемой логики (до 150 тыс. логических элементов), блоки статического ОЗУ (Micro SRAM и Large SRAM), встроенное микропроцессорное ядро ARM Cortex-M3 с рабочей частотой 166 МГц (со встроенными блоками eNVM (энергонезависимая память), eSRAM и периферией CAN, TSE, USB), математические блоки (MACC, умножители 18×18), высокоскоростные последовательные приемопередатчики (со скоростью 5 Гбит/с) и контроллеры DDR-памяти.

Еще одна серия ПЛИС СнК от Microsemi – PolarFire – coдержит многоядерный процессорный кластер на основе

Воронежский государственный технический университет, профессор кафедры полупроводниковой электроники и наноэлектроники, тел. +7 4732 43-76-95, andreistrogonov@mail.ru.

Воронежский государственный технический университет, аспирант кафедры полупроводниковой электроники и наноэлектроники, тел. +7 4732 43-76-95, gorodkoff@gmail.com.

64-разрядного RISC-V с поддержкой Linux, поэтому устройство подходит для решения задач реального времени. PolarFire позволяет реализовывать сложные вычислительные алгоритмы для захвата и отображения информации, а также для построения интеллектуальных видеосистем с высоким разрешением 4К/2К благодаря большому объему памяти и ЦОС-ресурсам. Преимущества процессора RISC-V — открытая архитектура команд, не требуется оплаты лицензии и роялти, как у ARM, что привлекательно для стартап-компаний.

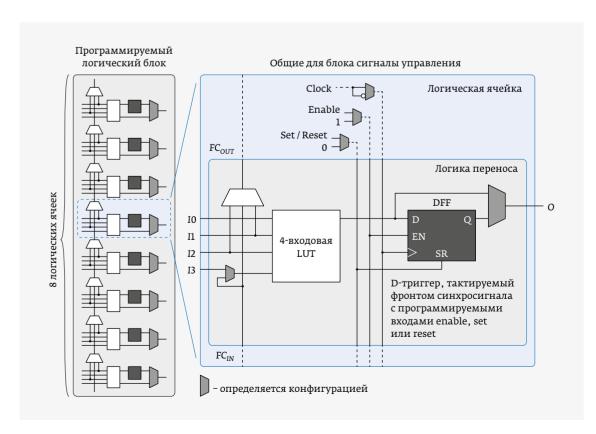

## ПЛИС НА ОСНОВЕ СОЗУ

ПЛИС, основанные на LUT и технологии статического ОЗУ, предлагают Intel (Altera), Xilinx, Achronix, Lattice (SiliconBlue), Tabula и QuickLogic.

Ячейка СОЗУ представляет собой электронный ключ и триггер оперативной памяти, в который при включении питания должна быть записана информация о конфигурации. Технология СОЗУ позволяет уменьшить энергопотребление и запрограммировать ПЛИС за десятки миллисекунд, обеспечив исходную загрузку конфигурирующей памяти и при необходимости реконфигурирование на лету для адаптации структуры реализуемого устройства. В настоящее время выпускаются также радиационно-стойкие КМОП ПЛИС на основе СОЗУ. К таким устройствам относятся, например, ПЛИС серии Virtex-5QV от Xilinx с поддержкой программного инструмента Xilinx ТМR, который автоматически генерирует структуры с тройным резервированием, обеспечивающие защиту от SEU и SET.

Примерами высокотехнологичных ПЛИС на основе СОЗУ служат серии Cyclon и Stratix последних поколений от Intel (Altera). Семейства Cyclon V и Stratix V (28-нм технологический процесс TSMC) содержат аппаратные IP-блоки (контроллеры интерфейсов и внешней памяти), ЦОС-блоки переменной точности, блоки памяти М10К и MLAB, поддерживают режим частичной реконфигурации. ПЛИС серии Stratix V снабжены встроенным интерфейсом (Hard IP) для управления внешней памятью. В ПЛИС Altera серии Cyclon V могут быть интегрированы два процессорных ядра ARM Cortex-A9.

Каждый ЦОС-блок ПЛИС серии Stratix V позволяет реализовать два умножителя двух 18-разрядных слов или один умножитель двух 32-разрядных слов. ЦОС-блоки содержат также 64-разрядную каскадирующую шину и 64-разрядный аккумулятор.

ЦОС-блоки с переменной точностью в Stratix V позволяют применять эти ПЛИС в сверточных нейронных сетях (Convolutional Neural Network – CNN) для анализа изображений и видео в технологиях глубокого машинного обучения. На основе ПЛИС Stratix V компания Microsoft разработала ускоритель CNN, который продемонстрировал преимущества перед графическими процессорами.

Усовершенствованные ПЛИС Intel (Altera) серий Cyclone 10 и Stratix 10 содержат адаптивные логические модули (АЛМ) новой структуры; 2-ядерные (ARM Cortex-A9) или 4-ядерные (64-разрядный ARM Cortex-A53) процессорные системы; больше вариантов встроенной памяти (конфигурируемый блок M20K); аппаратные ЦОС-блоки с переменной точностью для вычислений с плавающей точкой; аппаратные IP-блоки (высокоскоростные трансиверы, контроллеры внешней памяти, контроллеры PCI Express Gen1-3); аналоговые блоки (Cyclone 10).

В ПЛИС Stratix 10, выпускаемых по 14-нм технологическому процессу Intel FinFET, появилась новая трассировочная структура HyperFlex (регистры повсюду) во внутрикластерной коммутации. Кластер содержит девять АЛМ и локальные трассировочные ресурсы. В соединительных блоках на мультиплексорных структурах используются дополнительные регистры (гиперрегистры, или hyper-register), применение которых в локальных и глобальных трассировочных ресурсах позволяет выравнивать задержки распространения сигналов за счет их перераспределения (retiming) и конвейеризации.

НурегFlex позволила сохранить однокристальную реализацию логических ресурсов ПЛИС по мере их роста. В отличие от такого подхода, в ПЛИС от Xilinx (причем как в более ранней серии Virtex-7, так и в более поздней — Virtex UltraScale+, выпускаемой по 16-нм процессу FinFET+) предусмотрена сегментация кристалла ПЛИС на секции для последующей реализации проекта на отдельных кристаллах и их соединения с помощью кремниевой коммутационной платы.

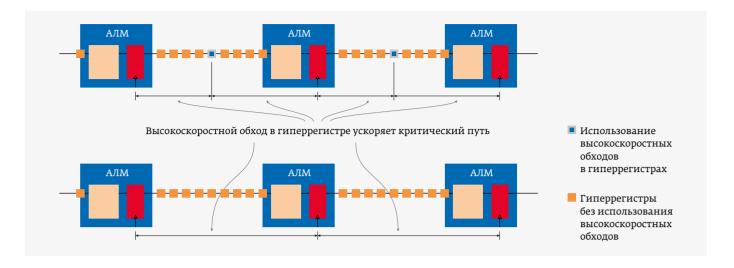

В ПЛИС СНК Intel серии Agilex, изготовляемых по 10-нм технологическому процессу Advanced FinFET, производительность улучшена благодаря введению высокоскоростных обходных путей в трассировочных ресурсах с использованием гиперрегистров второго поколения. Если проект не оптимизирован для архитектуры HyperFlex, то критический путь разделяется на части по регистрам АЛМ (рис. 1). По оценкам специалистов, технология соединительных ресурсов HyperFlex второго поколения повышает производительность ПЛИС на 40% по сравнению с ПЛИС серии Stratix 10.

В предыдущих сериях ПЛИС Intel ЦОС-блоки переменной точности аппаратно поддерживали формат FP32 (плавающая запятая с одинарной точностью, стандарт IEEE754). Усовершенствованные ЦОС-блоки переменной точности в процессорах ПЛИС Agilex поддерживают форматы FP16 (половинная точность с плавающей запятой) и bfloat16 (ВF16, формат библиотеки машинного обучения Tensorflow). ПЛИС серии Agilex обеспечивают производительность до 40 TFLOPS для форматов FP16 и BF16 или до 20 TFLOPS — для FP32.

ПЛИС серии Agilex поддерживают новую технологию подключения кеша и памяти Compute Express

**Рис. 1.** Высокоскоростные обходные пути в гиперрегистрах позволяют снизить задержки в трассировочных ресурсах: вверху – разделение критического пути на части с помощью гиперрегистров второго поколения; внизу – гиперрегистры первого поколения

Link (CXL), интерфейс стандарта PCIe Gen 5, трансиверы со скоростью передачи до 112 Гбит/с, память DDR4, DDR5, HBM (High Bandwidth Memory) и 4-ядерный процессор ARM Cortex-A53. С помощью шины Compute Express Link ПЛИС серии Agilex I могут быть подключены к процессорам Intel Xeon.

Среди ПЛИС СНК на основе СОЗУ компании Xilinx наиболее совершенные — устройства серии Versal, которые изготавливаются по 7-нм технологическому процессу FinFET. Эти ПЛИС ориентированы на высокопроизводительные приложения, такие как обработка алгоритмов искусственного интеллекта, например алгоритмов машинного обучения в беспроводных сетях 5G. Кроме того, ПЛИС можно использовать в центрах обработки данных и в облачных вычислениях.

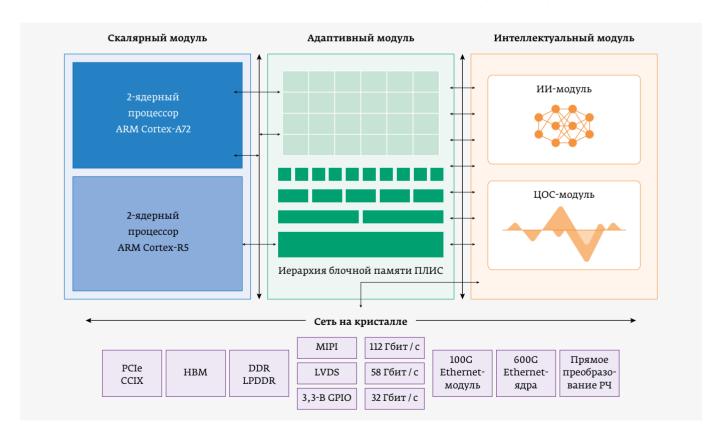

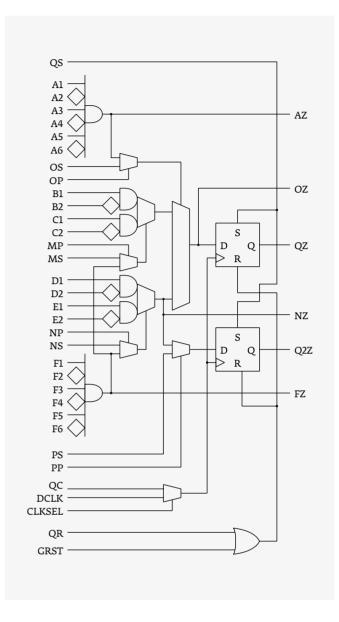

ПЛИС Versal реализованы на адаптивной платформе для ускорения вычислений любых приложений (Adaptive Computer Accelerator Platform – ACAP). В состав платформы входят четыре базовых компонента: скалярный модуль, адаптивный модуль, интеллектуальный модуль (векторные ускорители), а также высокоскоростная сеть на кристалле (Network-on-Chip – NoC) для связи модулей внутри системы (рис. 2). Программируются модули с применением языков С, С++ и Python.

Модули для скалярных вычислений (Scalar Engines) реализуются на основе 2-ядерных процессоров ARM — Cortex-A72 (процессорный модуль общего применения, или APU) и Cortex-R5 (процессорный модуль реального времени, или RPU). Cortex-R5, который используется также в ПЛИС CHK Zynq UltraScale+ от Xilinx, обеспечивает гораздо более высокую производительность, чем процессоры серии Cortex-M. Процессор Cortex-A72 с предельной тактовой частотой 2,5 ГГц, представляющий серию ARMv8,

обеспечивает поддержку 32/64-разрядных вычислений. В ПЛИС серии Versal используется ядро Cortex-A72, рассчитанное на 7-нм технологический процесс FinFET, что позволяет в два раза улучшить показатель DMIP/Вт по сравнению с 16-нм технологией. Процессоры Cortex-R5 из серии ПЛИС UltraScale+, адаптированные под 7-нм технологический процесс, отличаются дополнительным уровнем безопасности для ответственных приложений.

Модули для адаптации аппаратных компонентов (Adaptable Engines) реализуются на логических ресурсах ПЛИС с улучшенной способностью к частичной реконфигурации. Модуль управляет иерархией встроенной памяти массива ПЛИС под конкретную вычислительную задачу (Custom Memory Hierarchy). В серии Versal число триггеров в КЛБ достигает 1969152, а число LUT — 984576. Максимальное количество логических ячеек для VM2902 — самой крупной ПЛИС в серии Versal — составляет 2153760.

Интеллектуальные модули (Intelligent Engines), предназначенные для выполнения задач искусственного интеллекта и ЦОС-приложений, поддерживают операции умножения с плавающей запятой, обеспечивая минимальные задержки. Интеллектуальные модули отличаются высокой пропускной способностью, а также минимальными задержкам при выполнении операций и оптимальным уровнем энергопотребления. Они основаны на VLIW-архитектуре, которая обеспечивает параллельное выполнение нескольких операций в одной инструкции, поддерживают обработку множественных данных по принципу SIMD, что позволяет повысить производительность в 5–10 раз в задачах цифровой обработки сигналов и машинного обучения. Интеллектуальные модули называют также VLIW/SIMD-ускорителями или AI-ускорителями. Для ПЛИС Versal число ЦОС-модулей может

составлять 3080 для VM2902, а количество интеллектуальных модулей – 400.

Базовые компоненты ПЛИС связаны специальной сетью на кристалле (Network-on-Chip — NoC), пропускная способность которой достигает 1 Тбит/с. Сеть обеспечивает быстрый обмен данными между различными частями ПЛИС, возможность непосредственного программирования и не требует этапа размещения и трассировки при реализации проекта в базис ПЛИС. Она доступна в процессе конфигурирования, поскольку является аппаратной шиной. Энергопотребление такой сети ниже в восемь раз по сравнению с ее реализацией на логических ресурсах программируемой логики.

ПЛИС Versal также содержат интерфейсы хост-систем для взаимодействия с другими процессорными системами, в том числе PCle Gen4x16; интегрированный модуль AXI-DMA; CCIX для ускорения решения серверных задач; контроллеры внешней памяти DDR4-3200, LPDDR-4266, HBM; аппаратные ядра для реализации высокоскоростных протоколов передачи данных: 100 Гбит/с Multirate Ethernet, 600 Гбит/с Ethernet и Interlaken, 600 Гбит/с Cryptographic Engines (AES/IPSEC/MACSEC); широкополосные трансиверы, оптимизированные по энергопотреблению, на 32/58 Гбит/с PAM4 и 112 Гбит/с PAM4;

радиочастотные блоки — multi-GSPS RF-ADC/DAC нового поколения, DDC/DUC, SD-FEC для 5G и DOCSIS; программируемые блоки ввода-вывода для поддержки различных интерфейсов — MIPI D-PHY с поддержкой скорости более 3 Гбит/с на сенсор, LVDS и порты ввода-вывода общего назначения (GPIO).

Другие компании также предлагают ПЛИС, оптимизированные для решения задач искусственного интеллекта. Например, Achronix разработала ПЛИС серии Speedster7t, которая выпускается на TSMC по 7-нм технологическому процессу. Ранее компания представила серию Speedster22i на базе 22-нм технологического процесса Intel.

ПЛИС Speedster7t оптимизированы для использования в ускорителях машинного обучения и сетевых решениях с высокой пропускной способностью. В Speedster7t включен массив программируемых вычислительных элементов, которые легко конфигурируются для работы с целыми числами и числами с плавающей запятой. Среди особенностей серии ПЛИС Speedster7t — наличие гибкого массива процессоров машинного обучения (MLP) и высокоскоростной сети на кристалле (NOC).

Каждая ПЛИС cepuu Speedster7t отличается большим набором программируемых математических

**Рис. 2.** Блок-схема архитектуры Versal от Xilinx: скалярные процессоры ARM Cortex-A72 и Cortex-R5 (скалярный модуль), массив ПЛИС с блочной памятью (адаптивный модуль), ЦОС-блоки с векторными процессорами (интеллектуальный модуль)

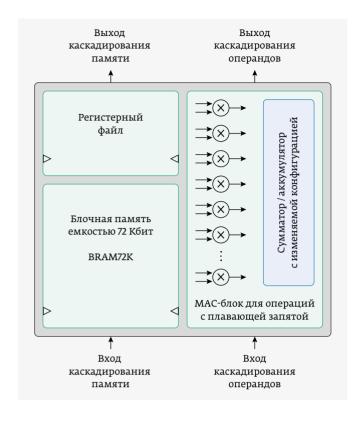

Рис. 3. Структура MLP-блока ПЛИС серии Speedster7t от Achronix

вычислительных элементов, организованных в процессоры машинного обучения (МLР-блоки). МLР – легко настраиваемый процессорный блок, в состав которого входит до 32 умножителей/аккумуляторов (МАС) (рис. 3). Каждый из них поддерживает целочисленные форматы от 4 до 24 бит и различные режимы с плавающей точкой, включая встроенную поддержку формата bfloat16, а также высокоэффективный блочный формат с плавающей точкой, который значительно повышает произво-

В MLP-блоки интегрирована блочная память для обеспечения работы алгоритмов машинного обучения с максимальной производительностью на частоте 750 МГц. Сочетание большого количества вычислительно-интенсивных блоков и скоростного обмена данными позволяет создать процессорную структуру, быстродействие которой достигает 134 TOPS с инструкциями Int8 (8-битные целочисленные значения). Для сравнения: GPU-ускоритель Tesla P40 на базе архитектуры Pascal от Nvidia с количеством CUDA-ядер, равным 3840, обеспечивает быстродействие 47 TOPS. У ПЛИС Xilinx серии AI core быстродействие составляет 49-147 TOPS с инструкциями Int8.

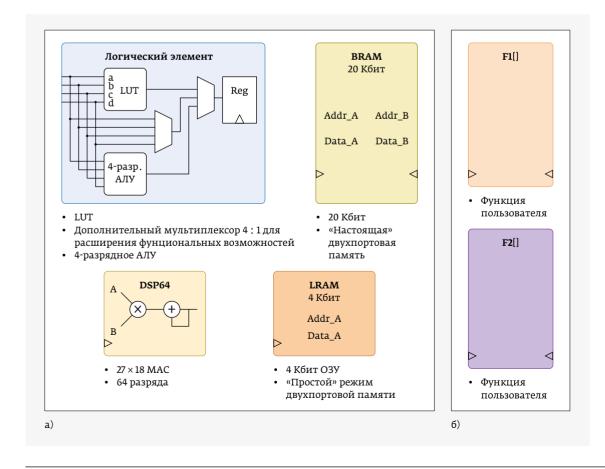

ПЛИС серии Speedster7t содержат от 336K до 2,6M 6-входовых LUT с дополнительным мультиплексором для реализации различных комбинационных функций

Рис. 4. Структура eFPGA-блоков: a - Speedcoreблоки; б - блоки для реализации функций пользователя

и быстрым сумматором, до 385 Мбит встроенной памяти, а также до 16 каналов GDDR6 со скоростью обмена до 4 Тбит/с, порты PCI Express Gen5, до 72 портов трансиверов (SerDes) со скоростью передачи от 1 до 112 Гбит/с, 4 порта 400 Гбит/с Ethernet или 16 портов по 100 Гбит/с Ethernet. В этих ПЛИС используются встроенные блоки памяти Logic RAM для логических функций LRAM2k и LRAM4k емкостью 2 и 4 Кбайт, соответственно, и блочная память Block RAM (BRAM) большого объема (72 Кбайт) для ЦОС-задач и машинного обучения. В ЦОС-блок (DSP-64) входят умножитель с размерностью операндов 18 × 27, 64-разрядный аккумулятор и 27-разрядный предсумматор.

Благодаря сочетанию программируемости, свойственной ПЛИС, со структурами маршрутизации заказных БИС и вычислительными ресурсами, серия Speedster7t позволяет создать новый класс встраиваемых ПЛИС (eFPGA) для БИС СНК. eFPGA поставляются как лицензированные IP-ядра в формате GDS II для интегрирования в кристалл БИС СНК. На одном кристалле может располагаться массив ПЛИС (причем разработчик БИС самостоятельно определяет объем логических ресурсов, памяти, количество ЦОС-блоков и процессоров машинного обучения), а также, например, 8-ядерный процессор общего применения (рис. 4). Такое решение дает возможность уменьшить площадь встраиваемого массива ПЛИС благодаря сокращению избыточных ресурсов, что оптимизирует энергопотребление. Кроме того,

уменьшаются задержки обращения к массиву ПЛИС по сравнению с вариантом, когда ПЛИС реализуется в виде отдельного кристалла, а также снижается стоимость разработки. ПЛИС eFPGA Speedcore в виде IP-ядер разработаны под технологический процесс 16FF+ на TSMC.

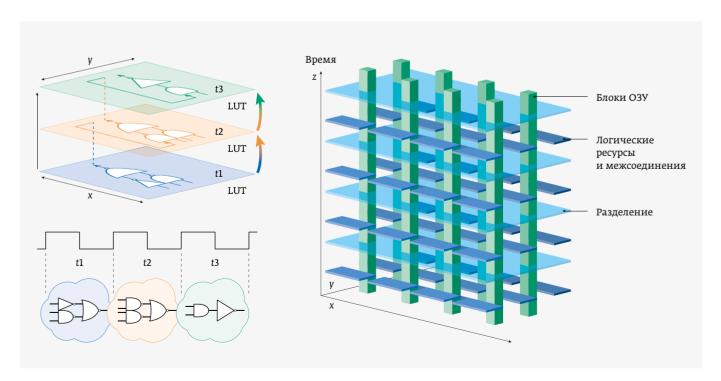

Несмотря на то, что фаблесс-компания Tabula, как уже отмечалось, в 2015 году прекратила свою деятельность, следует упомянуть ее разработку — ПЛИС на основе СОЗУ серии ABAX с пространственно-временной архитектурой (рис. 5). Логические ресурсы ПЛИС распределены на восемь пространственных слоев, площадь каждого примерно в три раза меньше площади кристалла ПЛИС. Коммутация между слоями осуществляется с частотой 1,6 ГГц, при этом могут быть задействованы не все слои. При использовании всех восьми слоев для получения максимальной емкости ресурсов ПЛИС можно достичь максимальной рабочей частоты 200 МГц, а при использовании четырех частота удвоится. Такой подход позволяет повысить быстродействие в результате уменьшения времени маршрутизации внутри слоя.

ПЛИС ABAX производятся на Intel по 22-нм технологическому процессу (ранее выпускались в TSMC по 40-нм процессу). В качестве примера приведем характеристики ПЛИС AIECO6 на основе 40-нм технологии TSMC: базовая частота 1,6 ГГц; частота для одного разделения 200 МГц; восемь временных разделений на кристалл; 630 тыс. LUT; 960 блоков регистровых файлов размерностью 64×9 бит; большие (LRAM) и средние (MRAM)

**Рис. 5.** ПЛИС ABAX от Tabula: слева – принцип пространственно-временного разделения булевой логики; справа – организация логических и трассировочных ресурсов, блочной памяти и их разделение

блоки памяти - 480×72 Кбит и 240×36 Кбит; СОЗУ емкостью 5,5 Мбайт; 1280 МАС-модулей с умножителями размерностью 18×18; 920 параллельных портов ввода-вывода; 48 трансиверов со скоростью обмена от 55 Мбит/с до 6,5 Гбит/с.

В 2010 году стартап SiliconBlue представил ПЛИС по технологии СОЗУ серии iCE65L08F-TCB132 со сверхнизким энергопотреблением для портативных потребительских приложений (рис. 6). Сегодня эти устройства выпускаются под торговой маркой компании Lattice Semiconductor по 65-нм КМОП-технологии TSMC с низким энергопотреблением. ПЛИС серии iCE65L08 содержат 7680 логических ячеек, 32 блока памяти типа RAM4K емкостью по 128 Кбит, максимальная рабочая частота составляет 256 МГц. Устройства отличаются низким током потребления (12 мкА в статическом режиме), работают в двух режимах – малая мощность и высокое быстродействие, что актуально для систем с батарейным питанием. Для программирования в системе ПЛИС содержит энергонезависимую защищенную конфигурационную память (NVCM), а также интегрированный интерфейс SPI.

В настоящее время Lattice предлагает более продвинутую серию іСЕ40, выпускаемую по 40-нм технологическому процессу. По структуре PLB-блока iCE40 схожа с іСЕ65, но содержит встроенные ЦОС-блоки, широкий набор интерфейсов: два SPI, два I2C, Parallel RGB, 7:1 LVDS, MIPI DPI/DBI, HiSPi, subLVDS, LVDS, Parallel

LVCMOS, блоки ФАПЧ. Наряду с официальной средой разработки iCECube2 существует открытая аппаратная платформа icoBoard 1.0, которая представляет собой отладочный набор на базе ПЛИС іСЕ40. Особенность данной платформы – использование для программирования ПЛИС открытого и бесплатного ПО icoTC (Verilogto-bitstream FPGA toolchain), основными компонентами которого являются синтезатор YoSys; инструмент размещения и трассировки Arachne-pnr; программные инструменты для формирования битового потока; загрузчик битового потока (программатор) ісергод.

Компания Lattice конкурирует в низовой категории ПЛИС с компанией OuickLogic, выпускающей ПЛИС серии PolarPro 3/3E. Логическая ячейка ПЛИС PolarPro 3/3E идентична PLB-блоку Lattice, однако является «крупнозернистой», булевы функции могут быть реализованы на двух 3-LUT и одной 4-LUT. Такая структура значительно улучшает трассируемость проектов в ПЛИС.

Кроме того, QuickLogic выпускает встраиваемые eFPGA серии ArcticPro в виде IP-ядра, интегрируемого с СнК, на основе 65-нм технологического процесса TSMC (а также по 40-нм процессу компании SMIC). В 2002 году в ПЛИС QuickLogic было интегрировано микропроцессорное ядро MIPS. Архитектура получила название QuickMIPS Multi-core SoC (180 нм). В 2017 году компания разработала современную многоядерную ПЛИС СНК – EOS S3 Multi-core SoC (40-нм технология).

Рис 6 PLB-блок ПЛИС компании Lattice (SiliconBlue)

Новая серия ArcticPro 2 от QuickLogic выпускается на кремниевой фабрике GlobalFoundries (США) по технологическому процессу 22FDX (кремний-на-изоляторе с полностью обедненным слоем, DF-SOI), предназначенному для производства заказных специализированных СБИС для беспроводных сетей 5G, Al-ускорителей, Интернета вещей. Кроме того, производство ArcticPro 2 планируется развер-

нуть на мощностях Samsung с применением 28-нм технологического процесса «кремний-на-изоляторе».

В низовой категории ПЛИС на основе СОЗУ, выпускаемых по 55-нм процессу, следует выделить быстро развивающийся стартап Gowin Semiconductor, предлагающий ПЛИС с трассировочной структурой, подобной FLEX Altera, но с современными элементами логического блока (по два 4-LUT и два триггера в секции), характерными для серий Altera Cyclone III, Stratix III и ПЛИС Xilinx XC4000. Например, ПЛИС серии Arora GW2A-55 содержит 54720 4-входовых LUT, 41040 триггеров логических блоков, блочную память BRAM объемом 2520 Кбит, 40 умножителей с размерностью операндов 18 × 18.

**Рис. 7.** Проводящий мостик или диэлектрическая перемычка (ONO-перемычка)

Выпускается также серия LittleBee — низковольтные, малопотребляющие энергонезависимые ПЛИС (55-нм технология) на основе флеш-технологии. ПЛИС серии GWIN поддерживает новые интерфейсы MIPI I3C и MIPI D-PHY для сопряжения с датчиками (например, видеокамер) и другими ИС. В них может быть интегрировано микропроцессорное ядро ARM Cortex-M3 и SAR-АЦП (для ПЛИС GWINS-2C) с поддержкой операционных систем реального времени uCOSIII и FreeRTOS.

ПЛИС от Gowin Semiconductor основаны на архитектуре британской компании Arm Holdings. В САПР Gowin для RTL-синтеза в базис ПЛИС используется программное обеспечение от Synopsys.

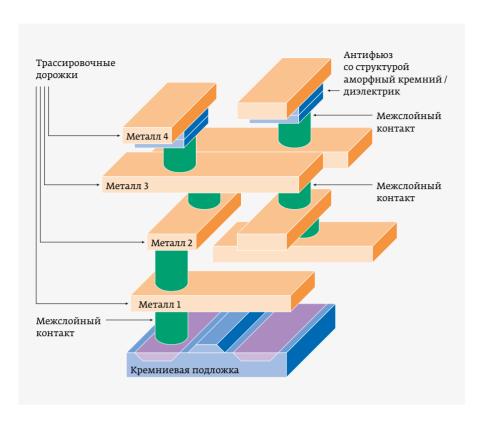

## ПЛИС СТОКОПРОВОДЯЩИМИ ПЕРЕМЫЧКАМИ («АНТИФЬЮЗ»)

Основные производители ПЛИС по технологии «антифьюз» (antifuse проводящий мостик): Microsemi (Actel). Cobham Semiconductor Solutions (Aeroflex), QuickLogic. Такие ПЛИС относятся к категории однократно программируемых устройств (OTP).

Возможны два подхода в реализации «антифьюза».

Компания Actel в своих ПЛИС использует структуру «оксид-нитридоксид» (oxid-nitrid-oxid, ONO-перемычка или диэлектрическая перемычка). Диэлектрическая перемычка (оксид-нитрид-оксидный диэлектрик) находится между диффузионной областью n<sup>+</sup> и поликремнием, расположенным сверху (рис. 7). Программирующий импульс напряжения пробивает перемычку и создает проводящий канал между поликремниевым электродом и диффузионной областью n+.

Типичная толщина ONO-перемычки составляет около 86 Å и лимитируется процессом роста нитрида при химическом парофазном осаждении (CVD-нитрид). Позднее толщина перемычки была повышена до 93 Å для ПЛИС Actel серии RH1020 и до 99 Å – для серии RH1280. ONO-перемычка запатентована компанией Actel под торговым знаком PLICE. В настоящее время PLICE-перемычка используется в серии АСТ 2.

Второй подход предусматривает создание между двумя верхними слоями металлизации низкоомного канала на основе аморфного (некристаллического) кремния с подслоем диэлектрика (опционально), это так называемая МІМ-перемычка (рис. 8). В незапрограммированном состоянии аморфный кремний ведет себя как диэлектрик, а при программировании преобразуется в токопроводящий поликристаллический кремний. Сопротивление перемычки в запрограммированном состоянии составляет 20-100 Ом, типичная толщина перемычки около 500-1000 Å в зависимости от производителя.

Такие перемычки можно рассматривать как наращиваемые. Для них характерен ряд преимуществ перед ONO-перемычкой. В частности, более высокий порог линейной передачи энергии (LET) с 40 до 80 МэВ см²/мг при воздействии ионизирующего излучения делает их привлекательными для использования в аэрокосмических применениях.

Рис. 8. МІМ-перемычка ПЛИС компании Microsemi

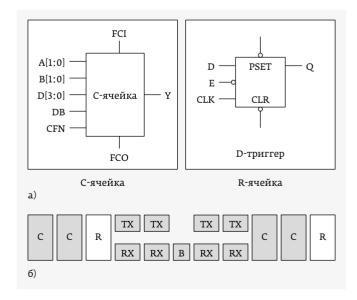

Компания Microsemi выпускает ПЛИС с токопроводящими MIM-перемычками серий Axcelerator и RTAX (радиационно-стойкие, с ЦОС-блоками). На рис. 9 показаны комбинационная и регистерная ячейки (модули) ПЛИС Axcelerator.

Рис. 9. ПЛИС серии Axcelerator: а - комбинационная ячейка (С-модуль) и регистерная ячейка (R-модуль); б - кластер, состоящий из модулей C, R, TX и RX

# Chip EXPO-2020 компоненты | оборудование | технологии

ВЫСТАВКА ПРОЙДЕТ

## 15-17.09

В ТЕХНОПАРКЕ ИННОВАЦИОННОГО ЦЕНТРА

## ТЕМАТИЧЕСКИЕ ЭКСПОЗИЦИИ:

- Экспозиция Департамента радиоэлектронной промышленности Минпромторга России, включая:

- экспозицию предприятий, являющихся изготовителями изделий, включенных в единый реестр российской радиоэлектронной продукции (Постановление Правительства РФ №878),

- экспозицию разработок, созданных в рамках государственной программы «Развитие электронной и радиоэлектронной промышленности на 2013—2025 годы» [Постановление Правительства РФ №109],

- экспозицию разработок, обеспечивающих выполнение приоритетных национальных проектов.

- Дивизионы кластера «Радиоэлектроника» ГК «Ростех»

- Квалифицированные поставщики ЭКБ

- Участники конкурса «Золотой Чип»

- Стартапы в электронике

- Консорциумы и дизайн-центры по электронике

- 🌘 Корпорация развития Зеленограда

## ОФИЦИАЛЬНАЯ ПОДДЕРЖКА:

## ОРГАНИЗАТОРЫ:

**Рис. 10.** Логическая ячейка ПЛИС Cobham серии RadTol Eclipse

MIM-перемычка компании QuickLogic на аморфном кремнии запатентована под торговым знаком ViaLink. С этой технологией компания вышла на рынок ПЛИС более 30 лет назад и в настоящее время выпускает следующие серии ПЛИС: PolarPro, PolarPro II, Eclipse II, Eclipse Plus, Eclipse.

Еще один производитель ПЛИС на основе «антифьюз» — компания Aeroflex, получившая лицензию на ПЛИС серии Eclipse компании QuickLogic. В настоящее время компания преобразована в Cobham Semiconductor Solutions (www.cobham.com/HiRel) и продолжает выпускать UT6325 серии Eclipse по 250-нм КМОП технологическому процессу. Логическая ячейка ПЛИС Cobham серии RadTol Eclipse представлена на рис. 10.

0 0 0

Анализ показывает, что 90% рынка ПЛИС контролируют компании Xilinx, Achronix, Atmel, Intel (Altera), Lattice Semiconductor, Atmel Corporation, Microsemi (Actel).

В ПЛИС СНК Intel и Xilinx интегрированы самые передовые решения в области микропроцессорных ядер, высокоскоростной памяти и интерфейсов. Игроки второго эшелона, такие как Achronix и QuickLogic, предлагают новый класс встраиваемых ПЛИС (eFPGA) для СБИС СНК в виде IP-ядер в GDS-формате.

Следует отметить, что радиационно-стойкие ПЛИС с перемычками («антифьюз») выпускаются уже более 30 лет, и многие компании не планируют прекращать их производство.

### ЛИТЕРАТУРА

- 1. Intel Agilex FPGA Advanced Information Brief. www.intel.ru

- Intel Agilex FPGAs Deliver a Game-Changing

Combination of Flexibility and Agility for the Data-Centric

World. www.intel.ru

- Al Engines. White Paper. WP506 (v1.0.2) October 3, 2018. www.xilinx.com

- 4. Versal ACAPs. White Paper. WP505 (v1.0.1) September 23, 2019. www.xilinx.com

- Versal Architecture and Product Data Sheet: Overview. DS950 (v1.2) July 3, 2019. – www.xilinx.com

- 6. Speedster7t FPGAs. Product Brief. www.achronix.com

- 7. Speedcore eFPGAs. Product Brief. www.achronix.com

- 8. Tabula Spacetime Architecture. White Paper. www.tabula.com

- 9. Abax Product Familiy Overview. www.tabula.com

- 10. iCE40 Ultra Family. Data Sheet. FPGA-DS-02028-2.3. August 2018. www.latticesemi.com

- QuickLogic PolarPro 3 Solution Platform Brief. www.quicklogic.com

- 12. FD-SOI Technology Innovations Extend Moore's Law. White Paper, September 2015. www.globalfoundries.com

- 13. GOWIN. GW2A series of FPGA Products Data Sheet DS102-1.8E, 10/12/2019. www.qowinsemi.com/en

- 14. Cobham Semiconductor Solutions. UT6325 RadTol Eclipse FPGA. January 10, 2017. www.cobham.com/HiRel

- 15. Microsemi Corporation. Axcelerator Family FPGAs. Revision 18. March 2012. www.microsemi.com

- 16. ПЛИС и параллельные архитектуры для применения в аэрокосмической области. Программные ошибки и отказоустойчивое проектирование/Под ред. Ф. Кастеншмидт, П. Реха; пер. с англ. и научн. ред. С. Цыбина, А. Быстрицкого, А. Строгонова, П. Городкова. М.: ТЕХНОСФЕРА, 2018. 326 с.

- 17. **Строгонов А. В.** Реализация цифровых устройств в базисе программируемых логических интегральных схем: учебное пособие / Под ред. С. И. Рембезы. Электрон. текстовые данные. Саратов: Ай Пи Эр Медиа, 2019. 151 с. 978-5-4486-0541-3.