### Особенности памяти LPDDR5 и ее поддержка

С. Белоусов $^1$ , Б. Мёрдок $^2$

УДК 004.332.33:004.072 | ВАК 05.27.01

В начале 2019 года ассоциация по твердотельным технологиям JEDEC выпустила новый стандарт LPDDR5, который должен прийти на смену широко используемому сейчас LPDDR4/4X в устройствах с низким энергопотреблением. Новый стандарт обеспечивает большее быстродействие, до 6400 Мбит/с, одновременно с этим снижая потребление питания. В статье рассмотрены основные особенности LPDDR5, а также приведены решения, которыми обладает компания Synopsys для построения систем с памятью нового типа.

ропускная способность памяти — это один из основных параметров, определяющих быстродействие любой электронно-вычислительной системы, начиная от систем искусственного интеллекта и облачных вычислений и заканчивая автомобильной электроникой и Интернетом вещей. Синхронная динамическая память с произвольным доступом и удвоенной скоростью передачи данных (DDR SDRAM) в настоящий момент является фактически единственным типом основной оперативной памяти для вычислительных устройств, которая удовлетворяет нескольким ключевым требованиям, таким как: большая емкость, простота архитектуры, высокое быстродействие и низкая цена. Далее для краткости под DRAM-памятью понимается DDR SDRAM.

Еще одним преимуществом является то, что такая память выпускается в различных форм-факторах — в виде двухстороннего модуля памяти (Dual In-line Memory Module, DIMM) или дискретного модуля DRAM.

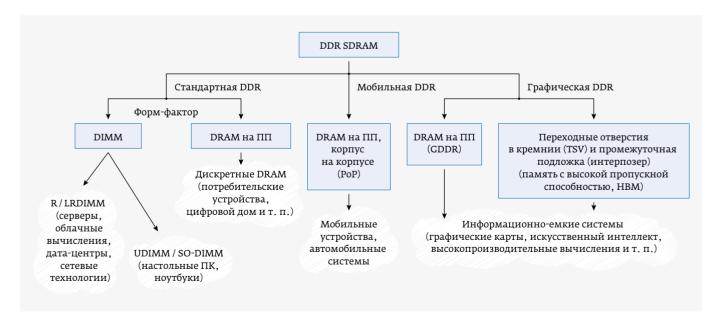

Ассоциация JEDEC выделяет три основных типа DRAM-памяти на основе областей их применения: стандартная DDR, графическая DDR и мобильная DDR, или DDR с низким энергопотреблением (Low Power DDR, LPDDR) (рис. 1). Последнему типу в настоящее время уделяется огромное внимание в связи с непрерывным развитием рынка портативной и автомобильной электроники, а также концепции Интернета вещей.

По своей сути LPDDR-память представляет собой массив ячеек хранения, выполненных на базе конденсаторов,

Рис. 1. Классификация памяти DDR SDRAM

Компания Synopsys, ведущий инженер по применению.

<sup>&</sup>lt;sup>2</sup> Компания Synopsys, менеджер по развитию продукта.

#### Сравнение характеристик LPDDR5 DRAM и LPDDR4/4X DRAM

|                                | LPDDR5 DRAM       | LPDDR4/4X DRAM |

|--------------------------------|-------------------|----------------|

| Емкость, Гбит на канал         | 232               | 216            |

| Количество банков              | 4; 8; 16          | 8              |

| Емкость страницы, байт         | 1024, 2048 и 4096 | 2048           |

| Пропускная способность, Мбит/с | До 6400           | До 4266        |

| Напряжения питания, В          |                   |                |

| Массив DRAM                    | 1,8               | 1,8            |

| Ядро                           | 1,05/0,9          | 1,1            |

| Сигнальная шина                | 0,5/0,3           | 1,1/0,6        |

аналогичных тем, что используются в DDR стандартного типа. Главной особенностью такого типа памяти является низкое энергопотребление, что является необходимым условием использования ее в мобильных устройствах. Оно обеспечивается наличием дополнительных функциональных возможностей, позволяющих переводить устройство в режим глубокого сна или снижать рабочие частоты, используя функцию динамического масштабирования частоты. Кроме того, небольшая длина межсоединений между контроллером и памятью, а также уменьшенная до 16—32 бит ширина канала по сравнению со стандартной для DDR 64-битной шириной позволяют получить большую пропускную способность канала LPDDR-памяти, чем у стандартной DDR того же поколения.

В настоящее время в большинстве современных устройств, для которых вопрос энергопотребления является ключевым, применяется LPDDR-память четвертого поколения – LPDDR4. Она обеспечивает пропускную способность канала до 4266 Мбит/с при напряжении питания 1,1 В. Существует также модификация LPDDR4X, которая обладает лучшими характеристиками с точки зрения потребляемой мощности за счет снижения напряжения высокого уровня (уровня «1») в сигнальной шине памяти (VDDQ) до 0,6 В при одновременном сохранении основных для LPDDR4 характеристик.

Ключевыми особенностями LPDDR5 является больший объем памяти, увеличенная до 6400 Мбит/с пропускная способность и новые возможности для уменьшения энергопотребления. Технические характеристики LPDDR5 в сравнении с LPDDR4/4X представлены в таблице.

LPDDR5 работает на напряжениях питания ядра 1,05 В и сигнальной шины 0,5 В в режиме с высокой частотой передачи данных и 0,9 и 0,3 В соответственно в режиме с пониженной частотой. Таким образом LPDDR5 поддерживает динамическое переключение питания (Dynamic Voltage Scaling, DVS) как для сигнальной шины, так и для ядра в отличие от LPDDR4X, где такая

возможность была только у сигнальной шины.

Помимо указанных выше изменений в технических характеристиках, в LPDDR5 добавлены новая функциональность, повышающая устойчивость памяти к ошибкам при передаче данных, и новые возможности для управления энергосберегающим режимом. Кроме того, принципиально изменена схема синхронизации между контроллером и памятью. Рассмотрим новые возможности, которые доступны в LPDDR5, более подробно.

## ЭКВАЛАЙЗЕР С РЕШАЮЩЕЙ ОБРАТНОЙ СВЯЗЬЮ ПЕРВОГО ПОРЯДКА

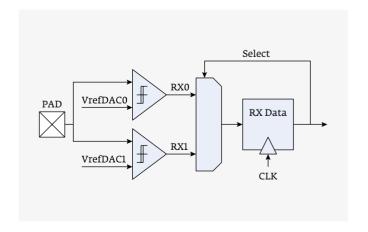

Использование эквалайзера с решающей обратной связью (Decision Feedback Equalizer, DFE) позволяет ослабить эффект межсимвольной интерференции, возникающий из-за влияния «хвостов» предыдущих импульсов, которое необходимо компенсировать на стороне приемника [1]. В структуру LPDDR5 входит опциональный эквалайзер с решающей обратной связью первого порядка, обеспечивающий высокую надежность приемника даже в случае работы памяти на предельных частотах 6 400 МГц (рис. 2).

#### KOMAHДA WriteX

В LPDDR5 добавлена специальная команда WriteX, позволяющая произвести запись всей памяти или отдельной ее области константными величинами, например «все нули», без передачи данных по шине DQ, снижая тем самым энергопотребление.

**Рис. 2.** Схема эквалайзера с решающей обратной связью памяти LPDDR5

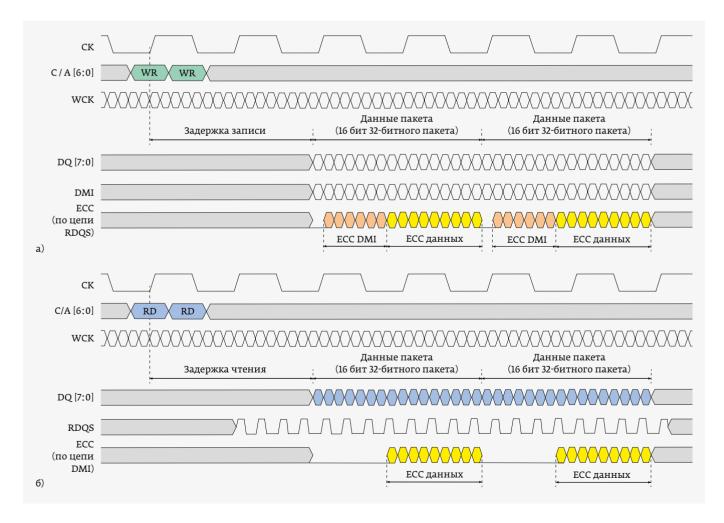

#### СИГНАЛ КОРРЕКЦИИ ОШИБОК

Дополнительный сигнал коррекции ошибок (Link Error Correction Code, Link ECC) позволяет автоматически детектировать и исправлять ошибки при передаче данных между памятью и контроллером, вызванные шумом. Данная опция доступна как при записи, так и при чтении памяти в режиме пакетной передачи данных (Burst). При записи контроллером формируется контрольная сумма ЕСС, которая передается по цепи RDQS (рис. 3a). При чтении контрольную сумму ЕСС формирует память и передает ее по цепи DMI (рис. 36). После приема ECC памятью или контроллером происходит автоматическое вычисление собственной контрольной суммы на основе полученных данных и сравнение с принятым значением ЕСС. В случае их идентичности данные считаются корректными и они могут быть приняты для хранения или в дальнейшую обработку. В случае если возникла единичная ошибка при передаче, данные автоматически исправляются и только после этого получают статус корректных. Таким образом, функция Link ECC обеспечивает высокую помехоустойчивость канала связи даже на высоких частотах, что особенно важно

при использовании LPDDR5 в задачах, связанных с автомобильной электроникой, где предъявляются высокие требования к стабильности работы памяти.

#### КОНФИГУРИРУЕМОЕ КОЛИЧЕСТВО БАНКОВ

LPDDR5 DRAM поддерживает динамическое конфигурирование количества используемых банков для установки необходимого числа транзакций чтения или записи в режиме Burst в зависимости от паттернов данных, с которыми предстоит работать. Доступны следующие конфигурации:

- 1. Режим групп банков (Bank-group, BG) 4 группы по 4 банка в каждой. Данный режим оптимален при работе на скоростях выше 3 200 Мбит / с. Число транзакций в режиме Burst 16 или 32.

- 2. Режим «8 банков». Данная конфигурация памяти может быть использована для любых скоростей передачи данных. Число транзакций в режиме Burst 32.

- 3. Режим «16 банков». Применяется для скоростей обмена до 3200 Мбит / с. Число транзакций в режиме Burst 16 или 32.

Рис. 3. Временные диаграммы записи (a) и чтения (б) памяти с функцией Link ECC

#### ДИНАМИЧЕСКОЕ МАСШТАБИРОВАНИЕ ЧАСТОТЫ

В памяти LPDDR4/4X для шин команд/адреса (C/A) и данных (DQ) была возможность выбора из двух рабочих частот (Frequency Set Points, FSP). В LPDDR5 можно выбирать из трех различных FSP для обеих шин. Это позволяет контроллеру быстро переключаться между разными рабочими режимами в зависимости от выбранного энергопотребления, реализуя тем самым функцию динамического масштабирования частоты (Dynamic Frequency Scaling, DFS). Совместное использование динамического переключения напряжения и масштабирования частоты делает решение, основанное на памяти типа LPDDR5, самым эффективным с точки зрения энергопотребления по сравнению с использованием LPDDR предыдущих поколений.

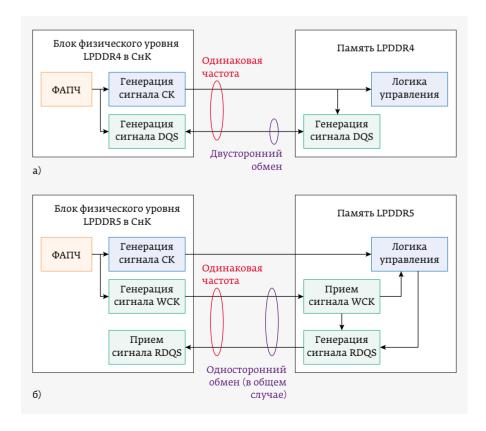

#### НОВАЯ СХЕМА СИНХРОНИЗАЦИИ

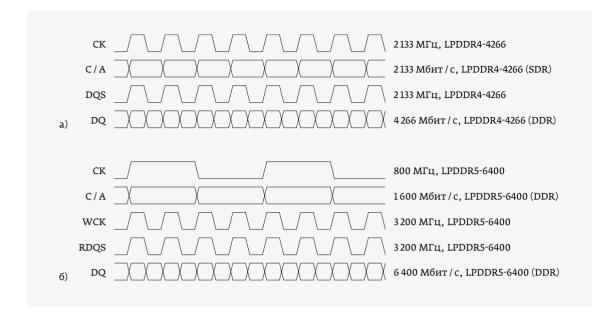

Одним из основных нововведений в LPDDR5 является новая система синхронизации. В предыдущих поколениях памяти LPDDR использовалась единая частота для синхронизации интерфейса между контроллером и памятью. Сигнал СК использовался для определения скорости передачи команд и адреса по шине C/A, что, в свою очередь, ограничивало частоту DQS и пропускную способность шины DO.

Например, для LPDDR4 частота СК и строб данных

DQS работают на максимально возможной частоте 2133 МГц. Шина С/А, в свою очередь, работает в режиме SDR (Single Data Rate), изменяя свое состояние только по одному активному фронту сигнала СК. Таким образом, максимальная пропускная способность шины С/А составляет 2133 Мбит / с. Поскольку шина DO работает по двум фронтам сигнала DQS, ее эффективная пропускная способность составляет 4266 Мбит/с. Строб данных, в свою очередь, является двунаправленным сигналом и реализован дифференциальной парой (рис. 4а).

В стандарте LPDDR5 вместо строба данных DQS вводится два дифференциальных сигнала: сигнал WCK, формируемый контроллером, который используется как строб записи данных в память, и сигнал RDQS, формируемый памятью, применяемый в качестве строба чтения данных из памяти. Сигнал RDQS генерируется на основе сигнала WCK, полученного от контроллера (рис. 46). В общем

№4 (00195) 2020

случае сигналы WCK и RDQS являются однонаправленными, однако иногда, например при использовании механизма Link ECC, сигнал RDQS может работать в двунаправленном режиме.

Введение дополнительных сигналов WCK и RDQS, работающих на частоте 3200 МГц, позволяет снизить частоту традиционного сигнала синхронизации СК до 800 МГц, сохраняя одновременно с этим требуемую пропускную способность канала 6400 Мбит/с. Кроме того, низкая частота СК позволила перевести режим работы шины С/А с SDR на DDR, обеспечивая ее быстродействие 1600 Мбит/с, необходимое для LPDDR5, в то время как для LPDDR4, чтобы обеспечить максимальное быстродействие шины С/А 2133 Мбит/с, требовалась частота СК 2133 МГц (рис. 5).

Возможно, достичь требуемого быстродействия в 6400 Мбит/с можно было бы простым удвоением рабочей частоты СК, как было неоднократно сделано прежде, при разработке предыдущих поколений стандартов DDR и LPDRR. Для того чтобы понять, почему было принято решение изменить интерфейс, а не увеличивать частоту СК, следует рассмотреть систему «контроллер — память» отдельно.

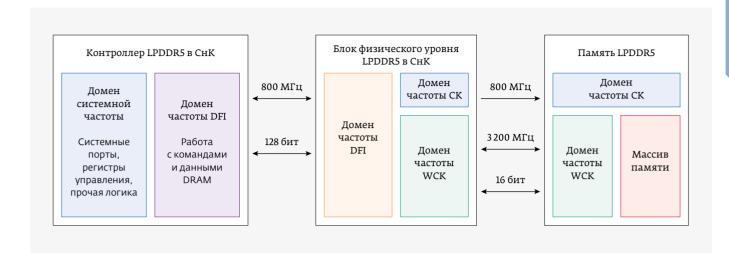

В каждом устройстве, работающем с памятью типа DDR/LPDDR, присутствуют контроллер и цифроаналоговый блок физического уровня (PHY). Контроллер отвечает за формирование необходимых команд, адреса

Рис. 4. Синхронизация в интерфейсе памяти LPDDR4 (a) и LPDDR5 (б)

Рис. 5.

Соотношение

частот сигналов

синхронизации

и пропускной

способности

шин С/А и DQ

памяти

LPDDR4 (a)

и LPDDR5 (б)

и данных. Блок же физического уровня преобразует их в аналоговый вид для дальнейшей передачи на блок памяти. Контроллер и блок PHY взаимодействуют через специальный интерфейс DFI (DDR PHY Interface) (рис. 6).

Рассмотрим частоты, используемые в такой системе, на примере LPDDR4. Как говорилось выше, сигнал DQS, обеспечивающий требуемое быстродействие 4266 Мбит/с, должен иметь частоту 2133 МГц, как и сигнал СК. Это означает, что блок PHY интерфейса LPDDR4 должен также работать на частоте 2133 МГц. Обычно соотношение частот между контроллером и блоком PHY составляет 1:2, то есть на один такт рабочей частоты контроллера приходятся два такта PHY. Этот режим получил название DFI 1:2. Таким образом, рабочая частота контроллера в данном случае равна 1066 МГц.

При простом удвоении частоты LPDDR4 мы в теории могли бы получить пропускную способность шины DQ в 8532 Мбит/с. Однако требования к частоте контроллера оказались бы невыполнимыми или выполнимыми с большим трудом даже на существующих сегодня проектных нормах. Например, для работы в режиме DFI 1:2 потребовалась бы рабочая частота контроллера 2133 МГц.

Рис. 6.

Взаимодействие контроллера DDR/LPDDR, блока физического уровня и памяти

Реализованная в LPDDR5 схема синхронизации позволяет снизить рабочую частоту контроллера. В случае если интерфейс работает с максимальным быстродействием 6400 Мбит / с, данные передаются на частоте в 3200 МГц. Можно предположить, что, по аналогии с LPDDR4, частота контроллера в данном случае составляет 1600 МГц, однако это не так. В действительности контроллер работает на частоте СК, которая, как указано выше, составляет 800 МГц, а требуемая пропускная способность достигается за счет использования режима DFI1:4. В случае LPDDR5 этот режим обозначается DFI1:1:4, поскольку в системе теперь присутствуют два соотношения рабочих частот: частота контроллера к частоте СК и частота контроллера к частоте СК и частота контроллера к частоте WCK (рис. 7).

## ПРИМЕНЕНИЕ РЕШЕНИЯ Synopsys DesignWare LPDDR5 / 4 / 4X ДЛЯ ПОСТРОЕНИЯ СИСТЕМ C НОВЫМ ТИПОМ ПАМЯТИ LPDDR5

Указанные выше возможности памяти LPDDR5 являются естественным продолжением технологии LPDDR, которая присутствует на рынке уже более 10 лет. За это время пропускная способность интерфейса LPDDR выросла в 16 раз — с 400 Мбит/с в модулях LPDDR первого поколения до 6 400 Мбит/с в модулях LPDDR5. Это стало возможным не только за счет непрерывного уменьшения технологических норм ИС и улучшения архитектуры контроллеров памяти и блоков физического уровня РНУ, но и за счет тесного сотрудничества между ведущими компаниями — разработчиками микросхем и систем проектирования в рамках ассоциации JEDEC.

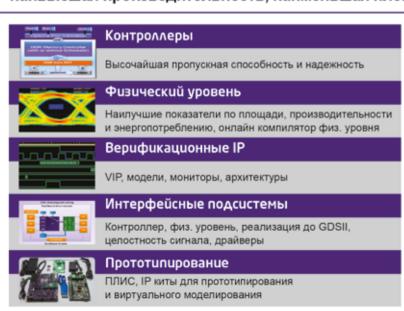

Компания Synopsys, будучи не только крупнейшим производителем САПР в индустрии интегральной электроники, но и обладателем обширного портфолио

Рис. 7. Рабочие частоты в режиме DFI 1:1:4

IP-блоков, предоставляемых сторонним заказчикам, является активным членом ассоциации JEDEC уже более 10 лет, принимая деятельное участие в разработке современных интерфейсов. Наличие собственного маршрута проектирования и сильной команды разработчиков IP-блоков для различного применения позволило Synopsys занять и удерживать лидирующие позиции на рынке решений, связанных с DDR/LPDDR-памятью

с 2010 года. В частности, контроллер и блок физического уровня интерфейса LPDDR5 от Synopsys был выпущен на рынок в начале 2019 года, спустя всего месяц после публикации окончательной версии стандарта LPDDR5 ассоциацией JEDEC.

Решение Synopsys DesignWare LPDDR5/4/4X является последней версией контроллера, оптимизированного для работы в системах с низким энергопотреблением.

Значимые показатели: наименьший риск, наименьшая производительность, наименьшая площадь

- Низкий риск: 1600+ DDR выигранных проектов, 10+ лет истории DDR, 75+ тестовых чипов, поставщик DDR в отрасли №1

- Высочайшая производительность и минимальная площадь DDR PHY на передовых технологиях

- Контроллер DDR с наивысшей производительностью – подтверждено множеством оценок Заказчиков

- Производственный опыт с НВМ и НВМ2

- Поддерживает технологические процессы до 5 нм, все ведущие фабрики

- Гибкость: быстрая настройка для любого применения

- Интерфейсные IP-подсистемы: точная интеграция CHK

Подробности на www.synopsys.com Москва, Смоленская площадь, дом 3 Тел: +7 (495) 933 1015

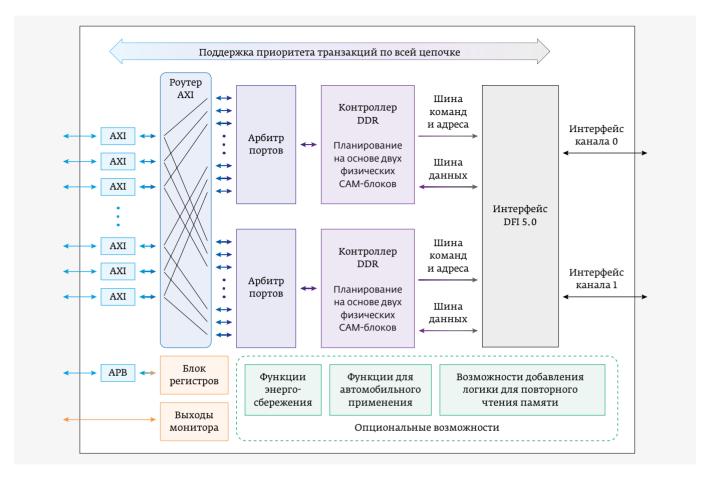

Рис. 8. Структурная схема контроллера Synopsys DesignWare LPDDR5/4/4X

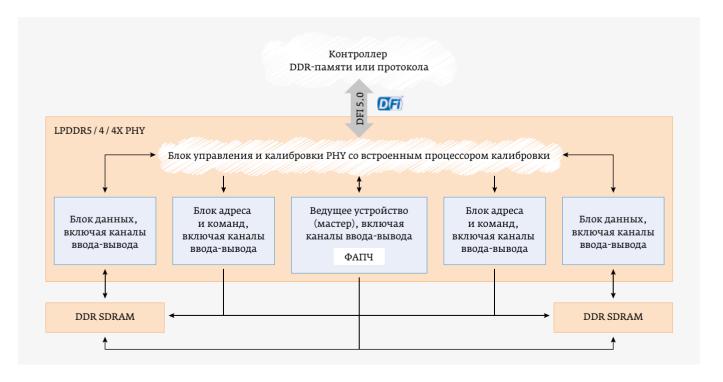

Рис. 9. Взаимодействие блока DesignWare LPDDR5/4/4X PHY с контроллером памяти

Структурная схема данного контроллера приведена на рис. 8. Он может работать с блоками PHY DesignWare LPDDR5/4/4X от компании Synopsys или с блоками физического уровня сторонних поставщиков, которые совместимы со стандартом DFI 5.0. Контроллер поддерживает интерфейс AMBA 4, содержит диспетчер команд и блок детектирования и исправления ошибок, а также полностью соответствует стандарту JEDEC для LPDDR5 [2].

DesignWare LPDDR5/4/4X PHY — законченное решение от компании Synopsys, представляющее собой набор GDSII-макроячеек для формирования необходимой конфигурации интерфейсов LPDDR5/4/4X средствами инструмента DDR PHY compiler и цифровой блок управления и калибровки PUB (PHY Utility Block), содержащий встроенный микропроцессор, отвечающий за выбор оптимальных частотных характеристик канала связи.

Данный блок PHY реализован в 16- и 7-нм базисе, поддерживает интерфейс DFI 5.0, а также обеспечивает пропускную способность до 6400 Мбит / с, необходимую для интерфейса LPDDR5 (рис. 9) [3].

Совместное использование контроллера DesignWare LPDDR5/4/4X и блока физического уровня DesignWare LPDDR5/4/4X PHY позволяет существенно сократить время разработки устройств за счет использования

единого инструмента интеграции от компании Synopsys – coreConsultant, а также обеспечивает необходимое быстродействие и энергопотребление всей системы в целом.

#### ЛИТЕРАТУРА

- Beyene W.T., Amirkhany A. Controlled Intersymbol Interference Design Techniques of Conventional Interconnect Systems for Data Rates Beyond 20 Gbps // IEEE Transactions on Advanced Packaging. November 2008. Vol. 31. No. 4. PP. 731–740.

- 2. LPDDR5/4/4X Controller IP. DesignWare IP Datasheet.

- 3. LPDDR5/4/4X PHY IP. DesignWare IP Datasheet.

- 4. **Murdock B.** Advantages of LPDDR5: A New Clocking Scheme // Сайт Semiconductor Engineering. 5 сентября 2019 г. – https://semiengineering.com/advantages-of-lpddr5-a-new-clocking-scheme/.

- 5. **Sankaranarayanan V.** Key Features Designers Should Know About LPDDR5. Synopsys Technical Bulletin.

- 6. **Sankaranarayanan V.** Which DDR SDRAM Memory to Use and When. Synopsys White Paper. 2019.

- 7. Synopsys Announces Fastest, Most Power Efficient DDR5 and LPDDR5 IP Solutions. October 24, 2018 // https://news.synopsys.com/2018-10-24-Synopsys-Announces-Fastest-Most-Power-Efficient-DDR5-and-LPDDR5-IP-Solutions.

М.: ТЕХНОСФЕРА, 2019. − 326 с..

ISBN 978-5-94836-513-8

#### КНИГИ ИЗДАТЕЛЬСТВА «ТЕХНОСФЕРА»

Цена 920 руб.

# ПЛИС И ПАРАЛЛЕЛЬНЫЕ АРХИТЕКТУРЫ ДЛЯ ПРИМЕНЕНИЯ В АЭРОКОСМИЧЕСКОЙ ОБЛАСТИ. ПРОГРАММНЫЕ ОШИБКИ И ОТКАЗОУСТОЙЧИВОЕ ПРОЕКТИРОВАНИЕ

Под ред. Ф. Кастеншмидт, П. Реха

При поддержке АО «Конструкторско-технологический центр «ЭЛЕКТРОНИКА» Пер. с англ. и научная редакция С. А. Цыбина, к. т. н., АО «КТЦ «ЭЛЕКТРОНИКА», А. В. Быстрицкого, к. т. н., АО «КТЦ «ЭЛЕКТРОНИКА», А. В. Строгонова, д. т. н., ФГБОУ ВО «ВГТУ», П. С. Городкова, ФГБОУ ВО «ВГТУ»

В книге приводится понятие устранимых ошибок, возникающих в ПЛИС типа ППВМ (FPGA – Field Programmable Gate Array) и графических процессорах. Рассматриваются радиационные эффекты в ПЛИС, отказоустойчивые методы для ПЛИС, применение серийно выпускаемых ПЛИС в авиации и космонавтике, экспериментальные данные о воздействии радиации на ПЛИС, встроенные в ПЛИС процессоры под воздействием радиации и внесение ошибок в ПЛИС.

Книга будет полезна не только инженерно-техническим работникам, занимающимся применением серийно выпускаемых ПЛИС в авиации, космонавтике, в приборостроении для транспорта и других критически важных областях народного хозяйства, но и магистрантам, обучающимся по направлению подготовки 11.04.04 «Электроника и наноэлектроника», а также аспирантам, проходящим обучение по направлению подготовки 11.06.01 «Электроника, радиотехника и системы связи».

#### КАК ЗАКАЗАТЬ НАШИ КНИГИ?