# Проектирование корпусов и микросборок по технологии FO WLP средствами CATP MENTOR GRAPHICS

Часть 1

Дж. Фергусон<sup>1</sup>, Д. Вертянов, к. т. н.<sup>2</sup>, К. Фелтон<sup>3</sup>, И. Беляков<sup>4</sup>, С. Евстафьев, к.т.н.⁵, В. Сидоренко6, Н. Горшкова, к.т.н.7

УДК 004.9:621.3 | ВАК 05.13.12

Проектирование и верификация корпусов, микросборок FO WLP требуют взаимного сотрудничества между разработчиками, поставщиками аутсорсинговых услуг по сборке и тестированию изделий микроэлектроники (OSAT), производителями полупроводниковых изделий и продавцами САПР. Средства проектирования, которые имеют необходимую интеграцию и функциональные возможности для работы как с ИС, так и с корпусами позволяют уменьшить риски получения ошибок, брака на этапе корпусирования, а также сократить время выполнения заказов для поставщиков компонентов, компаний OSAT и производителей полупроводниковой продукции. Применение маршрута САПР MENTOR GRAPHICS дает уверенность в том, что разработчики корпусов, микросборок FO WLP имеют все необходимые функциональные возможности, инструменты проектирования и верификации для получения максимальной выгоды от новой технологии корпусирования, активно поддерживаемой рынком в последние несколько лет.

FO WLP (Fan-out wafer-level packaging – корпусирование кристаллов на уровне пластины с использованием внутреннего монтажа) – это активно развивающийся метод группового корпусирования кристаллов, применяемый как для создания корпусов с одним кристаллом, так и для формирования многокристальных сборок. Метод относится к числу так называемых современных технологий корпусирования (advanced packaging), которые противопоставляются традиционной разварке и позволяют уменьшить габариты изделия, сократить длину соединений

между контактами кристалла и корпуса. Кроме FO WLP, к современным методам корпусирования также относятся: Flip-chip-корпусирование, технологии Fan-in WLP, корпусирование посредством внутреннего монтажа кристаллов (embedded die) в коммутационное основание (из металла, диэлектрика, полупроводника), а также создание 2,5D- и 3D-микросборок на основе сквозных отверстий в кремнии TSV (Through Silicon Vias) [1-4].

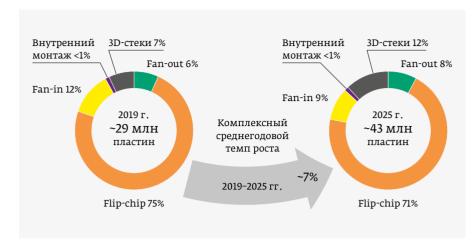

Среди современных методов корпусирования FO WLP (согласно прогнозу Yole Developpement от 2020 года [5]) занимает одну из лидирующих позиций по среднегодовому темпу роста с показателем 16% в период 2019–2024 годов, уступая лишь TSV (21,3%) и внутреннему монтажу в коммутационные основания (18%). При этом по объему рынка FO WLP значительно превосходит внутренний монтаж (рис. 1) [5].

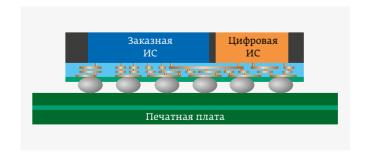

Одним из ключевых преимуществ FO WLP, особенно по сравнению с близкими технологиями Fan-in WLP, является возможность объединить в малогабаритном корпусе несколько кристаллов интегральных схем, изготовленных по различным технологиям и на основе разнородных материалов (рис. 2). Технология FO WLP позволяет создавать корпуса, которые по площади превышают

- Mentor, A Siemens Business, продуктовый директор подразделения Design to Silicon, ru\_soft@mentor.com.

- Институт НМСТ НИУ МИЭТ, руководитель УНЦ, vdv.vertyanov@gmail.com.

- Mentor, A Siemens Business, маркетинг менеджер в области корпусирования, ru\_soft@mentor.com.

- Институт НМСТ НИУ МИЭТ, аспирант, igor-terra@yandex.ru.

- Институт НМСТ НИУ МИЭТ, доцент, madcatse@gmail.com.

- АО «ЗНТЦ», руководитель центра корпусирования и 3D-сборки микросхем, sidorenko@zntc.ru.

- АО НПЦ « ЭЛВИС», начальник лаборатории отдела проектирования аналоговых блоков.

исходный кристалл. Данный факт не противоречит стремлению к миниатюризации электронных изделий, поскольку именно на дополнительной площади размещаются вертикальные межсоединения, позволяющие создавать на основе FO WLP корпусов трехмерные микросборки. Также дополнительная площадь используется для трассировки кристаллов с большим количеством контактных площадок, позволяя эффективнее перераспределять коммутацию от более плотно расположенных площадок кристалла к менее плотно расположенным контактам корпуса.

Первые коммерчески успешные технологии корпусирования кри-

сталлов на уровне пластины с использованием внутреннего монтажа появились в 2006–2010 годах. Это были технология eWLB (Embedded Wafer Level Ball Grid Array) от Infineon и технология RCP (Redistributed Chip Packaging) от Freescale [6, 7].

## ОБЩИЕ СВЕДЕНИЯ О FO WLP

Несмотря на разнообразие решений в области FO WLP, основные этапы процесса корпусирования остаются практически неизменными для разных вариантов технологии. К ним относятся:

- размещение кристаллов на временном носителе (пластине или прямоугольной панели);

- герметизация повторно собранной пластины с кристаллами посредством формовочного компаунда (EMC Epoxy Molding Compound);

- отделение временного носителя (полученную после этого заготовку со встроенными кристаллами называют восстановленной пластиной);

- формирование коммутационных слоев (слоев перераспределения или RDL – redistribution layer);

- разделение заготовки на отдельные корпуса или микросборки.

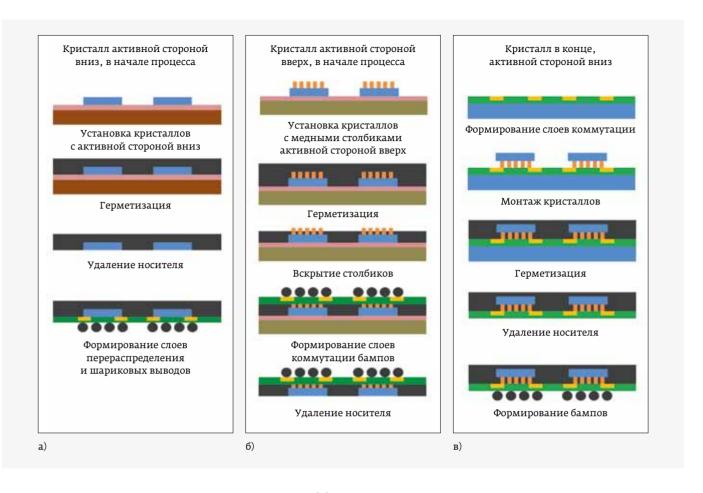

При этом последовательность этапов корпусирования для разных вариантов FO WLP может отличаться. Так, в зависимости от того, как и на каком этапе процесса происходит присоединение кристаллов к носителю, выделяют три варианта технологий FO WLP. Первый вариант – традиционные технологии, в которых кристалл устанавливается активной стороной вниз на адгезив, покрывающий временное основание, в самом начале процесса (рис. 3а) [8]. Именно так изготавливаются корпуса по технологиям RCP и eWLB. Преимущество данного подхода в том, что полностью исключаются процессы пайки и сварки при формировании соединений корпуса,

**Рис. 1.** Развитие рынка современных технологий корпусирования (по числу пластин) на 2019–2025 годы

а также нет необходимости в применении лазерной обработки и специализированных кристаллов.

Альтернативой традиционному подходу является установка кристаллов в начале процесса активной стороной вверх (рис. 36) [8]. При этом на кристаллах либо должны присутствовать заранее подготовленные проводящие столбики, либо после герметизации с помощью лазера должны формироваться отверстия в компаунде до контактов кристалла.

Третий вариант FO WLP значительно отличается от первых двух, поскольку предусматривает монтаж кристаллов с помощью шариковых микробампов на уже сформированные слои перераспределения (слои формируются на временном носителе) – рис. 3в [8]. Основное преимущество метода состоит в том, что кристаллы не смещаются при герметизации, однако данный вариант не является полностью беспаечным.

В технологиях Fan-in и Fan-out WLP обычно не используются переходные отверстия в кремнии (TSV) или специальные многослойные подложки (как в Flip-chip-или Embedded die корпусировании, например подложки,

**Рис. 2.** Пример структуры микросборки, выполненной по технологии FO WLP с двумя встроенными бескорпусными микросхемами

Рис. 3. Различные варианты технологий Fan-out WLP [8]

изготовленные с применением технологии наращивания слоев (build up layers)). При этом в качестве временного носителя обычно применяют именно кремниевую подложку (пластину) или стеклянную прямоугольную панель (в технологиях PLP – panel level packaging). Отказ от TSV и дополнительных подложек не только уменьшает конечную стоимость продукции, но и позволяет компаниям изготавливать корпуса и микросборки с улучшенными электрическими и массогабаритными параметрами.

Технология FO WLP послужила основой для формирования направления 3D WLP-микросборок и реализации конструкций типа «корпус на корпусе» (PoP), которые позволяют значительно повысить уровень интеграции электронных устройств. Это стало возможным благодаря применению сквозных переходных отверстий в корпусе (TPV). В отличие от сквозных отверстий в кремнии, TPV имеют характеристики, схожие с традиционными переходными отверстиями, что позволяет не переживать за надежность и увеличение стоимости. Кроме того, TPV меньше подвержены индуктивному и тепловому воздействию по сравнению с TSV, а также значительно дешевле в производстве.

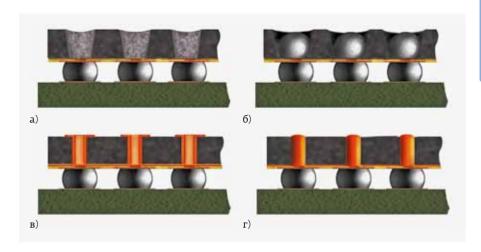

Методы формирования межуровневой коммутации в технологиях 3D WLP схожи друг с другом. Почти все они основаны на создании сквозных отверстий в компаунде по периферии WLP-корпуса (именно на тех участках, которые выступают за пределы границ кристалла), заполняемых впоследствии проводящим материалом. Различия в данных технологиях определяются в основном методами обеспечения электрического контакта. Так, технология WL FO (wafer-level Fan-out) от Amkor technologies предполагает создание с помощью лазера отверстий в компаунде до слоев коммутации на нижней стороне корпуса и последующее заполнение этих отверстий припойной композицией (рис. 4а) [9, 10]. Компания Stats Chip создает межуровневую коммутацию похожим способом, только вместо заполнения припоем в полученных с помощью лазера отверстиях формируют шарики (рис. 46) [9, 10]. Компания Infineon для создания межуровневых соединений использует процессы металлизации компаунда, в результате которых на стенках отверстий формируется слой меди, достаточный для обеспечения надежного электрического контакта. Такие межуровневые соединения носят название сквозных отверстий в инкапсулянте (TEV) – рис. 4в [9, 10]. Оригинальную

технологию формирования межуровневой коммутации под названием InFo (Integrated Fan-out) разработала компания TSMC. Межуровневая коммутация в данной технологии реализуется не с помощью металлизированных или заполненных припоем отверстий, а с помощью медных столбиковых выводов, называемых TIV (Through InFo Via) – рис. 4г [9, 11].

Сборка типа РоР обеспечивает меньшие размеры изделия, что позволяет разработчикам без особого труда выполнять требования по высоте изделий и применять широкий спектр сторонних кристаллов DRAM в одном корпусе с основной микросхемой. Учитывая меньшие габариты, пониженную мощность и более высокие характеристики сборок PoP [12], легко понять растущую популярность FO WLP.

Рис. 4. Различные варианты формирования межуровневой коммутации в трехмерных сборках на основе WLP-корпусов: отверстия в компаунде, заполненные припоем (а), отверстия со сформированными бампами (б), сквозные металлизированные отверстия в компаунде инкапсулянте (в), медные столбиковые выводы по технологии InFo (г) [9, 10, 11]

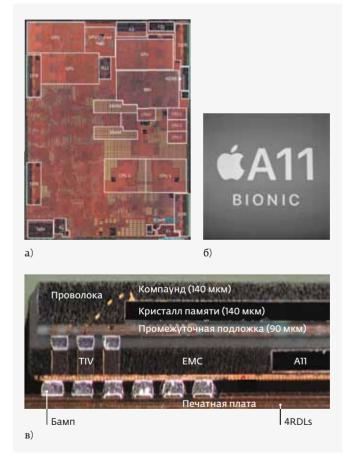

Смартфоны и беспроводные мультимедиа-устройства стали первыми крупными коммерческими сегментами, в разработке которых применили FO WLP, например в микропроцессорах мобильных телефонов iPhone компании Apple. Микропроцессоры Apple AlO, All, Al2 изготавливаются по InFo-технологии от компании TSMC (рис. 5) [13].

#### ПРЕИМУЩЕСТВА FO WLP

FO WLP имеет много преимуществ по сравнению с традиционными технологиями корпусирования:

- более высокую производительность;

- более короткие межсоединения позволяют снизить количество паразитных связей и уменьшить задержки;

- более короткие расстояния до теплоотвода уменьшают вероятность тепловых ударов и сопротивления;

- сниженное энергопотребление;

- улучшенные конструктивные параметры (габаритные размеры);

- имеет меньшую высоту и массу, чем традиционные 2,5D- и 3D-сборки;

- позволяет размещать большее количество элементов / компонентов по вертикали, уменьшая площадь посадочного места корпуса.

В то время как кремниевые 2,5D- и 3D-технологии конкурируют с FO WLP, многие в отрасли рассматривают их как параллельные технологии для разных рынков и различных задач применения. Так, например, FO WLP часто считают более подходящим решением для мобильных

Рис. 5. Использование высокоплотных микросборок WLP (технология InFo) в микропроцессоре Apple All: а – кристалл микропроцессора; б, в – компонент микропроцессора Apple All (вид сверху и фрагмент среза) [13]

устройств, радиочастотных изделий и автомобильной электроники, в то время как 2,5D- и 3D-микросборки на основе кремния с TSV-отверстиями лучше всего подходят для памяти, ПЛИС и графических/центральных процессоров.

#### ТЕХНОЛОГИИ FO WLP

Следующим шагом после решения использовать FO WLP является выбор конкретного способа изготовления, то есть технологии.

Первой коммерческой и доступной FO WLP технологией стала технология корпусирования кристаллов на уровне пластины с применением массива шариковых выводов eWLB от компании Infineon.

Процесс сборки микросхем непосредственно на кремниевой подложке в технологии eWLB не ограничен размерами кристаллов, что дает разработчикам гибкость в использовании практически неограниченного количества соединений между корпусом и промежуточной подложкой для обеспечения максимальной плотности. Компания Infineon решила лицензировать свой технологический маршрут eWLB, поэтому теперь он доступен у большинства ведущих поставщиков аутсорсинговых услуг по сборке и тестированию изделий микроэлектроники (OSAT).

Однако это привело к тому, что OSAT-компаниям очень трудно конкурировать между собой, когда все они применяют один и тот же технологический маршрут, ценообразование которого ограничено стоимостью лицензирования. В результате все крупные аутсорсинговые OSAT-компании поддерживают технологию корпусирования eWLB, но при этом часть из них также предоставляет альтернативные запатентованные процессы.

Таким образом, eWLB – далеко не единственная FO WLP технология на рынке. Группа из нескольких компаний организовала консорциум высокоплотных технологий FO WLP под руководством A\*Star (Сингапурская научно-исследовательская компания), в состав которой вошли компании Amkor, Nanium, STATS ChipPAC, NXP, GLOBALFOUNDRIES, Kulicke & Soffa, Applied Materials, Dipsol, JSR Micro, KLATencor, Kingyoup, Orbotech и ТОК [14]. Цель данного консорциума – исследование проблем, связанных как с технической реализацией, так и с оптимизацией стоимости производства высокоплотных корпусов, микросборок по FO WLP и поиском лучших производственных решений для быстрого внедрения данных технологий в электронной отрасли. За последние несколько лет консорциум разработал две высокоплотные технологии корпусирования: mold-first и RDL-first/chips-last.

Например, технология SWIFT (silicon wafer integrated fan-out technology) фирмы Amkor имеет ряд уникальных особенностей, нетипичных для традиционных корпусов интегральных схем, таких как использование диэлектриков на основе полимеров; использование нескольких типов кристаллов; применение кристаллов больших размеров; плотность межсоединений до 2 мкм на линию (недопустимо для SoC-изделий); межслойные соединения с шагом до 30 мкм; возможность использовать TMV (Through Mold Via – сквозные металлизированные отверстия в компаунде) или медные столбики (как в технологии TIV от TSMC в процессорах A10, 11). Недостаток данной технологии заключается в необходимости использовать дополнительный кремниевый компонент (например, кремниевый интерпозер, но без TSV-отверстий). Поскольку OSAT-компании не могут производить кремниевые компоненты, они вынуждены пользоваться

**Таблица 1.** Варианты технологий FO WLP от OSAT-компаний

| Компания/<br>технология<br>корпусирования | Минимальный<br>размер проводник/<br>зазор (мкм) | Особенности<br>технологии          | Область применения                                                                                                                                             |

|-------------------------------------------|-------------------------------------------------|------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Amkor/SLIM                                | <1 (до 0,4 включи-<br>тельно)                   | BEOL, химическая<br>полировка меди | Корпусирование отдельных кристаллов                                                                                                                            |

| Amkor/SWIFT                               | 2                                               | RDL                                | Микросистемы с двумя бескорпусными микросхемами внутри одного корпуса, процессоры для работы приложений и процессоры для работы беспроводной связи в смартфоне |

| SPIL/NTI                                  | 2                                               | RDL                                | Микросистемы с двумя бескорпусными микросхемами внутри одного корпуса, процессоры для работы приложений в смартфоне                                            |

| Xilinx/SLIT                               | 0,4/0,4<br>для трех слоев меди                  | Выборочное<br>удаление кремния     | Высоко- и среднепроизводительные устройства                                                                                                                    |

PADS Professional уже в базовой конфигурации содержит все инструменты, необходимые для качественного проектирования устройств с использованием высокоскоростных интерфейсов, и включает в себя:

- инструменты пред- и постгопологического анализа целостности сигналов:

- средства анализа и моделирования аналоговых и цифро-аналоговых схем;

- решение для осуществления теплового анализа.

#### Кроме того, доступны программные средства, позволяющие выполнять:

- анализ падений напряжения в цепях питания;

- расширенный DRC-скрининг с уникальным набором правил;

- анализ тайминга и целостности сигналов DDR;

- анализ поведения воздушного потока и теплопередачи для устройств со сложной геометрией:

- проектирование ВЧ-плат в условиях расширенных возможностей:

- проектирование гибко-жестких печатных плат;

- оптимизацию ПЛИС:

- автоматическую подстройку проводников высокоскоростных сигналов и использование расширенного набора электрических ограничений.

Наведите на QR код - получите скидку на PADS Professional

услугами сторонних производителей. Варианты наиболее известных FO WLP технологий, предлагаемые OSAT-компаниями [15], перечислены в табл. 1.

Фабрики по производству микросхем также обратили внимание на рост популярности решений на основе технологий FO WLP. Компания TSMC, вышедшая на рынок со своей технологией InFO WLP [16], сертифицировала ее для корпусирования кремниевых кристаллов собственного производства для различных размеров корпусов:  $8 \times 8 \text{ мм}^2$  (позволяет монтировать один или несколько кристаллов с количеством входов / выходов до 600),  $15 \times 15 \text{ мм}^2$ (поддерживает до 2000 входов/выходов) и  $30 \times 30 \text{ мм}^2$ (поддерживает до 3600 входов / выходов).

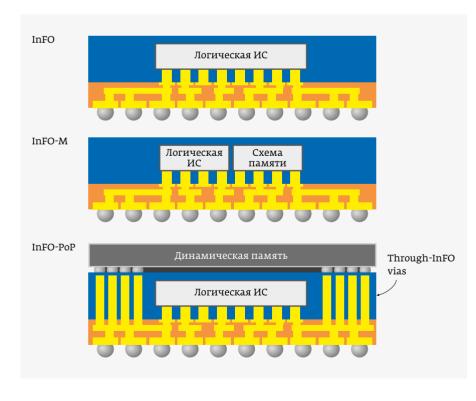

В одном из вариантов технологии InFO, известном под названием integrated fan-out package-on-package (InFO-PoP), кристалл DRAM монтируется над FO WLP с использованием технологии TPV (в TSMC называют ее «переходные отверстия», through-InFO или TIV) (рис. 6). Другой вариант технологии, называемый InFO-M, поддерживает размещение одновременно нескольких кристаллов.

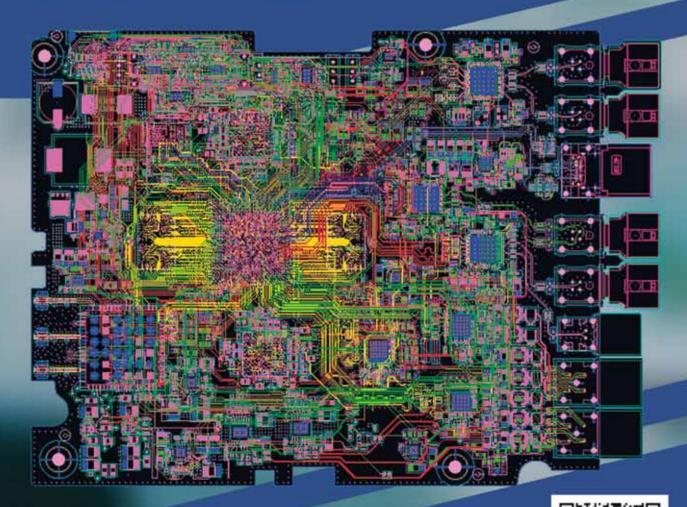

Компания Intel Custom Foundry недавно представила собственную технологию под названием EMIB (embedded multi-die interconnect bridge) как новый экономически выгодный подход к сборке гетерогенных микросхем с высокой плотностью межсоединений (рис. 7) [17].

Несмотря на то, что данная технология не является прямым аналогом FO WLP, она позволяет избежать использования TSV-отверстий за счет замены больших и сложных интерпозеров на «кремниевые мосты» (небольшие элементы с высокой плотностью коммутации, выполненные из кремния), что позволяет создавать межсоединения между интерфейсами кристаллов с малым шагом. Существует также информация, что Intel разрабатывает полноценную FO WLP технологию.

С включением в состав консорциума фабрик по производству микросхем, у разработчиков корпусов появилась новая тема для обсуждения: компании OSAT против фабрик по производству микросхем. Основные преимущества, предлагаемые фабриками: более быстрое время изготовления за счет совместного использования производственных линий; единое место для связи и предоставления услуг; специализированное оборудование; десятки лет опыта и предоставление полного набора комплекта библиотек для разработчиков. Например, компания TSMC, занимаясь внедрением технологии InFO в серийном производстве [18], производила отладку и проверку технологических процессов InFO с целью получения на выходе готового продукта со стопроцентной гарантией с вариантами исполнений для конкретных областей применения. Вполне вероятно, что компании OSAT будут следовать по примеру фабрик в данной области, вкладывая больше ресурсов на установление и сертификацию их производственных норм и допусков.

> Сравнение процессов фабрик FO WLP с процессами компаний OSAT позволяет увидеть преимущества и недостатки каждого подхода (табл. 2).

> Очевидно, главное преимущество для компаний разработчиков – это возможность делать и согласовывать все этапы технологического процесса в одном месте. Фабрики имеют большой опыт в создании PDK (Process Design Kit – комплект средств проектирования) для сложных ИС. Теперь они делятся своими знаниями и опытом с ведущими мировыми компаниями по разработке корпусов. Но, помимо большого опыта и исторически долгих отношений с EDA-компаниями, они также имеют преимущество в виде уникальных знаний по работе с кристаллами и их корпусами. Все это облегчает разработчикам получение доступа к большому количеству всевозможной информации об ИС и корпусах, чем в случае работы с несколькими участниками рынка.

Рис. 6. Варианты межсоединений в системе в корпусе по технологии InFO компании TSMC

Таблица 2. Сравнение производственных процессов FO WLP на фабриках с процессами компаний OSAT

#### Фабрики по производству полупроводниковых микросхем

#### Единый процесс:

- все кристаллы привязаны к одной фабрике;

- большая пропускная способность;

- единое место обмена информацией

#### Компании типа OSAT

Цепочка последовательных процессов:

- возможность объединения в одной сборке кристаллов, выполненных по различным технологиям и от нескольких производителей;

- возможны задержки из-за транспортировки;

- обмен информации в нескольких местах;

- непонятно кто отвечает за проблемы с выходом годных изделий

Специальные библиотеки проектирования (PDK) и методы разработки:

- сертифицированные изделия и технологические маршруты;

- жесткие требования к соблюдению PDK

Исторически отсутствуют жесткие требования к соблюдению PDK или его поддержке

Контролируемая стоимость и масштаб производства

Чаще всего имеет низкую стоимость

Так, например, собрать воедино общие решения по проблеме минимизации паразитических связей, возникающих вследствие взаимного влияния кристалла и проводников корпуса, для OSAT-компаний является трудной задачей, поскольку OSAT обладают

а)

Встроенные кремниевые элементы коммутации

**Puc. 7.** Микросборка по технологии EMIB от компании Intel: а - вид сверху, б - вид в разрезе

подробными знаниями только о корпусе. Кроме того, они не только плохо информированы о структуре кристалла, но и имеют ряд юридических ограничений на распространение имеющейся информации другим поставщикам ИС.

OSAT-компании имеют возможность создавать сборки на основе кристаллов от нескольких производителей, что обычно не доступно для фабрик. Так, например, трудно представить, что кристалл, произведенный в Samsung, можно отправить на сборку по технологии InFO в TSMC. С одной стороны, ограничиваясь одним заводом-изготовителем, отпадает необходимость в транспортировке кристаллов на дальние расстояния, при этом экономится время и появляется гарантия того, что вся необходимая информация в процессе работы будет доступна. С другой стороны, при выборе OSAT открывается широкий спектр возможностей

для разработок, при этом увеличиваются трудозатраты разработчиков корпусов на обеспечение надежности совместной работы всех элементов/компонентов (и отладки в случае ошибок) при работе с посредниками. Этот выбор может существенно повлиять на стоимость корпуса FO WLP в зависимости от предложений изготовителей кристаллов.

Для компаний, разрабатывающих корпуса, такая вариативность и персонализация означает постоянно увеличивающийся выбор FO WLP решений. Определить лучшее предложение на основе установленных разработчиком требований может быть не так просто. Помимо цены и производителя, предложения обычно оценивают с точки зрения минимизации объема, занимаемого корпусом в изделии, и улучшения электрических параметров. Объем корпуса WLP определяется минимально возможной высотой и площадью посадочного места, минимальной плотностью размещения в соответствии с минимальным расстоянием между кристаллами и минимальной шириной проводника, а также пространством, соединяющим RDL-слои и BGA-выводы.

Подводя итоги, вне зависимости от того, что выберет разработчик корпуса, микросборки – фабрику или OSAT, технология FO WLP будет доступна. FO WLP позволяет использовать новую методологию разработки с перечнем ключевых преимуществ, которой с удовольствием пользуются разработчики корпусов. Ожидается, что область применения FO WLP будет расширяться в течение нескольких последующих лет, совместно с расширением области 3D-технологий сборки ИС.

Во второй части статьи будут рассмотрены вопросы проектирования и верификации корпусов и микросборок по технологии FO WLP средствами САПР компании Mentor Graphics.

#### ЛИТЕРАТУРА

- Burakov M. M., Vertyanov D. V., Boyko A. N., Sosnovsky A.V. Investigation of TSV metallization for MEMS encapsulation technology. 2018 // ElConRus Conference IEEE. PP. 1599-1603. DOI: 10.1109/EIConRus.2018.8317411.

- Вертянов Д., Евстафьев С., Виклунд П., Сидоренко В. Технологии внутреннего монтажа бескорпусных элементов и особенности проектирования микросистем со встроенными кристаллами. Часть 2 // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2020. № 7 (00198). C. 144-148. DOI: 10.22184/1992-4178.2020.198.7.144.148.

- Вертянов Д., Евстафьев С., Виклунд П., Сидоренко В. Технологии внутреннего монтажа бескорпусных элементов и особенности проектирования микросистем со встроенными кристаллами. Часть 1 // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2020. № 6 (00197). С. 96-102. DOI: 10.22184/1992-4178.2020.197.6.96.102.

- 4. Вертянов Д. В., Сидоренко В. Н., Тимошенков С.П., Ковалев А.А. Перспективные конструктивно-технологические решения для производства «систем в корпусе» // Технологии в электронной промышленности. 2019. № 4. C. 60-64.

- Kumar S., Shoo F., Trivedi V. Status of the advanced packaging industry 2020 // Market & technology report. July 2020. Yole developpement. 2020. 5 p.

- Lapedus M. Fan-Out Wars Begin [Электронный ресурс] / Semiconductor Engineering, 2018. URL: https://semiengineering.com/fan-out-wars-begin/ (дата обращения 20.04.2021).

- Lau J. H. Fan-Out Wafer Level Packaging/Springer, 2018. PP. 5-31.

- Germering H.H., Erlangen T.M., Munich B.V. Transfer wafer level packaging. Заявитель и патентообладатель Infineon Technologies AG, опубл. 27.04.2004.

- Вертянов Д.В., Сидоренко В.Н., Бураков М.М., Беляков И.А. Технологии формирования межуровневой коммутации для изготовления трехмерных микросборок // НАНОИНДУСТРИЯ. 2019. № S (82). С. 515-526. DOI: 10.22184/NanoRus. 2019.12.89.515.526.

- 10. Lau John H. 3D IC Packaging 3D IC Integration: A CPMT Distinguish Lecture // San Diego Chapter. 2015.

- 11. **Lanzone R.** Amkor Technology Advanced Package Solutions // SVP Engineering Solutions: Confab. Las Vegas. 2013.

- 12. **Liu C.C. et al.** High-performance integrated fan-out wafer level packaging (InFO-WLP): Technology and system integration, Electron Devices Meeting (IEDM), 2012 IEEE International, San Francisco, CA, 2012, PP, 14.1.1–14.1.4. DOI: 10.1109/IEDM.2012.6479039.

- 13. **Lau H.J.** Fan-Out Wafer-Level Packaging for 3D IC Heterogeneous Integration // IEEE/EPS Chapter Lecture in the Silicon Valley Are. 2018. 79 p.

- 14. Fan-Out Wafer-Level Packaging (FOWLP) Consortium, https://www.a-star.edu.sg/ime/INDUSTRY/INDUSTRY-CONSORTIA/Fan-Out-Wafer-Level-Packaging-FOWLP-Consortium.aspx.

- 15. TechSearch International, Inc., "The Future of Packaging and Assembly Technology" presentation at Central Texas Electronics Association, 2016. http://www.smta.org/chapters/files/ Central-Texas\_CTEAVardaman2016.pdf.

- 16. Letter to Shareholders // Taiwan Semiconductor Manufacturing Co Ltd, 2015. http://www.tsmc.com/ download/ir/annualReports/2015/english/pdf/e\_1\_1.pdf

- 17. Intel Custom Foundry. «Embedded Multi-die Interconnect Bridge,» Intel Corporation, http://www.intel.com/content/ www/us/en/foundry/emib.html.

- 18. Taiwan Semiconductor Manufacturing Co Ltd Earnings Call. October 15. 2015. http://www.tsmc.com/uploadfile/ir/ quarterly/2015/3C2bO/E/TSMC 3Q15 transcript.pdf.

# SEMIEXPO RUSSIA

**МЕЖДУНАРОДНАЯ ВЫСТАВКА**

ТЕХНОЛОГИИ | МАТЕРИАЛЫ | ОБОРУДОВАНИЕ В ОБЛАСТИ МИКРОЭЛЕКТРОНИКИ

24 – 25 августа 2021

ЦВК «Экспоцентр», Москва

## ОТРАСЛЕВЫЕ ОБЗОРЫ

Конкурентный анализ рынка и стандарты, маркетинговые исследовательские программы

# **ИННОВАЦИИ**

Новые разработки, международные проекты и локальные компетенции

# СОТРУДНИЧЕСТВО

Стратегические инициативы, международные институты развития и ведущие мировые ассоциации

#### **БИЗНЕС**

Локальные партнеры, новые заказчики и поставщики, старт-апы и консорциумы

Организатор: Business Media Russia

+7 495 649 69 11

Подробная информация и бесплатный билет

www.semiexpo.ru

@semiexporussia