## Обзор ПЛИС китайских производителей

А. Строгонов, д. т.н. $^{1}$ , П. Городков $^{2}$

УДК 621.3.049.774 | ВАК 05.27.01

Несмотря на практически абсолютную монополию на рынке ПЛИС американских компаний, появление нескольких серий высокопроизводительных устройств китайского производства свидетельствует о серьезных достижениях китайской электронной отрасли в области проектирования ПЛИС и разработки программного обеспечения. Кроме ПЛИС с независимыми правами интеллектуальной собственности, китайские компании предлагают соответствующие экосистемы, которые включают инструменты проектирования и библиотеки ІР-блоков. Китайские разработчики активно встраивают в свои ПЛИС различные микропроцессорные ядра, аналоговые блоки и разнообразную периферию. В статье представлен обзор ПЛИС от ведущих китайских производителей, их особенности, инструменты разработки и области применения.

атентная защита двух ведущих американских компаний, Xilinx и Intel (Altera), продукция которых занимает до 90% мирового рынка ПЛИС, сформировала сильный рыночный барьер для развивающихся стартапов. В этих условиях китайские производители ПЛИС проводят собственные исследования и разработки, чтобы преодолеть патентные барьеры, решая, таким образом, проблему создания ПЛИС с нуля.

В последние годы ПЛИС стали одним из основных элементов стратегического продукта China Strong Core. Ведущие китайские производители ПЛИС, такие как Ziguang Tongchuang, Fudan Microelectronics, China Microelectronics, 58 Institute of China Electronics, 772 Institute of Aerospace, Jingwei Yage, Gowin Semiconductor, Shanghai Anlu, Xi'an Zhiduo Crystal, Shanghai Aogexin, еще не вышли на основной европейский рынок. Ограничения прав интеллектуальной собственности со стороны мировых вендоров не позволяют китайским компаниям выпускать достаточно широкий ассортимент функциональных аналогов ПЛИС от ведущих зарубежных компаний.

Компания Shenzhen Ziguang Tongchuang Electronics – единственный китайский производитель, отвечающий требованиям рынка ПЛИС к приложениям высокого, среднего и низкого уровней. В 2015 году эта дочерняя компания группы Ziquanq Group выпустила серию высокопроизводительных ПЛИС Titan и набор программных инструментов

вспомогательных средств разработки с полностью независимыми правами интеллектуальной собственности. А в 2016 году ПЛИС PGTI80H прошла все системные проверки таких производителей радиоэлектронного оборудования, как ZTE и Xinhua Three Communications.

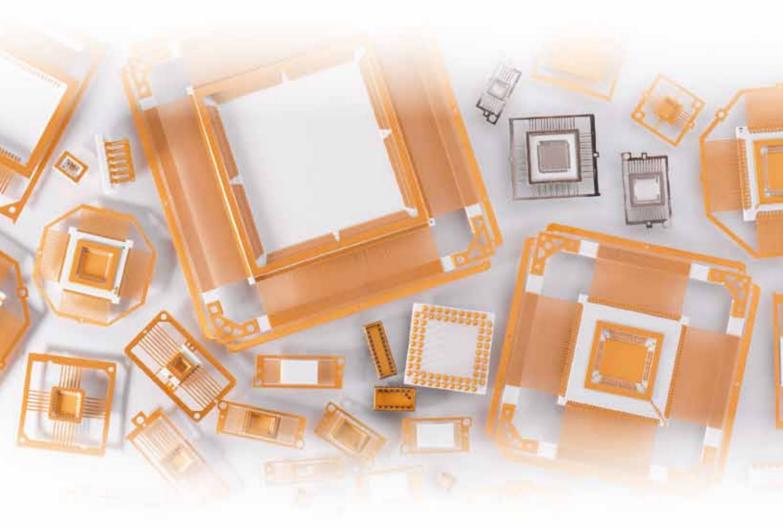

Shenzhen Ziguang Tongchuang Electronics предлагает три основные серии ПЛИС: Titan, Logos и Compa (рис. 1). В составе ПЛИС FPGA серии Titan (PGT180H), выпускаемой по 40-нм КМОП-технологии, 174019 LUT4, 217524 триггеров DFF, SERDES, интерфейсы DDR3 800 Мбит/с, LVDS и PCIe Gen2x4. Серия ПЛИС FPGA Logos (PGL22G), также выпускаемая по 40-нм КМОП-технологии, содержит от 12К до 100К LUT5/6, ЦОС-блоки, АЦП, SERDES, интерфейсы DDR3, LVDS, MIPI, а также модуль 256-бит AES. Серия Compa представляет собой ПЛИС CPLD, выпускаемые по 55-нм флеш-технологии (eFlash), и содержит от 1К до 10К LUT4, RAM, ФАПЧ, интерфейсы MIPI, LVDS, I2C, SPI.

Рис. 1. Высокопроизводительные ПЛИС Ziguang Tongchuang Electronics: а - ПЛИС (FPGA) серии Titan; б - ПЛИС (FPGA) серии Logos; в - ПЛИС (CPLD) серии Сотра

Воронежский государственный технический университет, профессор кафедры полупроводниковой электроники и наноэлектроники, тел. +7 4732 43-76-95, andreistrogonov@mail.ru.

Воронежский государственный технический университет, аспирант кафедры полупроводниковой электроники и наноэлектроники, тел. +7 4732 43-76-95, gorodkoff@gmail.com.

**Рис. 2.** Отладочная плата производства компании ALINX на ПЛИС PGL12G

Для разработки проектов на ПЛИС и их конфигурирования используется собственная САПР Pango Design Suite и отладочные платы компании ALINX Electronic Technology (Shanghai) Co., Ltd. (рис. 2).

В планах Ziguang Group было приобретение американской компании Lattice, занимающейся разработкой и производством ПЛИС, однако после рассмотрения Комитетом по иностранным инвестициям в США (CFIUS) и противодействия со стороны администрации США сделка закончилась неудачей.

**Tsinghua Unigroup** — крупный холдинг, специализирующийся на производстве электронных компонентов и оборудования. Он является третьим по величине разработчиком имеющихся в продаже БИС для мобильных телефонов в мире, на долю предприятия приходится 20% мирового рынка SIM-карт. Холдинг обладает 30 тыс. патентами, из них 8 тыс. связано с ИС. В состав холдинга Tsinghua Unigroup входит ряд крупных ИТ-компаний по всему миру, в том числе Unisoc (Spreadtrum Communications) и RDA Microelectronics.

Unisoc входит в число крупнейших разработчиков БИС в Китае. В 2021 году Unisoc представила первый в мире 6-нм процессор по технологии EUV (Extreme ultraviolet lithography, фотолитография в экстремальном ультрафиолете) (серия Tanggula T770) с максимальной частотой 2,5 ГГц для смартфонов. Сегодня Unisoc конкурирует с американской Qualcomm и тайваньской MediaTek на звание крупнейшего производителя процессоров в мире.

На официальном сайте Tsinghua Unigroup не указано, что компания занимается разработкой и производством ПЛИС, тем не менее, в зарубежных интернет-изданиях отмечается, что холдинг интересуется разработками в области перспективных высокоинтегрированных ПЛИС.

**Рис. 3.** ПЛИС серии СМЕ-С1 компании Jingwei Yage

Компания **Jingwei Yage** была основана в 2003 году в Кремниевой долине (США), а в 2005 году переехала в Пекин и, в основном, занималась разработкой ПЛИС. За прошедшие годы Jingwei Yage разработала несколько серий ПЛИС и сегодня планирует перейти от рынка недорогих ПЛИС к устройствам среднего и высокого класса. ПЛИС серии СМЕ-СІ емкостью до 20 млн вентилей способны частично заменить ПЛИС американских компаний на рынке младшего класса (рис. 3).

ПЛИС Jingwei Yage представлены несколькими сериями. Высокопроизводительные серии CME-M7 Huashan и CME-M5 Jinshan можно рассматривать как системына-кристалле (ПЛИС СНК). Серия CME-M7 Huashan выполнена по технологии КМОП СОЗУ. В своем составе содержит 32-разрядное RISC процессорное ядро ARM Cortex-M3, 2-канальный 12-разрядный АЦП со скоростью преобразования 1 Мвыб / с, встроенную блочную память EMB5K, ЦОС-блоки. Выпускаются также серии CME-M1 Hengshan, CME-M0 и малопотребляющая серия CME-HR03.

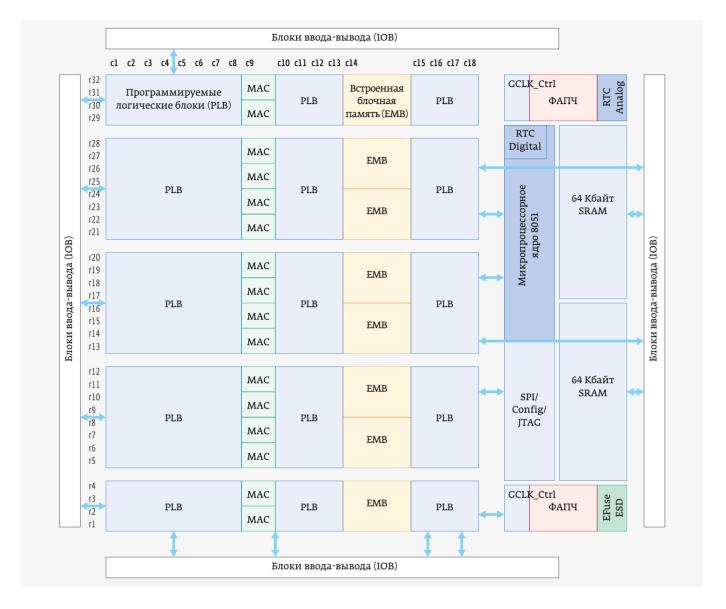

В настоящее время на рынке доступны высокопроизводительные (до 250 МГц) ПЛИС серии СМЕ-М5 (рис. 4) с макетной платой (рис. 5) и загрузчиком. Отличительной особенностью ПЛИС СМЕ-М5 являются ЦОС-блоки для МАС-операций с размерностью операндов 18 × 18 (16 шт.) или 12 × 9 (32 шт.) и микропроцессорное ядро 8051 с рабочей частотой до 200 МГц.

На кристалле ПЛИС серии СМЕ-М5 располагаются следующие функциональные блоки (см. рис. 4, на примере М5СО6N3): программируемые логические блоки (PLB), состоящие из 6144 4-LUT, 4096 триггеров DFF; встроенная блочная память СОЗУ (32 ЕМВ емкостью 4,5 Кбит), ЦОС-блоки (МАС, 16 шт.), аналоговые блоки фазовой автоподстройки частоты (ФАПЧ, 2 шт.), блоки ввода-вывода (IОВ), микропроцессорное ядро 8051 и 128 Кбит СОЗУ (SRAM) для его поддержки, цифровой и аналоговый блок часов реального времени (digital RTC и analog RTC), блок защиты от электростатических разрядов EFuse ESD, блок конфигурирования ПЛИС с помощью интерфейсов SPI / JTAG (SPI config / JTAG).

Рис. 4. Архитектура ПЛИС СМЕ-М5

Рис. 5. Макетная плата для отладки на базе ПЛИС СМЕ-М5

В дополнение к загрузке, отслеживанию и отладке ПЛИС, модуль USB\_JTAG также поддерживает онлайнотладку встроенного аппаратного ядра 8051 в среде отладки Keil, реализуя такие функции, как точка разрыва, одношаговое отслеживание, наблюдение блока памяти и др. Для ПЛИС СМЕ-М7 улучшена отладка внутреннего ядра Cortex-M3.

Поскольку ПЛИС Jingwei Yage не совместимы по выводам с американскими ПЛИС, то требуется техническая поддержка в течение всего жизненного цикла изделий, что снижает востребованность этих устройств на рынке. В мае 2016 года компания Jingwei Yage столкнулась с трудностями в своей деятельности и обанкротилась. В июне 2017 года оставшиеся сотрудники Jingwei Yage основали компанию Jingwei Qili (Qili Technology). Jingwei Qili в настоящее время использует собственные

**Рис. 6.** ПЛИС серии JFM7 от Fudan Microelectronics

ПЛИС для реализации приложений искусственного интеллекта. В дополнение к продолжающимся продажам собственных ПЛИС, разрабатываются ПЛИС (AiPGA) нового поколения,

БИС НРА для гетерогенных вычислений и встроенные программируемые IP-ядра eFPGA для приложений искусственного интеллекта.

Fudan Microelectronics Group (Фуданьский институт микроэлектроники) — независимая научно-исследовательская организация, занимающаяся исследованиями в области ПЛИС, а также разработкой и производством энергонезависимой памяти, такой как SPI NAND флеш-память и EEPROM.

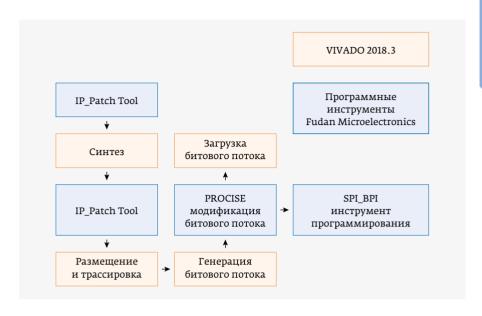

Fudan Microelectronics представила радиационностойкую ПЛИС серии JFM7 (рис. 6), которая предназначена для применения в аэрокосмической отрасли, коммуникационном оборудовании и других областях. ПЛИС этой серии имеют увеличенную логическую емкость и быстродействие по сравнению с предыдущей серией JFM4. ПЛИС JFM7 выпускаются по 28-нм технологическому процессу, являются функциональными аналогами седьмой серии Kintex XC7K325T и Virtex-7 XC7VX690T от Xilinx и совместимы с ними по выводам. Тем не менее, необходимо использовать программные заплатки на IP-блоки (IP\_patch), на битовый поток при конфигурировании ПЛИС (bit\_patch) и на прожиг (burn\_patch), которые должны быть включены в маршрут проектирования в случае использования САПР Vivado Xilinx.

Между JFM7K325T и XC7K325T существует несколько различий, например в схеме высокоскоростного трансивера. Параметр при конфигурации IP-ядра TXOUT\_DIV/RXOUT\_DIV для ПЛИС JFM7K325T может быть установлен только в 1, а не в 2, 4, 8 или 16, как для ПЛИС XC7K325T. Кроме того, существуют различия в конфигурации параметра RX\_DFE\_KL\_CFG2 блока CTLE (широкополосные каскады усиления): для XC7K325T этот параметр

**Puc. 7.** Интеграция программных инструментов Procise в маршрут проектирования ПЛИС с использованием CAПР Vivado Xilinx

по умолчанию равен 1, тогда как для JFM7K325T он должен быть настроен на 0. Поэтому IP-ядро PCIe CAПР Vivado не работает должным образом с ПЛИС JFM7K325T и требуется IP\_patch. Все существующие отличия указаны в руководстве пользователю на ПЛИС JFM7K325T на китайском и английском языках.

Для программирования ПЛИС JFM7K325T используется САПР Procise собственной разработки (рис. 7). САПР Procise представляет собой новое поколение программных средств разработки с многочисленными IP-ресурсами и поддерживает ПЛИС с количеством вентилей более миллиона.

Особенности ПЛИС JFM7K325T: число логических модулей 326080; число секций 50950; распределенная память 4000 Кбит; тактовая частота 600 МГц; объем блочной памяти ОЗУ 16020 Кбит; 840 ЦОС-блоков (умножитель с размерностью операндов 25×8, 48-разрядное АЛУ, 25-разрядный пресумматор, гибкая конвейеризация); 16 приемо-передатчиков GTX; 12-разрядный АЦП на 1 Мвыб/с; коммуникационные протоколы PCI Express VI.1/2.0, 10GBASE-R, Interlaken, XAUI, RXAUI, CAUI, CPRI, OBSAI, OC-48/192, OUT-1/2/3/4, SRIO, SATA, SDI. Официальный поставщик ПЛИС Fudan в РФ ООО «Феникс Электроникс».

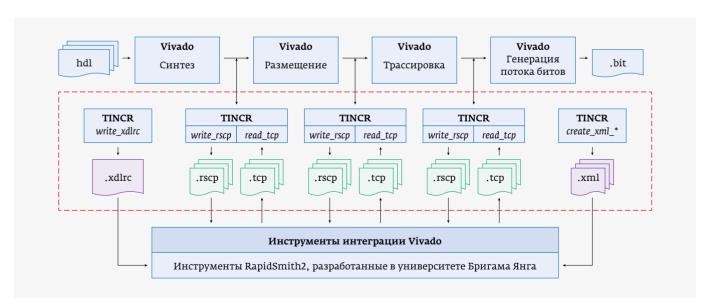

Идея интеграции программных инструментов Procise в маршрут проектирования ПЛИС с использованием САПР Vivado Xilinx не нова. Нечто подобное представляет ПО с открытым программным кодом RapidSmith частного университета имени Бригама Янга США (для ПЛИС Xilinx ранних версий, которые поддерживались в ISE; RapidSmith зависим от языка разработки Xilinx (XDL), поддержка которого была прекращена в Vivado).

RapidSmith2 используется для исследования современных индустриальных ПЛИС СнК Xilinx, доступных в Vivado (рис. 8). ПО RapidSmith2 позволяет экспортировать дизайн проекта из Vivado, изменять его на более мощном языке Java, чем Tcl, а затем импортировать обратно. Tcl-интерфейс используется в САПР Xilinx Vivado. Теоретически, он предоставляет полный функционал, необходимый для создания собственных алгоритмов САПР ПЛИС: размещение, трассировка и т.д. Для ПО RapidSmith2 был разработан инструмент Tincr, который представляет собой набор Tcl-библиотек, написанных для САПР Xilinx Vivado.

Основанная в 1958 году **Китайская корпорация электронных технологий (58-й научно-исследовательский институт, China Electronics Technology Group Corporation, CETC58)** является ключевым национальным научно-исследовательским институтом, занимающимся исследованиями, разработками и производством СБИС. Он специализируется на разработке и производстве микроэлектронных устройств для авиационной, военной и космической областей. Корпорация выпускает следующие типы компонентов космического применения: ПЛИС, АЦП/ЦАП, контролеры шин, ИС памяти и др.

Холдинг «Росэлектроника» и СЕТС58 рассматривали возможность совместного производства полупроводниковых приборов. Соответствующее соглашение стороны заключили в ходе международного авиасалона Airshow China 2016 в Чжухае. Соглашение предусматривает возможность сотрудничества в режиме foundry, при котором «Росэлектроника» берет на себя разработку и проектирование изделий, а СЕТС58 обеспечивает их производство в заданном объеме. В 2017 году СЕТС58 становится резидентом индустриального парка «Великий камень» в Беларуси, офис которой находится в Минске. ООО «Феникс

Электроникс» является официальным представителем СЕТС58 на территории Российской Федерации.

СЕТС58 разработал радиационно-стойкую ПЛИС JRT54SX72S на основе технологии Antifuse. Основные характеристики ПЛИС JRT54SX72S: количество вентилей 108 тыс.; напряжение питания 3,3 или 5 В; тактовая частота 150 МГц. ПЛИС является функциональным аналогом RT54SX72S производства Actel (Microsemi) и совместима с ней по выводам.

Компания Gowin Semiconductor (Guangdong Gowin Semiconductor Technology), основанная в январе 2014 года, занимается исследованиями и разработкой ПЛИС СНК с независимыми правами интеллектуальной собственности. Компания выпускает две серии ПЛИС: Little Bee и Arora. ПЛИС серии Arora разработаны с использованием 55-нм технологического процесса СОЗУ фабрики TSMC. В серию Arora входит три типа ПЛИС: GW2A, GW2AN и GW2ANR.

Серия LittleBee представляет собой низковольтные, малопотребляющие энергонезависимые ПЛИС, созданные по 55-нм процессу флеш-технологии. ПЛИС серии GWIN поддерживает новые интерфейсы MIPI I3C и MIPI D-PHY для сопряжения датчиков (например, видеокамер и дисплеев) и других БИС. В ПЛИС можно интегрировать микропроцессорное ядро Arm Cortex-M3 и SAR АЦП (для ПЛИС GWINS-2C) с поддержкой операционных систем реального времени (ОСРВ) uCOSIII (коммерческая) и FreeRTOS (бесплатная).

ПЛИС GWINSE и GWINSER предназначены для ответственных применений. В ПЛИС GWINSR встроены 32-разрядное процессорное ядро Cortex-M3 и 12-разрядный SAR АЦП. ПЛИС GWINZ отличается низким потреблением и содержит встроенную флеш-память. В ПЛИС

Рис. 8. Маршрут интеграции программных инструментов RapidSmith2 в САПР Xilinx Vivado

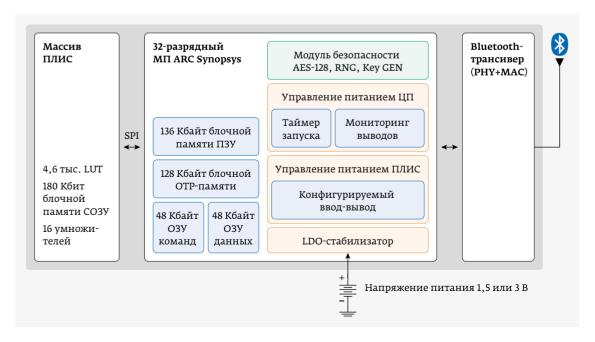

GWINRF встроено процессорное ядро ARC и интерфейс Bluetooth 5.0.

ПЛИС CHK GWINRF содержит аппаратные блоки: Bluetooth-трансивер, 32-разрядный микропроцессор с RISC-архитектурой с низким энергопотреблением Synopsys ARC (Argonaut RISC Core), менеджеры управления питанием ПЛИС и микропроцессорного ядра (power manager) и LDO-стабилизатор (рис. 9).

В своих разработках компания Gowin Semiconductor использует архитектуру компании Arm Holdings и программное обеспечение Synopsys в собственной САПР Gowin для RTL-синтеза в уникальный базис ПЛИС. Синтезатор Synplify Pro от Synopsys используется совместно с синтезатором Gowin Synthesis собственной разработки. Для этапов размещения и трассировки используются собственные программные инструменты.

Компания **Shanghai Anlu Information Technology** была основана в 2011 году с целью разработки ПЛИС СНК, а также связанных с ними инструментов разработки программного обеспечения. В 2015 году Anlu Technology выпустила свое первое поколение FPGA AL3-10 и разработала еще несколько изделий: ПЛИС CPLD серии Elf, серию Eagle (Falcon), недорогую FPGA Phoenix. В октябре 2017 года Anlu Technology выпустила серию высокопроизводительных ПЛИС с низким энергопотреблением второго поколения ELF2 (рис. 10) по 55-нм технологическому процессу. Anlu обладает полными правами интеллектуальной собственности на программное и аппаратное обеспечение.

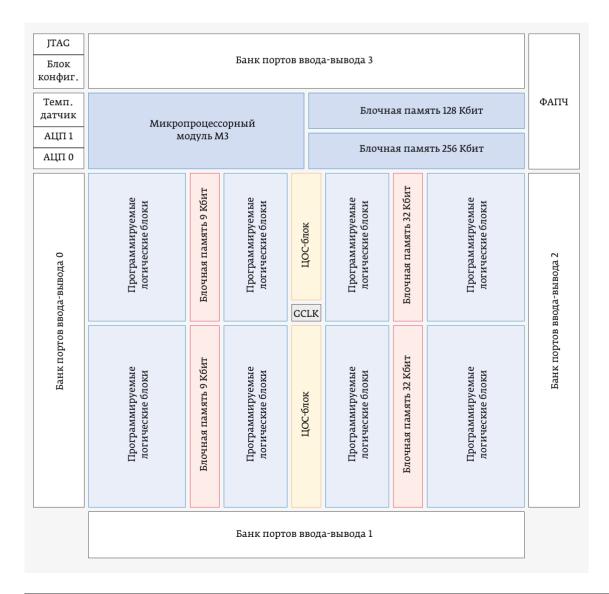

В серии ELF2 предлагается два типа устройств: L (без микропроцессорного ядра) и М (микропроцессорное ядро МЗ, АЦП последовательного приближения с частотой дискретизации 1 МГц). Серия содержит: от 1500 до 4480

LUT4/5; от 1500 до 4480 триггеров DFF; распределенную память до 35 Кбит; блочную память типа 9К, 32К, 256К до 700 Кбит; от 8 до 15 ЦОС-блоков; ФАПЧ; флеш-память 4 Мбит. ПЛИС поддерживают несимметричные входывыходы стандартов LVTTL, LVCMOS (3,3/2,5/1,8/1,5/1,2 В), PCI, SSTL 3,3 и 2,5 В (класс І и ІІ), SSTL 1,8 и 1,5 В (класс І), НSTL 1,8 и 1,5 В (класс І); дифференциальные входывыходы стандартов LVDS, Bus-LVDS, MLVDS, RSDS, LVPECL; интерфейсы DDR: DDRx1, DDRx2, MIPI HS/LP IO. Серия обеспечивает 128-битное шифрование данных AES.

Компания Xi'an Zhiduojing Microelectronics была основана в ноябре 2012 года и стремится стать крупнейшим в Китае поставщиком FPGA и CPLD, а также приложений для ПЛИС. На сайте www.isilicontek.com представлены три серии ПЛИС: Seagull 1000 (CPLD, макроячейки), Sealion 2000 (LUT4) и Seal 5000 (LUT6/5), САПР и отладочные платы. В 2017 году Zhiduojing Microelectronics анонсировала собственную платформу НqFpgaTM RTL-to-FPGA для полнофункциональной реализации ПЛИС.

Серия ПЛИС Sealion 2000 производится по 55-нм технологическому процессу с низким энергопотреблением. ПЛИС этой серии содержат высокопроизводительный программируемый логический блок на основе LUT4 (табл. 1). До 98% логических ресурсов LUT4 могут быть использованы при синтезе проекта в базис ПЛИС. Оптимизирована производительность режимов работы КЛБ, например, арифметические режимы могут быть использованы для реализации сумматоров, счетчиков, аккумуляторов и компараторов.

В ПЛИС Sealion 2000 встроен аппаратный ЦОС-блок для приложений с интенсивной обработкой данных. Предусмотрена встроенная флеш-память для хранения конфигурации ПЛИС (только для SL2E-5E), реализована

Рис. 9.

Архитектура

ПЛИС СНК

GWINRF

Таблица 1. Ресурсы ПЛИС серии Sealion 2000

| Ресурсы ПЛИС                                      | SL2E-5E | SL2E-7V | SL2E-12E |

|---------------------------------------------------|---------|---------|----------|

| Количество LUT                                    | 5 0 4 0 | 6864    | 12032    |

| Количество DFF                                    | 5 0 4 9 | 6864    | 12032    |

| Количество секций (LUT: DFF=1:1)                  | 2 5 2 0 | 3 432   | 6016     |

| Количество КЛБ                                    | 630     | 858     | 1504     |

| Емкость встроенной флеш-памяти, Кбит              | 512     | -       | -        |

| Максимально доступная распределенная память, Кбит | 40      | 54      | 95       |

| Емкость встроенной памяти, Кбит                   | 108     | 240     | 432      |

| Количество блоков памяти СОЗУ емкостью 9 Кбит     | 12      | 26      | 48       |

| Количество аппаратных умножителей                 | 16      | -       | 20       |

| Количество блоков PLL+DLL общего применения       | 2+2     | -       | 2+2      |

**Рис. 10.**Архитектура

ПЛИС СНК

Anlu ELF2M4500

поддержка распределенной и встроенной памяти ПЛИС. Максимальная частота работы ПЛИС составляет 200 МГц. Может быть предоставлено до 16 глобальных синхросигналов, из которых 8 могут быть мультиплексированы в сеть с большим разветвлением. Предусмотрено до 12 выделенных входных контактов синхронизации. LVDS-интерфейс может обеспечивать максимальную скорость передачи данных до 840 Мбит/с, скорость приема – 875 Мбит/с. ПЛИС оснащена интерфейсом DDR2 SDRAM (400 Мбит/с). Напряжения питания портов ввода-вывода: 3,3/2,5/1,8/1,5/1,2 В, интерфейс МІРІ обеспечивает скорость до 1,2 Гбит/с. Стандарты ввода-вывода включают: LVTTL, LVCMOS, SSTL, HSTL, PCI и LVDS, SSTL, HSTL, LVPECL, BLVDS, мини-LVDS, RSDS (дифференциальный).

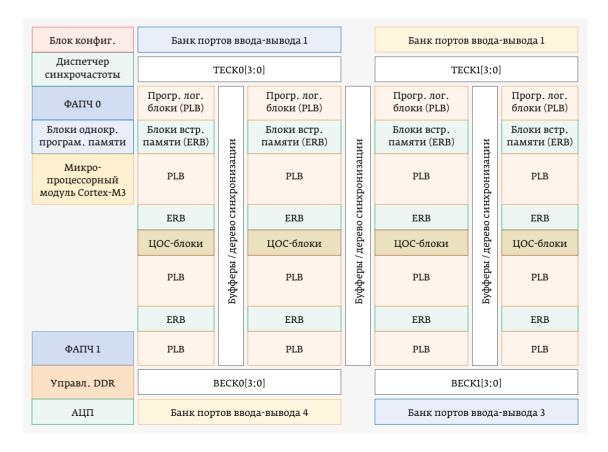

ПЛИС СНК серии Seal 5000, которые по производительности могут быть сравнимы с ПЛИС Xilinx серии Virtex-7, производятся по усовершенствованному 28-нм КМОП-процессу с медной металлизацией. Объем логических ресурсов Seal 5000 — от 30 до 326К, количество триггеров DFF — от 37 до 408К, емкость распределенной памяти — от 597 до 6520 Кбит (рис. 11). 128 бит распределенной памяти может быть сконфигурировано как 64-разрядный распределенный сдвиговый регистр. ПЛИС содержит до 500 пользовательских I/O. Высокопроизводительный программируемый логический блок (PLB) использует 6-LUT или два 5-LUT. Напряжение питания ядра ПЛИС 1,0 В (опционально 0,9 В). Максимальная рабочая

частота составляет 500 МГц. Размер блока встроенной памяти (ERB) составляет 18/36 Кбит, число блоков встроенной памяти от 63/32 до 1050/525, а общая емкость — до 18,9 Мбит. Число аппаратных ЦОС-блоков с размерностью операндов умножителя 18×18/25×18 составляет от 42/21 до 1312/656. Количество блоков ФАПЧ (PLL/DLL) от 2/4 до 13/20. В составе ПЛИС 12-разрядный АЦП с 300 Квыб/с. Аппаратное микропроцессорное ядро реализовано только в ПЛИС SA5-30E.

ПЛИС СНК серии Seal 5000 содержит от 4 до 8 каналов ввода-вывода I/O GTP (6,6 Гбит/с), от 4 до 16 каналов I/O GTH (13,1 Гбит/с), от 1 до 4 аппаратных ядер контроллера DDR2/3. В ПЛИС реализованы LVDS-интерфейс (до 1,6 Гбит/с), поддержка видеоинтерфейса со скоростью до 1,2 Гбит/с и универсальный интерфейс DDRx1/x2/x4/x8 (до 1,2 Гбит/с). Поддерживается обмен с памятью DDR1/2/3 и LPDDR1/2/3. В ПЛИС также интегрирован модуль PCI Express.

За безопасность отвечает блок AES-шифрования и сжатия битового потока, 256-битный ключ шифрования. Обеспечена совместимость со стандартом IEEE1149.1: граничное сканирование (BSCAN). Внутрисистемное программирование в соответствии со стандартом IEEE 1532.

На сайте www.uptops-dt.com предлагается САПР HqFpga-XIST V2.6.1 (2019), которая может быть использована для ПЛИС Xi'an Zhiduojing Microelectronics. Революционная особенность этой САПР заключается в том, что

Рис. 11. Архитектура ПЛИС СНК Seal 5000 (серия 30 K, без SerDes)

она предоставляет открытое и платформенное решение, то есть сторонние производители могут вести вторичную разработку на основе HqFpga и создавать собственные системы, что значительно упрощает процесс разработки ПО производителям ПЛИС. На сайте утверждается, что САПР HqFpga сопоставим с программной архитектурой Xilinx Vivado.

200 200 200

На сегодняшний день существует достаточно большой разрыв между ПЛИС китайских и ведущих мировых производителей по основным показателям: производительности, функциональным возможностям, энергопотреблению, программному обеспечению и поддержке приложений. ПЛИС китайских компаний в основном распространяются на рынке low-end-приложений. Большинство из них представляют собой устройства с логической емкостью до 10 млн вентилей. Однако разработано несколько серий ПЛИС СНК с числом логических вентилей до 20 млн. В приложениях с более высокими требованиями к производительности китайские ПЛИС пока не могут конкурировать с ПЛИС от Xilinx и Intel (Altera).

### **ЛИТЕРАТУРА**

- Domestic FPGA market structure and progress. https://programmersought.com/article/56525027465/.

- 2. What is the gap between domestic and foreign FPGA manufacturers? https://chowdera.com/2021/04/20210414195758577T.html.

- 3. Анализ отечественного рынка ПЛИС. Как выйти из игры. https://russianblogs.com/article/28011301584/.

- 4. Основные производители ПЛИС. https://russianblogs.com/article/26991047447/.

- 5. https://pangomicro.com/news/Cnew/detail323.html.

- 6. https://www.unisoc.com/en\_us/#/home/prodList?id=127998 5958166523906&pid=1338374479197306881&cdx=6&t=1.

- 7. http://www.gowinsemi.com.cn/.

- 8. https://github.com/AnlogicInfo/EF2M45-SOC.

- 9. https://aliexpress.ru/item/1005002178287075.html?sku\_id=12000018991079773.

- 10. https://phoenix-electronics.ru/news/28/62/plis-Antifuse-proizvodstva-knr-dlya-kosmicheskogo-primeneniya.html.

- 11. https://ru.wikipedia.org/wiki/China\_Electronics\_Technology\_ Group.

- 12. Design of an energetic particle radiation diagnostic spectroscopy system based on national core chips and Qt on Linux in EAST. Nuclear Science and Techniques, 2021, 32:68.— https://doi.org/10.1007/s41365-021-00906-x.

- 13. https://phoenix-electronics.ru/news/26/62/novoe-pokolenie-plis-proizvodstva-Fudan.html.

- 14. **Строгонов А., Кривчун М.** Исследование трассировочной способности архитектур индустриальных ПЛИС Xilinx с помощью программного инструмента RapidSmith2 // Компоненты и технологии. 2019. № 5. С. 90–94.

- 15. **Строгонов А., Кривчун М., Городков П.** Обзор программных средств с открытым исходным кодом для исследования современных архитектур ПЛИС Xilinx // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2020. № 1. С. 1–7.

- 16. **Строгонов А. В., Городков П. С.** ПЛИС компании Guangdong Gowin Semiconductor Corporation // Компоненты и технологии. 2020. № 1. С. 110–112.

- 17. http://www.isilicontek.com/page29.

### КНИГИ ИЗДАТЕЛЬСТВА «ТЕХНОСФЕРА»

Цена 920 руб.

# ПЛИС И ПАРАЛЛЕЛЬНЫЕ АРХИТЕКТУРЫ ДЛЯ ПРИМЕНЕНИЯ В АЭРОКОСМИЧЕСКОЙ ОБЛАСТИ. ПРОГРАММНЫЕ ОШИБКИ И ОТКАЗОУСТОЙЧИВОЕ ПРОЕКТИРОВАНИЕ

Под ред. Ф. Кастеншмидт, П. Реха

При поддержке АО «Конструкторско-технологический центр «ЭЛЕКТРОНИКА» Пер. с англ. и научная редакция С.А. Цыбина, к. т. н., АО «КТЦ «ЭЛЕКТРОНИКА», А.В. Быстрицкого, к. т. н., АО «КТЦ «ЭЛЕКТРОНИКА»,

А.В.Строгонова, д.т.н., ФГБОУ ВО «ВГТУ», П.С.Городкова, ФГБОУ ВО «ВГТУ»

В книге приводится понятие устранимых ошибок, возникающих в ПЛИС типа ППВМ (FPGA – Field Programmable Gate Array) и графических процессорах. Рассматриваются радиационные эффекты в ПЛИС, отказоустойчивые методы для ПЛИС, применение серийно выпускаемых ПЛИС в авиации и космонавтике, экспериментальные данные о воздействии радиации на ПЛИС, встроенные в ПЛИС процессоры под воздействием радиации и внесение ошибок в ПЛИС.

### КАК ЗАКАЗАТЬ НАШИ КНИГИ?

№ 125319, Москва, а/я 91; **\** +7 495 234-0110; 🖺 +7 495 956-3346; knigi@technosphera.ru, sales@technosphera.ru

M : TEXHOCOEPA

ISBN 978-5-94836-513-8

2019. – 326 c.,

ЙОШКАР-ОЛА, РЕСПУБЛИКА МАРИЙ ЭЛ

### АКЦИОНЕРНОЕ ОБЩЕСТВО «ЗАВОД ПОЛУПРОВОДНИКОВЫХ ПРИБОРОВ»

Металлокерамические корпуса

Нагревательные элементы

Контактные устройства

Графитовая оснастка

Оптоэлектронные корпуса

424003, Россия, Республика Марий Эл, г. Йошкар-Ола, ул. Суворова, 26

Ten.: +7-8362-45-70-09, 45-67-68. info@zpp12.ru marketing@zpp12.ru